Verilog_概述(精)

verilog的三种描述方式

Verilog的三种描述方式Verilog是一种硬件描述语言(HDL),用于描述数字电路和系统。

它是一种高级语言,允许工程师以更高层次的抽象来描述电路,从而简化了电路设计和验证过程。

Verilog有三种主要的描述方式,分别是结构描述、行为描述和数据流描述。

本文将详细介绍这三种描述方式,并分析它们的特点和适用场景。

1. 结构描述结构描述是Verilog的一种描述方式,它通过层次结构和模块之间的连接关系来描述电路。

在结构描述中,我们可以使用模块、端口、电路连接和实例化等概念来描述电路的组成和连接方式。

结构描述类似于画出电路图,只需要关注电路的结构和连接关系,而不需要考虑电路的具体功能。

结构描述的语法如下所示:module ModuleName (input wire A, input wire B, output wire C);// 输入端口定义// 输出端口定义// 内部信号定义// 子模块实例化// 逻辑实现endmodule结构描述的特点是清晰明了,易于理解和调试。

通过模块化的设计和层次结构,可以方便地对电路进行分析和调试。

结构描述适用于需要详细描述电路结构和连接关系的场景,比如设计一个复杂的处理器或系统。

2. 行为描述行为描述是Verilog的另一种描述方式,它通过描述电路的功能和行为来实现对电路的描述。

行为描述使用类似于编程语言的语法,可以使用条件语句、循环语句和顺序语句等来描述电路的行为。

在行为描述中,我们可以直接使用Verilog的语法来描述电路的逻辑功能,而不需要关注电路的结构和连接关系。

行为描述的语法如下所示:module ModuleName (input wire A, input wire B, output wire C);// 输入端口定义// 输出端口定义// 内部信号定义// 逻辑实现always @ (A or B) begin// 行为描述endendmodule行为描述的特点是灵活性高,可以方便地实现复杂的逻辑功能。

verilog教程

verilog教程Verilog是一种硬件描述语言(HDL),用于描述数字系统的行为和结构。

它是一种流行的HDL,广泛用于硬件设计和验证领域。

本教程将介绍Verilog的基本概念和语法,以帮助初学者入门。

一、Verilog的基本概念1.1 什么是VerilogVerilog是一种描述数字系统的语言,它可以用来描述硬件电路、验证设计的正确性以及进行电路仿真。

1.2 Verilog的应用领域Verilog广泛应用于硬件设计和验证领域,包括用于开发ASIC(应用特定集成电路)、FPGA(现场可编程门阵列)以及其他数字系统的设计。

1.3 Verilog的版本Verilog有多个版本,包括Verilog-1995、Verilog-2001以及最新的Verilog-2005、这些版本之间有一些语法和功能上的差异。

二、Verilog的语法结构2.1模块和端口在Verilog中,所有的电路描述都是由模块(module)组成的。

模块是电路的基本组成单元,可以看作是一个黑盒子,它接受一些输入,产生一些输出。

2.2信号声明在Verilog中,我们需要声明所有的输入和输出信号。

可以使用`input`和`output`关键字来声明这些信号。

2.3电路实现Verilog允许使用多种语句和结构来描述电路的行为和结构。

这些语句包括顺序语句、条件语句、循环语句以及层次结构。

2.4实例化模块在一个模块中,我们可以实例化其他的模块。

这样可以将一个大的电路拆分成多个小的模块,方便编写和测试。

三、Verilog的仿真和验证3.1静态验证Verilog语言本身提供了很多语法和语义层面的验证功能,对于语法和类型错误会有相应的提示。

3.2激励设计在进行电路验证时,我们需要为输入信号提供激励。

Verilog提供了一种称为`testbench`的特殊模块,用于生成输入信号并将其应用到待验证的电路中。

3.3波形仿真在Verilog中,我们可以使用仿真器来模拟电路的行为,并生成波形图来验证电路是否按预期工作。

verilog概述

verilog概述Verilog是一种硬件描述语言,用于描述数字电路和系统的行为和结构。

它被广泛应用于数字电路设计、集成电路验证、嵌入式系统开发等领域。

本文将从Verilog的基本语法、模块化设计、时序建模以及仿真和综合等方面进行概述。

Verilog的基本语法包括模块定义、端口声明、内部信号定义、赋值语句等。

模块是Verilog设计的基本单元,每个模块包含输入端口、输出端口和内部信号。

端口声明用于指定模块的输入输出接口,内部信号定义用于存储和传递模块内部的中间结果。

赋值语句用于对信号进行赋值,可以采用阻塞和非阻塞赋值两种方式。

Verilog的模块化设计是其重要特点之一。

通过将复杂的电路和系统划分为多个模块,可以提高设计的可读性和可维护性。

模块间的连接通过端口进行,可以通过实例化、连接和层次化等方式实现。

模块化设计可以大大提高设计的复用性和灵活性。

Verilog中的时序建模是对数字电路和系统中时序行为的描述。

通过使用时钟、时钟边沿和延迟等概念,可以准确地描述电路和系统中的时序关系。

时钟信号用于同步电路的操作,时钟边沿用于触发时序逻辑的运算,延迟用于模拟电路中的传播延迟。

仿真是Verilog设计中的重要环节,用于验证设计的正确性和功能。

通过编写测试文件和仿真脚本,可以对设计进行功能验证、时序验证和性能验证等。

仿真还可以用于验证设计的可靠性和容错性,对于复杂系统的设计尤为重要。

综合是将Verilog代码转换为可实现的硬件电路的过程。

通过综合工具,可以将Verilog代码转换为逻辑门、寄存器和连线等硬件元件的组合。

综合的结果可以用于后续的布局布线和物理设计,最终生成可用于生产的芯片。

Verilog是一种用于描述数字电路和系统的硬件描述语言。

通过Verilog的基本语法、模块化设计、时序建模、仿真和综合等技术,可以实现复杂的数字电路和系统设计。

Verilog的应用领域广泛,包括数字电路设计、集成电路验证和嵌入式系统开发等。

verilog instance 语句-概述说明以及解释

verilog instance 语句-概述说明以及解释1.引言1.1 概述Verilog是一种硬件描述语言,用于设计数字电路并进行硬件仿真。

在Verilog中,Instance语句被广泛应用于电路的模块化设计和组件重用。

它提供了一种简单而有效的方法,将已设计好的模块实例化为一个更大的电路系统。

Instance语句的概念类似于面向对象编程中的对象实例化,可以理解为在设计电路中创建了一个特定的实例。

通过使用Instance语句,可以将多个独立的模块连接在一起,形成一个完整的系统。

每个实例都具有自己的输入和输出端口,可以通过连接这些端口来实现数据的传输和处理。

使用Instance语句的一个主要优势是可以提高电路设计的可复用性。

通过将已验证和经过测试的模块实例化,可以减少重新设计和验证的工作量,同时确保了系统的稳定性和可靠性。

此外,Instance语句还提供了一种结构化编程的方式,使得电路设计更加清晰和易于维护。

然而,Instance语句也存在一些局限性。

首先,实例化的过程需要消耗一定的资源,包括时间和空间。

因此,在设计复杂的电路系统时,可能需要考虑资源的分配和优化。

其次,Instance语句只能在静态的编程环境中使用,在设计时需要提前确定系统的结构和连接方式,不适用于动态变化的场景。

尽管Instance语句在当前的硬件设计中已经得到了广泛应用,但它的未来发展仍然受到一些限制。

未来的发展方向可能包括提供更好的资源管理机制,以及支持动态配置和重构的能力。

同时,随着硬件设计的不断演进,Instance语句可能会与其他编程语言或工具进行更紧密的集成,以提高设计效率和灵活性。

综上所述,Verilog Instance语句是一种用于实例化模块并连接电路的重要概念。

它可以提供电路设计的可复用性和结构化编程的优势,但也存在一些局限性。

未来,我们可以期待Instance语句在硬件设计中的进一步发展和应用。

1.2 文章结构本篇文章主要围绕Verilog Instance语句展开论述。

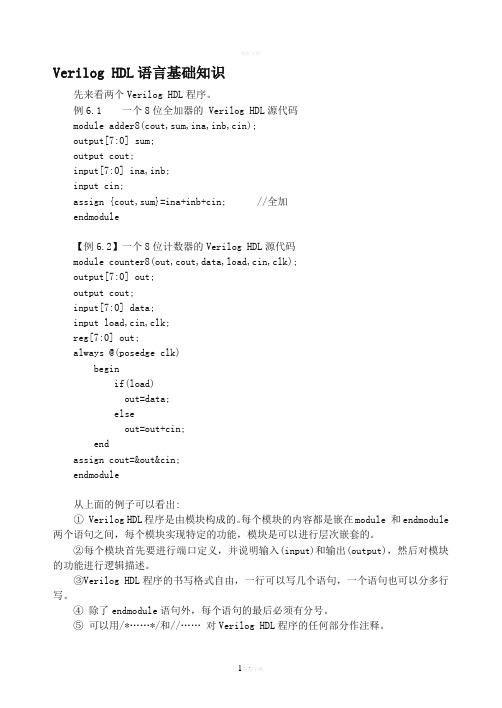

Verilog语言基础知识

在Verilog HDL中,用parameter来定义常量,即用parameter来定义一个标志符,代表一个常量,称为符号常量。其定义格式如下:

parameter 参数名1=表达式,参数名2=表达式,参数名3=表达式……;

例如:

parameter sel=8,code=8'ha3;

//分别定义参数sel为常数8(十进制),参数code为常数a3(十六进制)

Verilog HDL中共有19种数据类型。数据类型是用来表示数字电路中的数据存储和传送单元的。在此介绍4个最基本的数据类型:integer型、parameter型、reg型和wire型。

Verilog HDL中也有常量和变量之分,他们分属以上这些类型。

6.2.1 常量

在程序运行过程中,其值不能被改变的量称为常量。

assign {cout,sum}=ina+inb+cin;//全加

endmodule

【例6.2】一个8位计数器的Verilog HDL源代码

module counter8(out,cout,data,load,cin,clk);

output[7:0]out;

output cout;

input[7:0] data;

6.1.2 Verilog HDL模块的结构

Verilog HDL的基本设计单元是"模块(block)"。一个模块是由两部分组成的,一部分描述接口;另一部分描述逻辑功能,即定义输入是如何影响输出的。下面举例说明,图6.1示出了一个"与-或-非"门电路。

图6.1"与-或-非"电路

该电路表示的逻辑函数可以写为:

6.2.2 变量

verilog的三种描述方式

verilog的三种描述方式(最新版)目录1.引言2.Verilog 描述方式概述1.结构描述2.数据流描述3.行为描述4.混合描述3.结构描述1.门级结构描述2.模块级结构描述4.数据流描述1.逻辑关系2.持续赋值语句5.行为描述1.寄存器传输级描述2.状态机描述6.混合描述7.结论正文一、引言Verilog 是一种硬件描述语言,广泛应用于数字电路和模拟混合信号电路的设计验证。

在 Verilog 中,有多种描述方式可以实现逻辑功能,包括结构描述、数据流描述、行为描述和混合描述。

本文将对这些描述方式进行详细介绍。

二、Verilog 描述方式概述1.结构描述:通过调用逻辑原件,描述它们之间的连接来建立逻辑电路的 Verilog 模型。

这里的逻辑元件包括内置逻辑门、自主研发的已有模块、商业 IP 模块。

结构描述分为门级结构描述和模块级结构描述。

2.数据流描述:根据信号之间的逻辑关系,采用持续赋值语句描述逻辑电路的行为。

数据流描述关注信号的传输和处理过程,适用于组合逻辑电路的设计。

3.行为描述:通过描述电路的输入输出行为,以及电路内部状态的变化,来实现逻辑功能的描述。

行为描述主要包括寄存器传输级描述和状态机描述。

4.混合描述:结合结构描述、数据流描述和行为描述,实现对逻辑功能的全面描述。

混合描述可以充分利用 Verilog 的各种特性,提高描述的准确性和效率。

三、结构描述1.门级结构描述:通过实例化内置逻辑门或使用自定义模块,构建逻辑电路的结构。

例如,可以使用与门、或门、非门等逻辑门实现组合逻辑电路。

2.模块级结构描述:将具有一定功能的模块进行组合,形成复杂的逻辑电路。

模块可以是自主研发的已有模块,也可以是商业 IP 模块。

四、数据流描述1.逻辑关系:根据信号之间的逻辑关系,使用持续赋值语句进行描述。

例如,对于一个与非门,可以使用`assign #5 neg(a);`语句描述其输出信号与输入信号 a 的逻辑关系。

verilog语言简述

verilog语⾔简述verilog语⾔简述verilog是硬件描述语⾔,并不是单纯的“敲代码”。

C语⾔与Verilog的最⼤区别1. 互连:在硬件系统中,互连可以将实现模块间的连接,⽽C语⾔中并没有这样的变量。

Verilog的wire型变量配合⼀些驱动结构能有效地描述出⽹线地互连2. 并发:C语⾔天⽣是串⾏的,不能描述硬件之间的并发特性,C语⾔编译后,其机器指令在CPU的⾼速缓冲队列中基本是顺序执⾏的;⽽Verilog可以有效地描述并⾏地硬件系统。

3. 时间:运⾏C 程序时,没有⼀个严格的时间概念,程序运⾏时间的长短主要取决于处理器本⾝的性能;⽽Verilog 语⾔本⾝定义了绝对和相对的时间度量,在仿真时可以通过时间度量与周期关系描述信号之间的时间关系。

HDL语⾔的本质 Verilog 作为硬件描述语⾔,它的本质作⽤在于描述硬件。

Verilog 虽然采⽤了C 语⾔的形式,但是它的最终描述结果是芯⽚内部的实际电路。

所以评判⼀段HDL 代码优劣的最终标准是其描述并实现的硬件电路的性能(包括⾯积和速度两个⽅⾯ )。

使⽤HDL 语⾔可以从算法、系统级(System Level) 、功能模块级(Function Model Level) 、⾏为级(Behavior Level) 、寄存器传输级( RTL , Register Transfer Level) 、门级(Gate Level) 和开关级(Switch Level) 等不同层次描述数字电路系统,然后通过EDA ⼯具综合、仿真并实现该系统。

可以说HDL 语⾔的出现是数字系统设计⽅法的⼀个重⼤飞跃。

Verliog语⾔不能仅仅在⾏为级上实现,也就是功能实现;写verilog必须考虑到实际的实现,也就是要在寄存器传输级去思考,这⼀级是是⾏为级的更低⼀级,需要考虑时延,芯⽚⾯积,功耗等⽅⾯问题,也就是脑⼦⾥要先有电路,再有verilog。

也就是不仅仅在应⽤实现就⾏,需要更底层的思维。

Verilog语言详解

第三章 Cadence仿真器

学习内容

逻辑仿真算法 如何启动Verilog-XL和NC Verilog仿真器 如何显示波形

仿真算法

主要有三种仿真算法

基于时间的(SPICE仿真器) 基于事件的(Verilog-XL和NC Verilog仿真器) 基于周期的(cycle)

仿真算法

基于时间的算法用于处理连续的时间及变量

课程内容(三)

• 逻辑综合的介绍

– – – – – 简介 设计对象 静态时序分析 (STA) design analyzer环境 可综合的HDL编码风格

• 可综合的Verilog HDL

– Verilog HDL中的一些窍门 – Designware库 – 综合划分

•

实验 (1)

课程内容(四)

• 设计约束( Constraint)

Verilog HDL是在1983年由GDA(GateWay Design Automation)公司的Phil Moorby所创。Phi Moorby 后来成为Verilog-XL的主要设计者和Cadence公司的第一个合伙人。

在1984~1985年间,Moorby设计出了第一个Verilog-XL的仿真器。

Verilog还有一定的晶体管级描述能力及算法级描述能力

行为级和RTL级

MUX的行为可以描述为:只要信号a或b或sel发生变化,如果sel为0则选择a输出;否则选择 b输出。

module muxtwo (out, a, b, sel); input a, b, sel; output out; reg out; always @( sel or a or b) if (! sel) out = a; else out = b; endmodule

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Verilog HDL简介

Verilog是在C语言的基础上发展起来的一 种硬件描述语言 由Gateway Automation 于1983年首创, 并于1995年成为IEEE标准,即IEEE standard 1364。

3

Verilog HDL的特点

支持不同抽象层次的精确描述以及混合模拟,如 行为级、 RTL级、开关级等 设计、测试、模拟所用的语法都相同 较高层次的描述与具体工艺无关 提供了类似C语言的高级程序语句,如if-else, case,loop等 提供了算术、逻辑、位操作等运算符 包含完整的组合逻辑元件,如and、or、xor等, 无需自行定义 支持元件门级延时和元件门级驱动强度

6

Verilog HDL基础知识

基本词法定义

空白符 : 空格(space bar),TAB 键,return 键。 注释 (Comment) : “//”或“/*, */”。

7

/* 2-to-1 multiplexer; out = a when sel = 0;out = b when sel = 1; */ module MUX_2(out, a, b, sel); output out; input a, b, sel; //netlist not(sel_, sel); and(a1, a, sel_),(b1, b, sel); or(out, a1, a2); endmodule

13

EX2:

module \2:1MUX (out, a, b, sel); output out; input a, b, sel; not not1 (\~sel , sel); and and1 (a1, a \~sel ), and2 (b1, b, sel); or or1 (out, a1, a2); endmodule

EX: reg [8*17] stringvar; initial begin stringvar = “This is a string!”; //共17个字符 end

11

Verilog HDL基础知识

取名规则

标识符必须是由a-z, A-Z, 0-9,_, $这些字符 組成,最長只能到1024个字符 开头必须由a-z, A-Z或下划线_开头 可以在标识符所取的非法名称前加上反斜杠 “\”,并在名称结尾加上空白键,这样就可 以用任何可印出的ASCII字符来当作标识符 的名称了;而反斜杠和空白键不会被视为标 识符的一部分

12

EX1: module MUX_2(out, a, b, sel); output out; input a, b, sel; not U0(sel_, sel); and U1(a1, a, sel_), U2(b1, b, sel); or U3(out, a1, a2); endmodule

实数:

7.2 1.8e-4 9.5E6 //1.8*10-4

10

Verilog HDL基础知识

字符串与字符变量

字符串为两个双引号“ ”之间的字符,不许跨行 除普通的ASCII字符外,还支持通过前导的控制键 (\, %)引入一些特殊字符:如\n(换行),\t(TAB),

\\(代表\),\”(代表”),%%(代表%)

Verilog HDL与电子设计自动化

讲课:叶以正 李晓明 哈尔滨工业大学微电子中心

1

硬件描述语言

概念:为了描述硬件电路而专门设计的 一种语言。如VHDL、Verilog HDL等 抽象层次

系统级:C等高级语言描述 行为级:模块的功能描述 RTL级:寄存器与组合电路的合成 逻辑门级:基本逻辑门的组合 开关级:晶体管开关的组合

9

整数:

17 //位宽, 基数符号不写会采用default值 (32bit十进制) 8’d32 //8-bit十进制值为32 8’h12 8’h1A 8’b0001_1100 /* ”_”无特別意义,只是为了方便二进制数易读*/ 8’o37 32’bx // ”x”表unknown 4’b0??? // ”?”表High impedance

8

Verilog HDL基础知识

数字表示:整数,实数 整数:+/- <位宽> ‘<基数符号> <数值>

<位宽>:指定整数的大小,以bit为单位。 <基数符号>:指定整数的基数,可以是b(binary)二 进制;o(octal)八进制;d(decimal)十进制;h (hex-adecimal)十六进制。 <数值>:指定整数的值。

module module_name(Port_list) 端口声明; 数据类型声明; 电路描述; endmodule 例:上升沿D触发器 module dff_pos(data,clk,q); input data,clk; //端口声明 output q; //端口声明 reg q; //数据类型声明 always @(posedge clk) q=data;//电路描述 endmodule

14

Verilog HDL基础知识

关键词keywords

是指一些Verilog语言内部已经使用的词,主要是用 来定义语言的架构,并且所有的keyword都是用小 写表示,用户应避免使用 module, endmodule input, output, inout

reg, integer, real

4

Verilog HDL 概述

Verilog HDL的特点

Verilog框架结构 行为级描述和结构级描述(全加器为例) 开关级描述 测试系统组成 完整的测试文件

5

Verilog框架结构

※Verilog HDL是由module模块组成,模块定义关键词 module 开始,到关键词 endmodule结束,每条Verilog语句以分号 “;”作为结束(块语句、编译向导、endmodule等除外)。

not, and, or, xor, nor begin, nd

15

Verilog HDL基础知识

特殊字符: $,#,`

$:以$开头的标识符代表系统命令 $time:返回目前的仿真时间 $display:显示出信号的值 $stop:停止仿真