makefile语法规则

makefile正则表达式

makefile正则表达式makefile是一种常用的工具,可以用于自动化构建和管理项目。

在makefile中,正则表达式是一个强大的工具,可以帮助我们更方便地匹配和处理文本内容。

makefile中常用的正则表达式包括:1. ^(起始符):匹配字符串的开头。

2. $(结束符):匹配字符串的结尾。

3. .(点号):匹配除了换行符外的任意一个字符。

4. *(星号):匹配前面的字符出现0个或多个。

5. +(加号):匹配前面的字符出现1个或多个。

6. ?(问号):匹配前面的字符出现0个或1个。

7. [ ](中括号):匹配中括号中任意一个字符。

8. [^ ](中括号取反):匹配不在中括号中的任意一个字符。

9. ( )(圆括号):将括号中的内容视为一个整体,可以和其他正则表达式一起使用。

除了这些常用的正则表达式外,还有一些特殊的符号和语法可以帮助我们更精确地匹配文本内容,比如:1. (反斜杠):转义符,可以将特殊字符转义为普通字符。

2. |(竖线):或运算符,可以匹配多个表达式中的一个。

3. { }(花括号):重复次数符号,可以指定一个字符或表达式的重复次数。

在使用正则表达式时,我们需要注意一些事项,比如:1. 正则表达式是区分大小写的。

2. 正则表达式中的空格和换行符也会被匹配。

3. 正则表达式可能会匹配到我们不需要的内容,因此需要通过进一步筛选和处理来达到我们的目的。

总之,正则表达式在makefile中的应用非常广泛,可以帮助我们更方便地编写自动化构建和管理脚本。

熟练掌握正则表达式的使用方法,可以极大地提高我们的工作效率。

makefile后缀规则

makefile后缀规则在Makefile中,后缀规则(Suffix Rules)用于指定文件的依赖关系和生成规则。

它可以帮助我们避免重复编写相似的规则,提高Makefile的可读性和可维护性。

后缀规则的一般语法如下:```<target-pattern>: <stem-patterns> | <suffixes><commands>```其中:- `<target-pattern>`是目标文件的模式,通常使用`%`来表示一个或多个字符的通配符。

- `<stem-patterns>`是关联目标文件的模式,通常也使用`%`来表示相同的通配符。

它用于指定目标文件与依赖文件的对应关系。

- `<suffixes>`是一组文件后缀,用于表示输入文件的后缀。

- `<commands>`是生成目标文件的命令。

例如,假设我们有一组C源文件(.c文件),我们可以使用后缀规则来指定如何将它们编译为目标文件(.o文件):```makefile# 后缀规则%.o: %.cgcc -c $< -o $@```在上面的例子中,`%.o: %.c`表示目标文件的模式是以`.o`为后缀的文件,而依赖文件的模式是以`.c`为后缀的文件。

`$<`和`$@`分别表示第一个依赖文件和目标文件。

通过这个后缀规则,我们可以将所有的`.c`文件自动编译为对应的`.o`文件。

例如,当我们运行`make foo.o`时,Make会自动查找`foo.c`文件并执行对应的命令。

需要注意的是,后缀规则在GNU Make 4.0版本之后已经被淘汰,推荐使用模式规则(Pattern Rules)来代替。

模式规则更灵活且更易读,可读性更好。

因此,在编写新的Makefile时,建议使用模式规则来代替后缀规则。

Makefile 语法分析

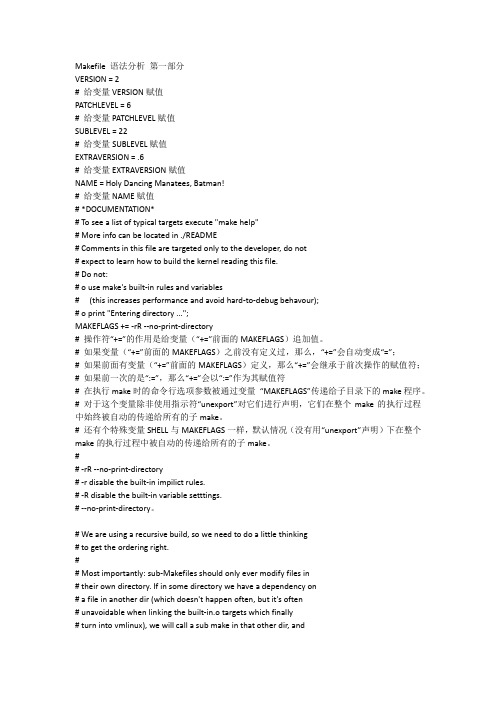

Makefile 语法分析第一部分VERSION = 2# 给变量VERSION赋值PATCHLEVEL = 6# 给变量PATCHLEVEL赋值SUBLEVEL = 22# 给变量SUBLEVEL赋值EXTRAVERSION = .6# 给变量EXTRAVERSION赋值NAME = Holy Dancing Manatees, Batman!# 给变量NAME赋值# *DOCUMENTATION*# To see a list of typical targets execute "make help"# More info can be located in ./README# Comments in this file are targeted only to the developer, do not# expect to learn how to build the kernel reading this file.# Do not:# o use make's built-in rules and variables# (this increases performance and avoid hard-to-debug behavour);# o print "Entering directory ...";MAKEFLAGS += -rR --no-print-directory# 操作符“+=”的作用是给变量(“+=”前面的MAKEFLAGS)追加值。

# 如果变量(“+=”前面的MAKEFLAGS)之前没有定义过,那么,“+=”会自动变成“=”;# 如果前面有变量(“+=”前面的MAKEFLAGS)定义,那么“+=”会继承于前次操作的赋值符;# 如果前一次的是“:=”,那么“+=”会以“:=”作为其赋值符# 在执行make时的命令行选项参数被通过变量“MAKEFLAGS”传递给子目录下的make程序。

makefile编写规则

makefile编写规则⼀、makefile 规则:⼀般开头都是 Tab ,不能空格, include 前⾯不能是 Tab; 1、如果没编译过,将所有的(.c)⽂件编译并且链接; 2、如果有其中的(.c)⽂件改变,编译并链接改变的⽂件; 3、如果(.h)⽂件被修改,编译引⽤相应的(.c)⽂件, 链接; 4、在随意修改时间的情况下,会导致编译过程中⽣成的(.o 中间⽂件)与可执⾏⽂件时间不⼀致,此时会编译相应的⽂件,并链接,最终编译成可执⾏⽂件;⼆、第⼀版 makefile: 例如有2个 .h ⽂件(utils.h, player.h, actor.h)和 3个 .c ⽂件( main.c, player.c, actor.c)需要编译链接:/*****main.c*********/#include "utils.h"#include "player.h"void main() {// do something}/*******player.c**********/#include "utils.h"#include "actor.h"bool create_player() {// do something}/****actor.c************/#include "utils.h"bool create_actor() {// do something}/********* makefile *****************/test : main.o actor.occ -o test main.o actor.omain.o : main.c utils.h player.h actor.hcc -c main.cpalyer.o: player.c player.h actor.h utils.hcc -c player.cactor.o: actor.h utils.hcc -c actor.cclean:rm test ain.o player.o actor.o 优点:可毒性很强,思路清晰明了; 缺点:⿇烦,重复的依赖过多,当需要编译⼤量⽂件时容易出错;第⼆版:利⽤ makefile 的变量;/********* makefile *****************/OBJ = main.o actor.o // 跟第⼀版⽐较,唯⼀的区别在这test : $(OBJ) // 这⼉cc -o test $(OBJ) // 这⼉main.o : main.c utils.h player.h actor.hcc -c main.cpalyer.o: player.c player.h actor.h utils.hcc -c player.cactor.o: actor.h utils.hcc -c actor.c .PHONY : clean // 伪⽬标,避免:如果当前⽬录下存在 clean rm 指令不执⾏clean:-rm test $(OBJ) // 前⾯的(-)表⽰,执⾏过程中不 care 出错;第三版:利⽤ GUN make 的⾃动推导规则 当 make 看到(.o )⽂件,他会⾃动把(.c)⽂件加上依赖关系,包括执⾏的语句(cc -c xx.c);/********* makefile *****************/OBJ = main.o actor.o // 跟第⼀版⽐较,唯⼀的区别在这test : $(OBJ) // 这⼉cc -o test $(OBJ) // 这⼉main.o : utils.h player.h actor.hpalyer.o: player.h actor.h utils.hactor.o: actor.h utils.h .PHONY : clean // 伪⽬标,避免:如果当前⽬录下存在 clean rm 指令不执⾏clean:-rm test $(OBJ)第四版:对第三版的整理(有⼀些重复的 .h) 公共的⼀起依赖,单独的单独依赖/********* makefile *****************/OBJ = main.o actor.o // 跟第⼀版⽐较,唯⼀的区别在这test : $(OBJ) // 这⼉cc -o test $(OBJ) // 这⼉$(OBJ) : utils.h actor.omain.o player.o .PHONY : clean // 伪⽬标,避免:如果当前⽬录下存在 clean rm 指令不执⾏clean:-rm test $(OBJ)优点:简洁缺点:不好理解以上的makefike⽂件的基本写法;或许你也发现了,如果有⼏百个源⽂件咋整呢,光是⽬录就要晕死,下⾯就是针对这种情况来说⼀下⼤型⼯程 makefile 的编写设计⼆、⼤型项⽬makefile编写: Makefile 同样也有像 c / c++ 类似的include功能; 例如我们有⼀堆 a.mk , b.mk以及 foo.make和⼀个变量 $(bar),其包含了 e.mk,f.mk, 那么 include foo.make *.mk $(bar) ------- 等价-------》 include foo.make a.mk b.mk e.mk f.mk。

makefile文件语法

makefile文件语法Makefile是一种用于自动化构建过程的工具,它使用一种特定的语法来定义构建规则和依赖关系。

下面是一些Makefile的基本语法规则:1. 目标(Target):目标是指要构建的程序或文件。

它通常以冒号(:)开头,后面跟着一个或多个依赖项(dependencies)。

```makefiletarget: dependenciescommands```2. 依赖项(Dependencies):依赖项是指要构建目标所必需的文件或目标。

在Makefile中,依赖项以空格分隔。

3. 命令(Commands):命令是指在构建目标时执行的命令行指令。

这些命令可以是编译、链接或其他任何必要的操作。

4. 变量(Variables):Makefile允许使用变量来存储值,以便在构建过程中重复使用。

变量以符号开头,后面跟着变量名。

```makefileVAR = value```5. 模式规则(Pattern Rules):模式规则允许根据文件模式匹配来构建目标。

它们使用通配符来匹配文件名,并在匹配的文件上执行相应的命令。

```makefiletargets : patterncommands```6. 条件语句(Conditionals):Makefile支持条件语句,可以根据条件执行不同的命令或规则。

条件使用ifdef、ifndef、ifeq等关键字定义。

7. 注释(Comments):Makefile使用井号()作为注释标记,任何在该符号之后的内容都会被视为注释,并被忽略。

8. 自动变量(Automatic Variables):Makefile提供了一些自动变量,可以在命令中使用,以获取有关目标、依赖项或文件名的信息。

例如,$表示当前目标,$<表示第一个依赖项等。

这些是Makefile的一些基本语法规则,但还有更多高级特性和用法,可以参考Make工具的文档或相关教程进行深入学习。

Makefile

MakefileMake的基本规则:Target [属性] 分隔符 [依赖文件] [;命令行 ]{Tab 命令行}注:命令行间可以加入任意多个空行,但空行也要以tab开头。

Cat –v -t -e Makefile会使Makefile文件中tab以^]显示,行尾以$显示。

注:命令过长,用\来连接多行成一行。

注释以#开头,如果#要用作字符符号,―#‖。

分隔符:::目标有多个规则。

哪条规则中的依赖文件比目标新,执行哪条规则。

如果多条规则的依赖文件都比目标新,多条规则都执行。

由于后面的规则可能覆盖前面规则的执行结构,所以规则顺序不同,执行结构也不同。

:^把本规则依赖文件和目标文件已有的依赖文件合起来,生成目标新的依赖文件列表。

:-清除目标已有依赖文件,把本规则依赖文件作为目标依赖文件列表。

:!对每个更新过的依赖文件都执行一次命令菜单。

:|内部规则专用。

如:file.o :file.cfile.o :^ filef.c现依赖文件为file.c filef.cfile.o :- filef.c现依赖文件为 filef.c令行属性:- 若本命令的执行错误,忽略掉,继续向下执行。

(不加该标志,make会停止)+ 始终执行本命令,即使make参数使用了-n-q-t。

(前提是本规则中依赖文件新与目标文件,命令行需要执行)@ 本命令行不在标准输出显示。

Target属性:指定多个目标文件属性:属性属性…… :目标目标……规则中指定单个目标属性:目标属性:[依赖文件] ……·IGNORE 类似与命令行属性-·SILENT 类似与命令行属性@·PRECIOUS 保留中间文件·LIBRARY 目标是一个库。

如果make发现目标是lib(member)或lib((entry))形式,会自动给名为lib的目标加上该属性。

·LIBRARYM 目标是库的一个成员。

如果make发现目标是lib(member)形式,会自动给lib目标加上·LIBRARY,被member目标加上·LIBRARYM。

makefile中if then写法

makefile中if then写法如何在Makefile 中使用if-then 写法Makefile 是一种软件构建工具,广泛用于管理和构建软件项目。

它使用一系列规则和命令来指导构建过程。

其中,条件语句if-then 是Makefile 中常用的控制语句之一。

在本文中,我们将逐步介绍如何在Makefile 中使用if-then 写法,以及它的用途和常见示例。

一、if-then 写法的基本语法在Makefile 中,if-then 语句的基本语法如下所示:ifeq (条件, 值)#条件为真时执行的命令else#条件为假时执行的命令endif在上述语法中,ifeq 是条件语句的关键字,用于判断一个条件是否为真。

条件是通过与指定的值进行比较来确定的。

若条件为真,则执行ifeq 和else 之间的命令块;若条件为假,则执行else 和endif 之间的命令块。

二、if-then 语句的使用场景if-then 语句在Makefile 中具有广泛的应用场景。

它可以用于实现以下功能:1. 根据不同的条件选择性地执行命令。

2. 根据环境变量的值选择性地执行命令。

3. 根据文件存在与否选择性地执行命令。

4. 根据命令执行结果选择性地执行不同的命令。

下面让我们逐步来看每个使用场景的示例。

三、根据不同的条件选择性地执行命令首先,我们来看一个根据不同的条件选择性地执行命令的示例。

假设我们有一个变量MODE,它的值可以是release 或debug。

根据MODE 的不同,我们可以选择性地执行不同的命令。

makefileMODE := releaseifeq ((MODE), release)# release 模式下执行的命令(info Building release version...)gcc -O3 -o myprogram main.celse# debug 模式下执行的命令(info Building debug version...)gcc -g -o myprogram main.cendif在上述示例中,(info ...) 是一个内置函数,用于在Makefile 执行过程中打印文本消息。

makefile文件语法规则

makefile文件语法规则Makefile文件的基本语法规则包括以下几点:1. 注释:以井号(#)开头的行被视为注释,不会被执行。

2. 规则:每条规则由一个目标文件和一组依赖文件组成,以及一个用于构建目标文件的命令。

规则的格式如下:Css:目标文件:依赖文件命令目标文件和依赖文件之间用冒号(:)分隔,命令部分指定了如何从依赖文件生成目标文件。

3. 变量:Makefile中可以使用变量来存储值,变量的值可以包含文本、空格、数字等。

变量名以美元符号($)开头,例如:Makefile:VAR = value命令= $VAR4. 函数:Makefile支持使用函数来执行更复杂的操作。

函数的语法如下:Scss:函数名(参数)Makefile中内置了一些常用的函数,如字符串操作函数、条件判断函数等。

也可以自定义函数。

5. 通配符:Makefile中可以使用通配符来匹配多个文件,常见的通配符有“*”和“?”。

例如,“*.c”表示匹配所有以“.c”结尾的文件,“a?b”表示匹配“ab”、“axb”、“ayb”等字符串。

6. 回声:在Makefile中,命令前面加上“@”符号可以关闭回声,即不会在执行命令时显示该命令。

例如:Makefile:@echo Hello, world!这条命令执行时不会输出“Hello, world!”的文本。

7. 模式规则:Makefile中的模式规则允许根据一组通配符匹配的文件来定义规则,格式如下:Makefile:模式:目标文件命令1命令2模式匹配的文件将按照指定的命令构建目标文件。

makefile循环语句

makefile循环语句(原创版)目录1.Makefile 简介2.Makefile 循环语句的作用3.Makefile 循环语句的语法4.Makefile 循环语句的示例5.Makefile 循环语句的注意事项正文1.Makefile 简介Makefile 是一种构建脚本,用于自动构建和编译源代码。

它最初用于 Unix 系统,但现在已经广泛应用于各种操作系统,如 Linux、macOS 等。

Makefile 可以根据源代码的变化自动重新编译目标文件,从而提高了开发效率。

2.Makefile 循环语句的作用在 Makefile 中,循环语句用于处理一系列相似的任务。

通过使用循环语句,可以避免重复编写相同的代码,使 Makefile 更加简洁和易于维护。

3.Makefile 循环语句的语法Makefile 循环语句的基本语法如下:```循环名:for 变量名 in 列表; do# 循环体内容done```其中,循环名是一个标识符,用于表示循环的开始和结束。

变量名是要迭代的变量,列表是一个包含多个元素的列表,用空格分隔。

循环体内容是循环执行的任务。

4.Makefile 循环语句的示例以下是一个 Makefile 循环语句的示例:```all:for src in src1 src2 src3; doobj := $(src).o$(CC) $(CFLAGS) -c $src -o $objdone```在这个示例中,循环名为“all”,变量名为“src”,列表为“src1 src2 src3”。

循环体内容是使用 C 编译器编译源代码文件并生成目标文件。

5.Makefile 循环语句的注意事项在使用 Makefile 循环语句时,需要注意以下几点:- 循环名应该具有唯一性,避免重复定义。

- 列表中的元素应该使用空格分隔,而不是逗号或其他分隔符。

- 在循环体内,可以使用自动变量(如$@、$%等)来表示当前迭代的变量。

makefile 中文手册 第四章 _ Makefile的规则

第四章:Makefile的规则本章我们将讨论Makefile的一个重要内容,规则。

熟悉规则对于书写Makefile至关重要。

Makefile中,规则描述了在何种情况下使用什么命令来重建一个特定的文件,此文件被称为规则“目标”(通常规则中的目标只有一个)。

规则中出目标之外的罗列的其它文件称为“目标”的依赖,而规则的命令是用来更新或者创建此规则的目标。

除了makefile的“终极目标”所在的规则以外,其它规则的顺序在makefile文件中没有意义。

“终极目标”就是当没有使用make 命令行指定具体目标时,make默认的更新的哪一个目标。

它是makefile文件中第一个规则的目标。

如果在makefile中第一个规则有多个目标的话,那么多个目标中的第一个将会被作为make的“终极目标”。

有两种情况的例外:1. 目标名以点号“.”开始的并且其后不存在斜线“/”(“./”被认为是当前目录;“../”被认为是上一级目录);2. 模式规则的目标。

当这两种目标所在的规则是Makefile的第一个规则时,它们并不会被作为“终极目标”。

“终极目标”是执行make的唯一目的,其所在的规则作为第一个被执行的规则。

而其它的规则是在完成重建“终极目标”的过程中被连带出来的。

所以这些目标所在规则在Makefile中的顺序无关紧要。

因此,我们书写的makefile的第一个规则应该就是重建整个程序或者多个程序的依赖关系和执行命令的描述。

4.1 一个例子我们来看一个规则的例子:foo.o : foo.c defs.h # module for twiddling the frobscc -c -g foo.c这是一个典型的规则。

看到这个例子,大家应该能够说出这个规则的各个部分之间的关系。

不过我们还是要把这个例子拿出来讨论。

目的是让我们更加明确地理解Makefile的规则。

本例第一行中,文件“foo.o”是规则需要重建的文件,而“foo.c”和“defs.h”是重建“foo.o”所要使用的文件。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

clean: @rm -vf main.o test

使 用:定义依赖关系;依赖的下行是要执行的编译或连接命令,必须以TAB开头;在 clean其冒号后什么也没有,那么,make 就不会自动去找文件的依赖性,也就不会自动 执行其后所定义的命令。要执行其后的命令,就要在 make 命令后明显得指出这个 lable 的名字。这样的方法非常有用,我们可以在一个 makefile 中定义不用的编译或 是和编译无关的命令,比如程序的打包,程序的备份,等等。 在默认的方式下,也就是我们只输入 make 命令。那么, 1、make 会在当前目录下找名字叫“Makefile”或“makefile”的文件。 2、如果找到,它会找文件中的第一个目标文件(target),在上面的例子中,他会找 到“test”这个文件,并把这个文件作为最终的目标文件。 3、如果 test文件不存在,或是 test所依赖的后面的 .o 文件的文件修改时间要比 test这个文件新,那么,他就会执行后面所定义的命令来生成 test这个文件。 4、如果 test所依赖的.o 文件也存在,那么 make 会在当前文件中找目标为.o 文件的 依赖性,如果找到则再根据那一个规则生成.o 文件。(这有点像一个堆栈的过程) 5、当然,你的 C 文件和 H 文件是存在的啦,于是 make 会生成 .o 文件,然后再 用 .o 文件生命 make 的终极任务,也就是执行文件 edit 了。

makefile简介

2012年11月1日 16:08

一、Makefile 的规则 target ... : prerequisites ...

command ….. target 是目标文件,prerequisites 依赖文件,command 也就是 make 需要执行的命令

test:main.o gcc -o test main.o

这 就是整个 make 的依赖性,make 会一层又一层地去找文件的依赖关系,直到最终编 译出第一个目标文件。在找寻的过程中,如果出现错误,比如最后被依赖的文件找不 到,那么 make 就会直接退出,并报错,而对于所定义的命令的错误,或是编译不成 功,make 根本不理。make 只管文件的依赖性,即,如果在我找了依赖关系之后,冒号 后面的文件还是不在,那么对不起,我就不工作啦。

分区 makefile 的第 3 页

路径的自动Leabharlann 索2012年11月1日 16:16

在一些大的工程中,有大量的源文件,我们通常的做法是把这许多的源文件分 类,并存放在不同的目录中。所以,当 make 需要去找寻文件的依赖关系时,你 可以在文件前加上路径,但最好的方法是把一个路径告诉 make,让 make 在自动 去找。Makefile 文件中的特殊变量“VPATH”就是完成这个功能的,如果没有指 明这个变量,make 只会在当前的目录中去找寻依赖文件和目标文件。如果定义了 这个变量,那么,make 就会在当当前目录找不到的情况下,到所指定的目录中去 找寻文件了。 VPATH = src:../headers 上面的的定义指定两个目录,“src”和“../headers”,make 会按照这个顺序 进行搜索。目录由“冒号”分隔。(当然,当前目录永远是最高优先搜索的地 方)

通配符代替了你一系列的文件,如“*.c”表示所以后缀为 c 的文件。一个需要我 们注意的是,如果我们的文件名中有通配符,如:“*”,那么可以用转义字符 “\”,如“\*”来表示真实的“*”字符,而不是任意长度的字符串。好吧,还是 先来看几个例子吧: clean: rm -f *.o 上面这个例子我不不多说了,这是操作系统 Shell 所支持的通配符。这是在命令中 的通配符。 print: *.c lpr -p $? touch print 上面这个例子说明了通配符也可以在我们的规则中,目标 print 依赖于所有的[.c] 文件。其中的“$?”是一个自动化变量,表示被修改的文件。 objects = *.o 上面这个例子,表示了,通符同样可以用在变量中。并不是说[*.o]会展开,不! objects的值就是“*.o”。Makefile 中的变量其实就是 C/C++中的宏。如果你要让 通配符在变量中展开,也就是让 objects 的值是所有[.o]的文件名的集合,那么, 你可以这样:objects := $(wildcard *.o),这种用法由关键字“wildcard”指 出。

“.PHONY”来显示地指明一个目标是“伪目标”,向 make 说明,不管是 否有这个文件,这个目标就是“伪目标”。只要有这个声明,不管是否有 “clean”文件,要运行“clean”这个目标,只有“makeclean”这样。于是整 个过程可以这样写:

.PHONY: clean clean: rm *.o temp

分区 makefile 的第 1 页

makefile详述

2012年11月1日 16:13

Makefile 里主要包含了五个东西:显式规则、隐晦规则、变量定义、文件指示和注释。

1、显式规则。显式规则说明了,如何生成一个或多的个目标文件。这是由 Makefile 的书写 者明显指出,要生成的文件,文件的依赖文件,生成的命令。

分区 makefile 的第 6 页

使用函数

2012年11月1日 16:17

函数调用,很像变量的使用,也是以“$”来标识的,其语法如下: $(<function> <arguments> ) 或是 ${<function> <arguments>} 这 里,<function>就是函数名,make 支持的函数不多。<arguments>是函数的参数,参数间 以逗号“,”分隔,而函数名和参数之间以“空格”分隔。函数调用以“$”开头, 以圆括号 或花括号把函数名和参数括起。感觉很像一个变量,是不是?函数中的参数可以使用变量, 为了风格的统一,函数和变量的括号最好一样,如使用 “$(subst a,b,$(x))”这样的形 式,而不是“$(subst a,b,${x})”的形式。因为统一会更清楚,也会减少一些不必要的麻 烦。 还是来看一个示例: comma:= , empty:= space:= $(empty) foo:= a b c bar:= $(subst $(space),$(comma),$(foo)) 在 这个示例中,$(comma)的值是一个逗号。$(space)使用了$(empty)定义了一个空 格,$(foo)的值是“a b c”,$(bar)的定义用,调用了函数“subst”,这是一个替换函 数,这个函数有三个参数,第一个参数是被替换字串,第二个参数是替换字串,第三个 参数 是替换操作作用的字串。这个函数也就是把$(foo)中的空格替换成逗号,所以$(bar)的值是 “a,b,c”。 $(subst <from>,<to>,<text> ) 名称:字符串替换函数——subst。 功能:把字串<text>中的<from>字符串替换成<to>。 返回:函数返回被替换过后的字符串。

分区 makefile 的第 5 页

定义命令包

2012年11月1日 16:16

如果 Makefile 中出现一些相同命令序列,那么我们可以为这些相同的命令序 列定义一个变量。定义这种命令序列的语法以“define”开始,以“endef”结 束,如:

define run-yacc yacc $(firstword $^) mv y.tab.c $@ endef 这里,“run-yacc”是这个命令包的名字,其不要和 Makefile 中的变量重 名。在“define”和“endef”中的两行就是命令序列。这个命令包中的第一个 命令是运行 Yacc 程序,因为Yacc 程序总是生成“y.tab.c”的文件,所以第 二行的命令就是把这个文件改改名字。还是把这个命令包放到一个示例中来看 看吧。 foo.c : foo.y $(run-yacc) 我们可以看见,要使用这个命令包,我们就好像使用变量一样。在这个命令包 的使用中,命令包“run-yacc”中的“$^”就是“foo.y”,“$@”就 是 “foo.c”(有关这种以“$”开头的特殊变量,我们会在后面介绍),make 在 执行命令包时,命令包中的每个命令会被依次独立执行。

5、注释。Makefile 中只有行注释,和 UNIX 的 Shell 脚本一样,其注释是用“#”字符, 这个就像 C/C++中的“//”一样。如果你要在你的 Makefile 中使用“#”字符,可以用反斜 框进行转义,如:“\#”。

最后,还值得一提的是,在 Makefile 中的命令,必须要以[Tab]键开始。 这样,make的执行过程如下: 1、读入所有的 Makefile。 2、读入被 include 的其它 Makefile。 3、初始化文件中的变量。 4、推导隐晦规则,并分析所有规则。 5、为所有的目标文件创建依赖关系链。 6、根据依赖关系,决定哪些目标要重新生成。 7、执行生成命令。

分区 makefile 的第 4 页

伪目标

2012年11月1日 16:16

我们提到过一个“clean”的目标,这是一个“伪目标”,clean: 正像我们前面例子中的“clean”一样,即然我们生成了许多文件编译文件,我 们也应该提供一个清除它们的“目标”以备完整地重编译而用。 (以“make clean”来使用该目标) 因为,我们并不生成“clean”这个文件。“伪目标”并不是一个文件,只是一 个标签,由于“伪目标”不是文件,所以 make 无法生成它的依赖关系和决定 它是否要执行。我们只有通过显示地指明这个“目标”才能让其生效。当然, “伪目标”的取名不能和文件名重名,不然其就失去了 “伪目标”的意义了。 当然,为了避免和文件重名的这种情况,我们可以使用一个特殊的标记