电子科大罗萍模拟集成电路期末试题3

模拟集成电路设计期末试卷..【范本模板】

《模拟集成电路设计原理》期末考试一.填空题(每空1分,共14分)1、与其它类型的晶体管相比,MOS器件的尺寸很容易按____比例____缩小,CMOS电路被证明具有_较低__的制造成本。

2、放大应用时,通常使MOS管工作在_ 饱和_区,电流受栅源过驱动电压控制,我们定义_跨导_来表示电压转换电流的能力。

3、λ为沟长调制效应系数,对于较长的沟道,λ值____较小___(较大、较小).4、源跟随器主要应用是起到___电压缓冲器___的作用。

5、共源共栅放大器结构的一个重要特性就是_输出阻抗_很高,因此可以做成___恒定电流源_。

6、由于_尾电流源输出阻抗为有限值_或_电路不完全对称_等因素,共模输入电平的变化会引起差动输出的改变.7、理想情况下,_电流镜_结构可以精确地复制电流而不受工艺和温度的影响,实际应用中,为了抑制沟长调制效应带来的误差,可以进一步将其改进为__共源共栅电流镜__结构.8、为方便求解,在一定条件下可用___极点—结点关联_法估算系统的极点频率。

9、与差动对结合使用的有源电流镜结构如下图所示,电路的输入电容C in为__ C F(1-A)__。

10、λ为沟长调制效应系数,λ值与沟道长度成___反比__(正比、反比).二.名词解释(每题3分,共15分)1、阱解:在CMOS工艺中,PMOS管与NMOS管必须做在同一衬底上,其中某一类器件要做在一个“局部衬底”上,这块与衬底掺杂类型相反的“局部衬底”叫做阱.2、亚阈值导电效应解:实际上,V GS=V TH时,一个“弱”的反型层仍然存在,并有一些源漏电流,甚至当V GS<V TH时,I D也并非是无限小,而是与V GS呈指数关系,这种效应叫亚阈值导电效应。

3、沟道长度调制解:当栅与漏之间的电压增大时,实际的反型沟道长度逐渐减小,也就是说,L 实际上是V DS 的函数,这种效应称为沟道长度调制.4、等效跨导Gm 解:对于某种具体的电路结构,定义inD V I ∂∂为电路的等效跨导,来表示输入电压转换成输出电流的能力 5、米勒定理解:如果将图(a)的电路转换成图(b )的电路,则Z 1=Z/(1-A V ),Z 2=Z/(1—A V —1),其中A V =V Y /V X 。

电子科技大学《模拟电路基础》期末考试

………密………封………线………以………内………答………题………无………效……电子科技大学2010-2011学年第二学期期末考试A 卷课程名称:模拟电路基础考试形式:开卷考试日期:20 11年 6月30日考试时长:_120分钟 课程成绩构成:平时20%,期中20%,实验0%,期末60% 本试卷试题由_六_部分构成,共_4_页。

一、单项选择题(共14分,共7题,每题2分)1、晶体管工作在放大区时,电压偏置为()。

A. 发射结正偏、集电结正偏B. 发射结正偏、集电结反偏C. 发射结反偏、集电结正偏D. 发射结反偏、集电结反偏2、放大电路在负载开路时输出电压为4V ,接入Ωk 3的负载电阻后输出电压降为3V ,放大电路的输出电阻o R =()。

A. Ωk 10B.Ωk 2C.Ωk 1D.Ωk 5.03、差分放大电路的共模抑制比CMR K 越大,表明电路的()。

A.放大倍数越稳定B. 放大倍数越大 C.放大倍数越小D. 抑制零漂的能力越强4、多级放大电路由两个参数相同的单级放大电路组成,在组成它的单级放大电路的截止频率处,幅值下降了()。

A. 3dBB. 6dBC. 20dBD. 40dB5、负反馈放大电路以降低电路的()为代价来提高电路的其他性能指标。

A. 通频带宽B. 放大倍数C. 输入电阻D.输出电阻6、当要求输入电阻大,输出电阻小时,应选用负反馈放大电路的反馈类型为()。

A. 电压串联负反馈B.电流串联负反馈 C.电压并联负反馈D.电流并联负反馈………密………封………线………以………内………答………题………无………效……7、( )不是使乙类互补推挽电路转换效率达到%5.78的假设条件。

A. 忽略饱和电压B. 静态工作点处于负载线中点 C. 合适的偏置电压D. 输入满激励 二、填空题(共26分,共13空,每空2分)1、NPN 管共射放大电路在测试时出现电压削顶,这是失真,要消除该失真,应将静态工作电流。

电子科技大学“机械设计制造及其自动化”《模拟电路基础》23秋期末试题库含答案

电子科技大学“机械设计制造及其自动化”《模拟电路基础》23秋期末试题库含答案第1卷一.综合考核(共20题)1.三极管的击穿电流ICEO是()。

A.基极开路时的集电极电流B.发射极开路时的集电极电流C.基极短路时的集电极电流D.发射极短路时的集电极电流2.差动放大电路依靠电路的对称性以及共模负反馈来抑制零点漂移。

()A.正确B.错误3.为了稳定静态工作点,应在放大电路中引入()。

A.电流负反馈B.电压负反馈C.直流负反馈D.交流负反馈4.电流求和负反馈使输人电阻减少;电压求和负反馈使输人电阻()。

A.增加B.不变C.减少5.6.功率放大器的效率是()。

A.平均输出功率与平均输入功率之比B.平均输出功率与晶体管平均消耗的功率比C.最大不失真平均输出功率与电源提供的平均功率总功率之比D.晶体管上平均消耗的功率与电源提供的平均功率总功率之比8.向放大器输入正弦电压。

当输出是非正弦的周期电压时,该放大器一定产生了()。

A.频率失真B.相位失真C.削波失真D.非线性失真9.在热激发条件下,少数价电子获得足够激发能,进入导带,产生()。

A.负离子B.空穴C.正离子D.电子-空六对10.要求得到一个由电流控制的电流源,应引入()负反馈。

A.电压串联B.电压并联C.电流串联D.电流并联11.半导体中的载流子为()。

A.电子B.空穴C.正离子D.电子和空穴12.产生零点漂移的原因主要是晶体管参数受温度的影响。

()A.正确B.错误13.在绝对零度时,本征半导体中()载流子。

A.有B.没有C.少数D.多数14.N沟道结型场效应管的夹断电压VP为()。

A.正值B.负值C.零15.差分放大电路端输出时,主要靠电路的对称性来抑制温漂。

()A.错误B.正确16.反馈放大电路由()电路和()网络组成。

A.基本放大B.反馈C.正反馈D.负反馈17.18.集成运放中间级的作用是()。

A.提高输人电阻B.提高共模抑制比C.提高放大倍数19.20.为了抑制直流放大器的温漂输出,应该采用()。

电子科大模电期末真题09~10

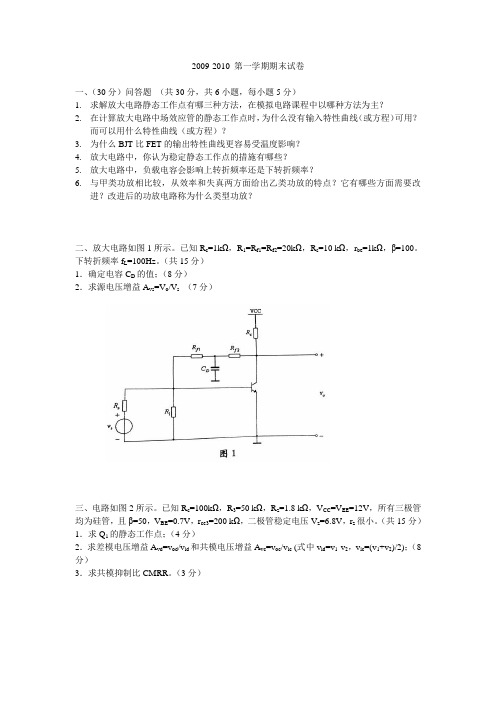

2009-2010 第一学期期末试卷一、(30分)问答题(共30分,共6小题,每小题5分)1.求解放大电路静态工作点有哪三种方法,在模拟电路课程中以哪种方法为主?2.在计算放大电路中场效应管的静态工作点时,为什么没有输入特性曲线(或方程)可用?而可以用什么特性曲线(或方程)?3.为什么BJT比FET的输出特性曲线更容易受温度影响?4.放大电路中,你认为稳定静态工作点的措施有哪些?5.放大电路中,负载电容会影响上转折频率还是下转折频率?6.与甲类功放相比较,从效率和失真两方面给出乙类功放的特点?它有哪些方面需要改进?改进后的功放电路称为什么类型功放?二、放大电路如图1所示。

已知R c=1kΩ,R1=R f1=R f2=20kΩ,R s=10 kΩ,r be=1kΩ,β=100。

下转折频率f L=100Hz。

(共15分)1.确定电容C D的值;(8分)2.求源电压增益A vs=V o/V s(7分)三、电路如图2所示。

已知R c=100kΩ,R3=50 kΩ,R z=1.8 kΩ,V CC=V EE=12V,所有三极管均为硅管,且β=50,V BE=0.7V,r ce3=200 kΩ,二极管稳定电压V z=6.8V,r z很小。

(共15分)1.求Q1的静态工作点;(4分)2.求差模电压增益A vd=v od/v id和共模电压增益A vc=v oc/v ic (式中v id=v1-v2,v ic=(v1+v2)/2);(8分)3.求共模抑制比CMRR。

(3分)四、负反馈放大器如图3所示。

已知β=50,r be=1 kΩ。

(共25分)1.判断交流反馈类型;(3分)2.画出A电路和B电路;(5分)3.求基本放大器的增益A和反馈系数B;(8分)4.计算输入电阻R in和输出电阻R out;(4分)5.计算闭环源电压增益A vsf=v o/v s;(3分)6.若假定该负反馈为深度负反馈,估算闭环源电压增益A vsf=v o/v s。

集成电路设计原理试卷及答案解读

电科《集成电路原理》期末考试试卷一、填空题1.(1分) 年,第一次观测到了具有放大作用的晶体管。

2.(2分)摩尔定律是指 。

3.集成电路按工作原理来分可分为 、 、 。

4.(4分)光刻的工艺过程有底膜处理、涂胶、前烘、 、 、 、 和去胶。

5.(4分)MOSFET可以分为 、 、 、 四种基本类型。

6.(3分)影响MOSFET 阈值电压的因素有: 、 以及 。

7.(2分)在CMOS 反相器中,V in ,V out 分别作为PMOS 和NMOS 的 和 ; 作为PMOS 的源极和体端, 作为NMOS 的源极和体端。

8.(2分)CMOS 逻辑电路的功耗可以分为 和 。

9.(3分)下图的传输门阵列中5DD V V =,各管的阈值电压1T V V =,电路中各节点的初始电压为0,如果不考虑衬偏效应,则各输出节点的输出电压Y 1= V ,Y 2= V ,Y 3= V 。

DD 13210.(6分)写出下列电路输出信号的逻辑表达式:Y 1= ;Y 2= ;Y 3= 。

AB Y 1AB23二、画图题:(共12分)=+的电路图,要求使用的1.(6分)画出由静态CMOS电路实现逻辑关系Y ABD CDMOS管最少。

2.(6分)用动态电路级联实现逻辑功能Y ABC=,画出其相应的电路图。

三、简答题:(每小题5分,共20分)1.简单说明n阱CMOS的制作工艺流程,n阱的作用是什么?2.场区氧化的作用是什么,采用LOCOS工艺有什么缺点,更好的隔离方法是什么?3.简述静态CMOS 电路的优点。

4.简述动态电路的优点和存在的问题。

四、分析设计题:(共38分1.(12分)考虑标准0.13m μ CMOS 工艺下NMOS 管,宽长比为W/L=0.26/0.13m m μμ,栅氧厚度为2.6ox t nm =,室温下电子迁移率2220/n cm V s μ=,阈值电压T V =0.3V,计算 1.0GS V =V 、0.3DS V =V 和0.9V 时D I 的大小。

电子科技大学模拟电路考试题及答案

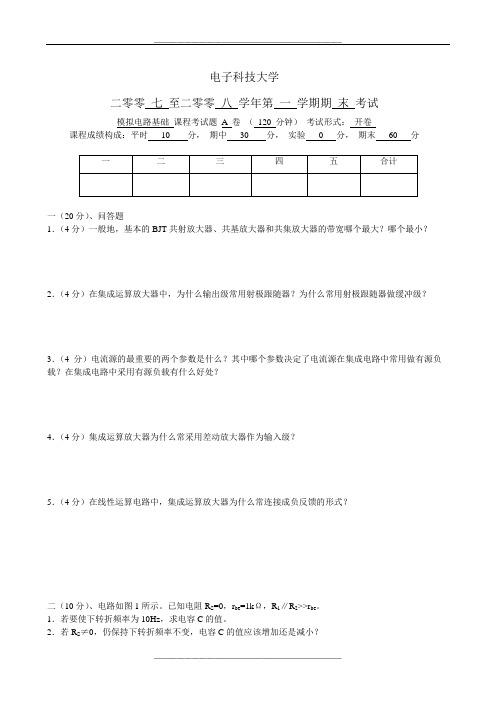

电子科技大学二零零七至二零零八学年第一学期期末考试模拟电路基础课程考试题A 卷(120 分钟)考试形式:开卷课程成绩构成:平时10 分,期中30 分,实验0 分,期末60 分一(20分)、问答题1.(4分)一般地,基本的BJT共射放大器、共基放大器和共集放大器的带宽哪个最大?哪个最小?2.(4分)在集成运算放大器中,为什么输出级常用射极跟随器?为什么常用射极跟随器做缓冲级?3.(4分)电流源的最重要的两个参数是什么?其中哪个参数决定了电流源在集成电路中常用做有源负载?在集成电路中采用有源负载有什么好处?4.(4分)集成运算放大器为什么常采用差动放大器作为输入级?5.(4分)在线性运算电路中,集成运算放大器为什么常连接成负反馈的形式?二(10分)、电路如图1所示。

已知电阻R S=0,r be=1kΩ,R1∥R2>>r be。

1.若要使下转折频率为10Hz,求电容C的值。

2.若R S≠0,仍保持下转折频率不变,电容C的值应该增加还是减小?图1三(10分)、电路如图2所示。

已知差模电压增益为10。

A点电压V A=-4V,硅三极管Q1和Q2的集电极电压V C1=V C2=6V,R C=10 kΩ。

求电阻R E和R G。

图2四(10分)、电路如图3所示。

已知三极管的β=50,r be=1.1kΩ,R1=150kΩ,R2=47kΩ,R3=10kΩ,R4=47k Ω,R5=33kΩ,R6=4.7kΩ,R7=4.7kΩ,R8=100Ω。

1.判断反馈类型;2.画出A电路和B电路;3.求反馈系数B;4.若A电路的电压增益A v=835,计算A vf,R of和R if。

图3五(10分)、试导出图4所示电路的输出电压v o与输入电压v i之间的关系。

已知R1=1MΩ,R2=4MΩ,R3=1/3MΩ,R4= R5= R6=1MΩ,C1=C2=1μF。

图4参考答案及评分标准一(20分)、问答题1.(4分)一般地,基本的BJT共射放大器的带宽最小(2分),共集放大器的带宽最大(2分)。

电子科大2012模电期末试卷

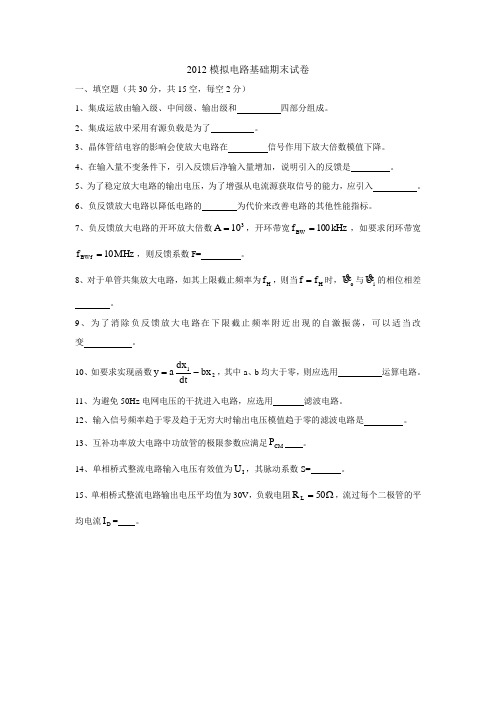

2012模拟电路基础期末试卷一、填空题(共30分,共15空,每空2分)1、集成运放由输入级、中间级、输出级和 四部分组成。

2、集成运放中采用有源负载是为了 。

3、晶体管结电容的影响会使放大电路在 信号作用下放大倍数模值下降。

4、在输入量不变条件下,引入反馈后净输入量增加,说明引入的反馈是 。

5、为了稳定放大电路的输出电压,为了增强从电流源获取信号的能力,应引入 。

6、负反馈放大电路以降低电路的 为代价来改善电路的其他性能指标。

7、负反馈放大电路的开环放大倍数310A =,开环带宽kHz 100f BW =,如要求闭环带宽MHz 10f BWf =,则反馈系数F= 。

8、对于单管共集放大电路,如其上限截止频率为H f ,则当H f f =时,oU 与i U 的相位相差 。

9、为了消除负反馈放大电路在下限截止频率附近出现的自激振荡,可以适当改变 。

10、如要求实现函数21bx dtdx ay -=,其中a 、b 均大于零,则应选用 运算电路。

11、为避免50Hz 电网电压的干扰进入电路,应选用 滤波电路。

12、输入信号频率趋于零及趋于无穷大时输出电压模值趋于零的滤波电路是 。

13、互补功率放大电路中功放管的极限参数应满足CM P 。

14、单相桥式整流电路输入电压有效值为I U ,其脉动系数S= 。

15、单相桥式整流电路输出电压平均值为30V ,负载电阻Ω=50R L ,流过每个二极管的平均电流D I = 。

二、图2所示电路中,V 10V V EE CC ==,Ω=k 1R L ,晶体管参数相同:V 7.0U on =、100=β、Ω=k 1r be 、∞→ce r 。

①电路由几级放大电路构成?每级分别是何种放大电路?②求静态电流mA 5.0I 1C =时的电阻R ;③求电压放大倍数u A 。

(15分)图2三、图3所示为两级共射放大电路的波特图,求中频电压放大倍数u A 、下限截止频率L f 和上限截止频率H f 。

电子科技大学大二微电子专业模拟集成电路试卷及答案 (2)

………密………封………线………以………内………答………题………无………效……电子科技大学二零XX 至二零XX 学年第X 学期期终考试模拟集成电路原理课程考试题 A 卷(120分钟)考试形式:开卷考试日期20XX 年月日课程成绩构成:平时10 分,期中0 分,实验10 分,期末80 分一二三四五六七八九十合计一.选择题(共20题,每题2分,共40分)1.对于MOS管, 当W/L保持不变时, MOS管的跨导随漏电流的变化是( B )A. 单调增加B. 单调减小C. 开口向上的抛物线D.开口向下的抛物线.2. 对与MOS器件,器件如果进入饱和区, 跨导相比线性区将( A )A增加 B.减少 C不变 D 可能增加也可能减小3. 在W/L相同时, 采用”折叠”几何结构的MOS管较普通结构的MOS管, 它的栅电阻( C )A 增大B 不变C 减小D 可能增大也可能减小4. 关于衬底PNP,下列说法正确的是( A )A.所有衬底PNP集电极电压必须相同.B.所有衬底PNP发射极电压必须相同.C.所有衬底PNP基极电压必须相同.D.所有衬底PNP各个电极电压可以任意设定5. 对于扩散电阻, 其宽度越大, 则电阻值越易做得( A )A 精确, B误差大, C 误差可大可小, D电阻间的相对误差大.6. 室温下, 扩散电阻阻值的温度系数为( A )A 正, B零, C负, 可正可负7.在集成电路中决定互联线宽度的因素有( A )A.大电流密度限制.B.Si-Al互熔问题.C.互联线的温度系数………密………封………线………以………内………答………题………无………效……D.是否形成欧姆接触.8. 套筒式共源共栅运放和折叠式共源共栅运放相比, 它的( B )较大些A. 最大电压输出摆幅B. 差模增益C. 极点频率D.功耗9.在版图设计上, 采用比例电阻和比例电容的设计可以( C )A. 提高电阻或电容自身的绝对精度,B. 提高电阻或电容自身的相对精度,C. 减小电阻或电容间的比例误差D. 无影响10.差分对中, 不影响其共模抑制比的因素为( C )A.差分管的对称性B.电流源的交流阻抗C.输入电压幅度D.电阻R C1和R C2的对称性11. Cascode电流镜的最小输出电压V MIN(out)的值为( C )A.V ON+V TN B.2(V ON+V TN) C. 2V ON+V TN D. V ON+2V TN12.对于ED NMOS基准电压源电路, 其中的两个NMOS的工作状态为( A )A, 都是饱和区B. 一个是饱和区, 一个是线性区C 都是线性区D都是亚阈值区13正偏二级管正向压降具有( B )温度特性.A . 零 B. 负 C. 正 D. 可正可负14. MOS共栅放大器的特点是( D )A.放大器输入输出反相, 输入阻抗高B.放大器输入输出同相, 输入阻抗高………密………封………线………以………内………答………题………无………效……C.放大器输入输出反相, 输入阻抗低D.放大器输入输出同相, 输入阻抗低15. 电路的主极点是( D )A离原点最远的极点, 它对应电路的-3dB带宽B 离原点最远的极点, 它对应电路的单位增益带宽C离原点最近的极点, 它对应电路的单位增益带宽D.离原点最近的极点, 它对应电路的-3dB带宽16.在CMOS差分输入级中, 下面的做法哪个对减小输入失调电压有利( C )A.增大有源负载管的宽长比.B.提高静态工作电流..C.增大差分对管的沟道长度和宽度D.提高器件的开启(阈值)电压17.在差分电路中, 可采用恒流源替换”长尾”电阻. 这时要求替换”长尾”的恒流源的输出电阻( A )A.越高越好, B.越低越好 C. 没有要求D. 可高可低18. 和共源极放大器相比较, 共源共栅放大器的密勒效应要( A )A.小得多B相当, C 大得多. D不确定19.在版图设计上, 采用比例电阻和比例电容的设计可以( C )A. 提高电阻或电容自身的绝对精度,B. 提高电阻或电容自身的相对精度,C. 减小电阻或电容间的比例误差D. 无影响20.对于差分对的版图设计下列( D )图最优.………密………封………线………以………内………答………题………无………效……二. 简答题(共5题,每题4分, 共20分)1. 画出共源共栅放大器基本结构, 简述其工作原理及特点.答:基本原理:M1为输入器件,M2为共源共栅器件,共源级M1将输入电压信号Vin 转换为电流信号g m Vin ,该电流信号流入M2漏端,从其源端输入到负载。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

………密………封………线………以………内………答………题………无………效……

电子科技大学二零零 四 至二零零 五 学年第 二 学期期 中

《微电子电路设计》课程考试题( 120 分钟) 考试形式: 闭卷 考试日期 2005年 5 月 日

一 二 三 四 五 六 七 八 九 十 总分 评卷教师

1. Identify the source, drain, gate and bulk terminals, and find the current I in the

transistors in the following Figure. Assume 2'

/25V A K n

μ=,V TN =0.75V . (16pts) (problem4.3)

Solution:

(a) V V V V V V V V V S D DS S G GS 2.0)2.0(0,

5=--=-==-=

A V A V V V V L W K I I DS DS TN G n

DS μμ2082.022.075.02.51102522'

=⎪⎭⎫

⎝

⎛--=⎪⎭⎫ ⎝⎛--== (b) V V V V V V V V V S D DS S G GS 2.0)2.0(0,

2.5)2.0(5=--=-==--=-=

A V A V V V V L W K I I DS DS TN G n

DS μμ2182.022.075.02.51102522'

-=⎪⎭⎫

⎝

⎛--=⎪⎭⎫ ⎝⎛---=-=

………密………封………线………以………内………答………题………无………效……

2. Design the bias circuit in the following figure to give the Q-point of mA I C 10= and V V EC 3= if the transistor current gain is 75=F β and V V BE 7.0=.What is the Q-point if the current gain of the transistor is actually 40? (15 pts) ( problem 5.62 )

Solution:

Ω

→Ω=-==Ω→Ω=-===+=

=-=+-=183.171333.0)7.03( ,68069110013)310( 13.101075

76

1 ,10)(10k mA

V

I -V V R mA V R mA mA I I

I R I R I I V B EB EC B C C F F F

C

E C E C B C EC ββα

0)5()(6801800007.05=--+---B C B I I I

mA I I A V

I B F C B 108.8,

7.202)680(41180007.010===Ω

+-=

βμ

V mA V V EC 35.4680)311.8(10=Ω-= )35.4,11.8(:int V mA po Q -⇒

3. Find V OH , V OL and the power dissipation (for v o =V OL ) for the logic inverter with the saturated load in

the following figure. Assume 0=γ, and 2

'/25V A K n μ=,V V TN 1=. (16 pts) (Problem7.12m)

Solution:

V V V V For TN DD OH 6.216.3,0=-=-==γ

………密………封………线………以………内………答………题………无………效……

DSS DSL OL I I V For =,,

OL OL n OL n V V K V K ⎪⎭⎫ ⎝

⎛--⎪⎭⎫ ⎝⎛=--⇒216.215)16.3(212'2', V V OL 1927.0=⇒ A I DD

μ22.36)11927.06.3(2

12102526=--⨯=-

W A V P μμ39.130)22.36)(6.3(==

Checking: A I DD μ22.361927.0)2/1927.016.2(152

10256=--⎪⎭

⎫

⎝⎛⨯=

-

4. Design a CMOS logic gate that implements the logic function ADE ABC Y += based on the CMOS

inverter. Select the transistor sizes with the same delay as that of the reference inverter whose

15=⎪⎭⎫

⎝⎛P L W ,12=⎪⎭⎫ ⎝⎛L L W . ( 20 pts).

Solution:

………密………封………线………以………内………答………题………无………效……

5. Find the poles and zeros of the following transfer function, and draw its asymptote Bode plot of the magnitude. (17pts)

)

2000210)(10000)((10102()

50(10)(2

632

8++++⨯++=s s s s s s s s A V Solution :

Zeros: s z1=0, s z2=-50

Poles: s=-10, s=-200, s=-1000, s=-1000, s=-10000

6. Draw the output voltage waveform for the circuit in the following figure for the triangular input waveform shown. (16pts)

Solution:。