版图设计实例

Ledit及器件版图设计

L-EDIT的应用

Electrical properties:电学 特性的设定。比如单位 面积电容的设定。一般 不设定。 GDS number:设置图层 数等。 Default wire setting:设 置线宽和连接点形状等 特性。

L-EDIT的应用

derivation工具栏:推 导产生图层 Draw和derived:选择 该图层是由绘制产生还 是由已有图层逻辑运算 产生。

L-edit 的图层

L-EDIT的应用

当把鼠标箭头放在 某个图层上时就会 显示该层的名称, 点击左键就会选中 该图层,任何时候 只能选中一个图层。 在选中的情况下绘 图只会反应在该图 层上

L-edit 的图层

L-EDIT的应用

单击某一个图层的 鼠标右键时就会显 示图层选项,图层 右侧的三个图标分 别表示锁定图层, 显示图层和保护图 层 L-edit 的图层

L-EDIT的应用

双击图层左侧区 域或者选中基本 工具栏中setupapplication就会 弹出版图应用设 置菜单,其中包 括快捷键设置和 版图的一些限定 L-edit 的设置

L-EDIT的应用

首先设定user为软件文 件路径然后进行设置. Paste to cursor:粘贴到 鼠标指针。即粘贴时 图形将会跟随鼠标移 动,直到鼠标落键图 形才会消失

Fill和outline:表 示填充和轮廓线的 颜色和花纹的设置。

L-EDIT实例

国内设计多为逆向,但也需要根据市场需求做适当改 变,所以绘制版图前首先必须完成符合项目需求的元 胞及其工艺的仿真验证,确定基本的元胞参数和工艺 步骤,为绘制确定条件。其次,需要和生产厂商确定 设计规则和工艺限制条件,使版图的绘制有据可依。

二极管结构示意图版图设计规则版图设计规则版图设计规则版图设计规则版图设计规则ledit的应用ledit的应用ledit的应用ledit的应用ledit的应用ledit的应用ledit的应用ledit的应用ledit的应用ledit的应用ledit的应用ledit的应用ledit的应用ledit的应用ledit的应用ledit的应用ledit的应用ledit的应用ledit的应用ledit的应用ledit的应用ledit的应用ledit的应用ledit的应用ledit的应用ledit的应用ledit的应用ledit的应用ledit的应用ledit的应用ledit的应用ledit实例ledit实例ledit实例ledit实例ledit实例ledit实例ledit实例ledit实例ledit实例ledit实例ledit实例ledit实例ledit实例ledit实例ledit实例ledit实例ledit实例ledit实例ledit实例ledit实例ledit实例ledit实例ledit实例ledit实例ledit实例ledit实例ledit实例ledit实例ledit实例ledit实例ledit实例ledit实例thanks

Cadence版图设计

第二章. Virtuoso Editing 的使用简介

全文将用一个贯穿始终的例子来说明如何绘制版图。这个例子绘制的是一个最简单的非 门的版图。

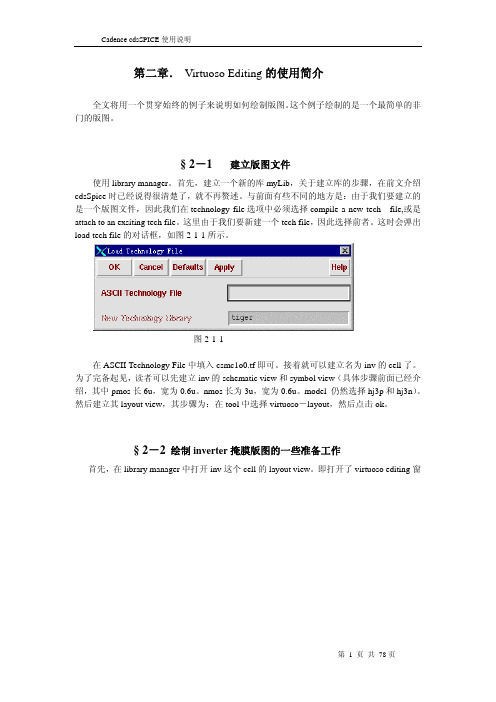

§ 2-1 建立版图文件

使用 library manager。首先,建立一个新的库 myLib,关于建立库的步骤,在前文介绍 cdsSpice 时已经说得很清楚了,就不再赘述。与前面有些不同的地方是:由于我们要建立的 是一个版图文件,因此我们在 technology file 选项中必须选择 compile a new tech file,或是 attach to an exsiting tech file。这里由于我们要新建一个 tech file,因此选择前者。这时会弹出 load tech file 的对话框,如图 2-1-1 所示。

Undo

------- 取消编辑(u)

Redo

-------恢复编辑 (U)

Move

------- 移动(m)

Stretch

------- 伸缩(s)

Rectangle -------编辑矩形图形(r)

Polygon

------- 编辑多边形图形(P)

Path

------- 编辑布线路径(p)

Copy

3.6u

0.6u

0.6u

3u

3u 图 2-3-2nmos 版图 四.完成整个非门的绘制及绘制输入、输出

1. 新建一个 cell(inv)。将上面完成的两个版图拷贝到其中,并以多晶硅为基准将两

第 8 页 共 78 页

Cadence cdsSPICE 使用说明

图对齐。然后,我们可以将任意一个版图的多晶硅延长和另外一个的多晶硅相交。 2. 输入:为了与外部电路连接,我们需要用到 metal2。但 poly 和 metal2 不能直接相

ADS2011版图优化设计实例

ADS2011版图优化——以Diplexer设计为例高峰3100101290ADS2011版图中没有直接优化的功能,不能像2006一样直接在版图中定义参数,针对版图参数进行优化,它需要在版图中定义参数后,生成原理图原件(Symbol),然后在原理图中对生成元件的参数进行优化,最后在由优化好的原理图重新生成原理图才能够完成优化目标。

下面以频分2.4G 双工器为例具体说明ADS的优化过程。

1.双工器设计指标:与参考文献,“A compact Diplexer Using Square Open Loop with Stepped Impedance Resonators”中的指标相同。

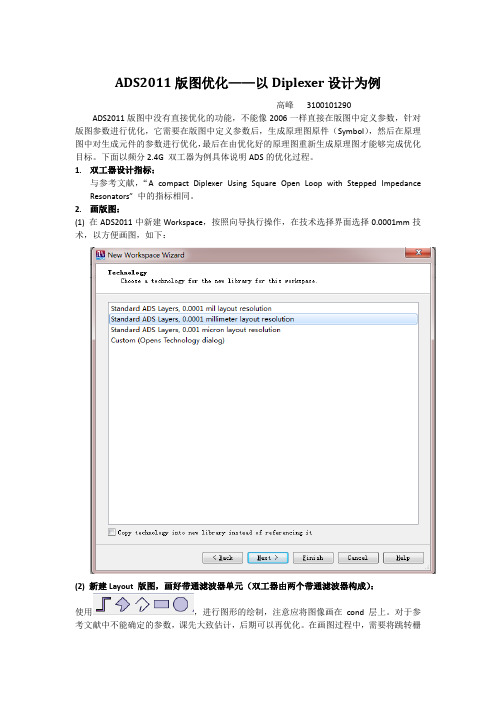

2.画版图:(1) 在ADS2011中新建Workspace,按照向导执行操作,在技术选择界面选择0.0001mm技术,以方便画图,如下:(2) 新建Layout 版图,画好带通滤波器单元(双工器由两个带通滤波器构成):使用,进行图形的绘制,注意应将图像画在cond层上。

对于参考文献中不能确定的参数,课先大致估计,后期可以再优化。

在画图过程中,需要将跳转栅格改到小才能画出变化0.05mm的长度,在Option-Preference菜单中修改,如下图:电路图中的各尺寸参数在文献中大多有,没有的可用尺子量得大致值。

画好后得到如下图的电路:点击进行仿真设置以进行初次仿真,如下图:Substrate 与ports为黄色感叹号,表示还未设置。

点击substrate,然后点击New按钮,新建基质文件,如下图:上图中,顶层微带线与底层地面的材料均选用铜,厚度设置为0.2mm,中间介质采用默认的Alumina(氧化铝),厚度设置为3mm。

这些参数由于文献中未提到,只能先设置为猜想的合适值,在后面仿真后手动修改,比较仿真结果找到比较合适的结果(基质参数无法优化)。

返回到版图界面用设置好端口后,再对仿真频率进行设置,将频率设置为1.4~2.6Ghz。

Lab 7 MOS管版图设计

Lab 7 MOS管版图设计1.实验目的1.1 掌握MOS管版图设计规则1.2 熟悉LSW设计环境1.3 学会MOS管版图设计方法2.实验原理MOS管单元版图设计是整个版图设计的基础。

根据工艺文件提供的版图设计规则,可以以几何绘图的方式完成版图设计。

在具体设计版图之前,首先是准备工作:在library manager中建立nmos版图视图,打开virtuoso layout editing 窗口与LSW窗口,熟悉两窗口中菜单命令,建立工艺库所需的版图层次及其显示属性,设置版图设计环境下的盲键等。

以上工作在lab6中已经完成设置,下面以给定的设计规则为依据,进行nmos等单元版图设计。

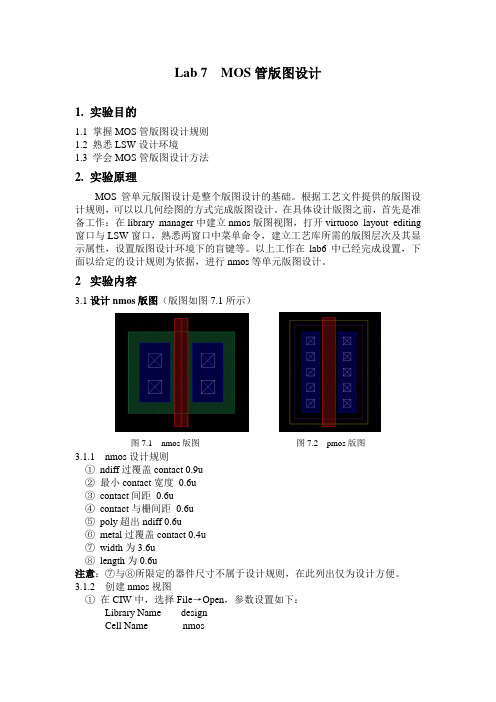

2实验内容3.1设计nmos版图(版图如图7.1所示)图7.1 nmos版图图7.2 pmos版图3.1.1nmos设计规则①ndiff过覆盖contact 0.9u②最小contact宽度0.6u③contact间距0.6u④contact与栅间距0.6u⑤poly超出ndiff 0.6u⑥metal过覆盖contact 0.4u⑦width为3.6u⑧length为0.6u注意:⑦与⑧所限定的器件尺寸不属于设计规则,在此列出仅为设计方便。

3.1.2创建nmos视图①在CIW中,选择File→Open,参数设置如下:Library Name designCell Name nmosView Name layout点击OK,打开design的空白窗口,以下编辑将实现nmos版图结构如图所示。

②在LSW窗口中,选择poly drawing作为当前编辑层。

③选择Create→Path或按盲键[p],来绘制多晶硅栅体。

④在design窗口中,点击LMB,从坐标原点x=0、y=0到x=0、y=4.8连线poly,之后双击LMB或按Return(Enter)键,完成栅体绘制。

⑤在LSW窗口中,选择ndiff drawing层为当前编辑层,选择Create→Rectangle或按盲键[r],用以绘制扩散区。

北大集成电路版图设计课件_第9章集成电路版图设计实例

2

1

2

1

2

3

1

3

2

3

1

3

R1和R2的共质心结构版图设计

加入R3后的共质心版图设计

49

9.7带隙基准源版图实例

总体版图实例

比例电阻

运算放大器

1:8 晶体管

50

9.8芯片总体设计

首先,在总体版图的布局上,尽量将数字部分远离模拟部分,如果 总体电路中模拟部分偏多,则在版图设计中将数字部分放在靠边的位 置,而且把模拟部分中最容易被数字干扰的部分放到离数字部分最远 的位置,同时在数字部分和模拟部分中间用接地的衬底接触来进行隔 离,反之亦然。 其次,采用隔离环设计,对每个单元模块都用一层接地的衬底接触, 一层接电源的N阱构成的隔离环来进行隔离。对于整个模拟部分和数 字也分别采用相同的隔离环隔离,数字电路的隔离环可以吸收数字电 路的衬底噪声,从而可以减少通过衬底串扰到模拟电路的衬底噪声。 隔离环包的层数越多,理论上吸收衬底噪声效果越好。但是要避免数 字电路的p隔离环紧靠模拟电路的p型隔离环,因为在这种情况下数字 地的噪声会串扰到模拟地。从而使模拟地受到干扰。

1.反相器-并联反相器的版图

直接并联

共用漏区

7

9.2 数字版图设计实例

2.与非门

VCC A Q1 Q2 OUT B Q3

Q4

按电路图转换

MOS管水平走向设计

8

9.2 数字版图设计实例

3.或非门

VCC A Q1

B

Q2 OUT Q3 Q4

按电路图转换

MOS管水平走向设计

9

9.2 数字版图设计实例

4.传输门

25

9.5静电保护电路设计实例

集成电路版图设计习题答案第九章集成电路版图设计实例

第9章集成电路版图设计实例【习题答案】1.版图设计关于数字地和模拟地的考虑事项是什么?答:一般的模拟集成电路中,通常既有数字信号又有模拟信号,数字信号和模拟信号之间容易发生干扰。

在版图设计过程中,还要考虑地噪声对电路的影响。

即在整体版图的设计中,需着重考虑电路噪声问题,按照尽量降低噪声的原则进行电路的整体布局。

首先,在总体版图的布局上,尽量将数字部分远离模拟部分,如果总体电路中模拟部分偏多,则在版图设计中将数字部分放在靠边的位置,而且把模拟部分中最容易被数字干扰的部分放到离数字部分最远的位置,同时在数字部分和模拟部分中间用接地的衬底接触来进行隔离,反之亦然。

其次,采用隔离环设计,对每个单元模块都用一层接地的衬底接触,一层接电源的N阱构成的隔离环来进行隔离。

对于整个模拟部分和数字也分别采用相同的隔离环隔离,数字电路的隔离环可以吸收数字电路的衬底噪声,从而可以减少通过衬底串扰到模拟电路的衬底噪声。

隔离环包的层数越多,理论上吸收衬底噪声效果越好。

但是要避免数字电路的p隔离环紧靠模拟电路的p型隔离环,因为在这种情况下数字地的噪声会串扰到模拟地。

从而使模拟地受到干扰。

最后,除了数字模块之外的其它单元模块尽量将距离缩短,这样一方面能尽量地减少互连线经过别的区域引入噪声,同时也能降低引线过长引起电压信号的衰减。

2.总结自己的版图设计技巧和经验。

3. 共质心MOS管设计时的注意事项是什么?答:低精度要求可采用一维共质心,高精度要求必须采用二维共质心。

共质心设计时需保证MO管的对称性和电流通路的对称性。

4. 静电保护的种类以及版图设计注意事项。

答:常用的二极管式的静电保护分为两种方式,一种是用MOS晶体管连接成二极管形式的静电保护,一种利用CMOS工艺中二极管的静电保护。

在MOS型静电保护版图设计中,主要考虑以下几点:●MOS管要分成多个管,叉指结构,以便形成多支路共同放电。

●因为放电瞬间流经MOS管的电流特别大,构成整个放电通路的任何导线的宽度一定要有足够保证,而且CMOS工艺对于每个接触孔能通过的电流密度还有要求,因此还要保证放电通路导线上孔的数目应尽量多。

实验一_MOS管版图设计

实验一 MOS 管版图设计一、实验目的1、了解版图设计基本流程2、熟悉版图设计工具Virtuso 的使用方法3、根据要求画出NMOS 和PMOS 版图。

二、实验内容1、回顾版图设计基本原理,如版图设计规则、工艺文件等。

2、熟悉版图设计工具Virtuso 的使用方法3、用Virtuso 画NMOS 和PMOS 版图。

其中PMOS 的尺寸为m W μ6=,m L μ1=,NMOS 的尺寸为m W μ3=,m L μ1=。

三、实验步骤1、运行cadence 工具(1)用exceed 登陆。

(运行“Hummingbird Connectivity V7.0”,选择broadcast ,显示当前可以登陆的工作站)(2)将压缩“layout.tar.gz ”文件包复制到自己的目录下,解压缩命令:tar –zxvf layout.tar.gz在目录下会出现文件夹“layout ”(3)Virtuso 启动:在layout 目录下启动。

$source /opt/bashrc$icfb&(或layout )2、版图设计基本流程(1)建立一个新的库(file/new/library)。

(2)关联到指定工艺库。

选择layout下面的tsmc18_文件添加。

(tf文件的作用是描述“层”)(3)手工画版图先建立小的单元,然后以小单元为基础构成较大的单元、模块、芯片等。

AC:diff+cont+M1VC12:M1和M2之间的通孔。

M1+via+M2PC:poly contact。

Cont+poly+M13、熟悉快捷键的使用。

以下是快捷键的总结。

Ctrl+E:放大,缩小Ctrl+空格:删除Ctrl+A:全选Ctrl+Q Ctrl+F Ctrl+XD:测量间距Shift+d:取消标尺Shift+z:缩小Shift+e:取消repeat command选项Shift+h:将鼠标放置在左下角上,归原点P:在出现的display option对话框中选择Grid,即鼠标移动一下的距离(精度)S:调整大小R:画矩形F:合适大小显示Z:放大。

第8章三极管版图

偏置电路及静态工作点

偏置电路

为了使三极管正常工作在放大状态,需要为其设置合适的偏置电路。偏置电路的 主要作用是为三极管的基极提供稳定的直流电压,使其工作在合适的静态工作点 。

静态工作点

静态工作点是指三极管在没有输入信号时的工作状态。在这个状态下,三极管的 基极电流、发射极电流和集电极电流都保持在一个稳定的值。静态工作点的设置 对于三极管的放大性能和稳定性至关重要。

防静电措施

在版图设计中考虑防静电措施,如增加接地引脚、设置静电放电通 路等,以避免静电对三极管的损害。

05

三极管版图仿真与验证

仿真工具介绍及使用方法

仿真工具介绍

目前常用的三极管版图仿真工具有 Cadence、Synopsys和Mentor等公 司的EDA软件,这些软件提供了全面 的电路设计和仿真功能,支持多种工 艺库和器件模型。

电流放大原理

电流放大倍数(β值)

三极管具有电流放大功能,即当基极电流发生变化时,集电极电流会按照一定比例放大。这个比例被 称为三极管的电流放大倍数,用β值表示。

电流放大原理

当基极电流增大时,发射极向基极提供的电子流也相应增大,导致集电极电流增大。由于集电极面积 较大,可以收集更多的电子,因此集电极电流的变化幅度大于基极电流的变化幅度,实现了电流的放 大。

传感器接口电路设计案例

传感器信号放大

信号调理电路

利用三极管构成的放大电路,对传感器输 出的微弱信号进行放大。

采用三极管构成信号调理电路,对放大后 的传感器信号进行进一步的处理和转换。

输出驱动电路

电源与接地处理

利用三极管作为输出驱动电路,将处理后 的传感器信号转换为适合后续电路处理的 信号形式。

在传感器接口电路中,同样需要注意电源 和接地的布局,以降低电源噪声对传感器 信号的影响。

CMOS反相器的版图设计

实验一:CMOS反相器的版图设计一、实验目的1、创建CMOS反相器的电路原理图Schematic、电气符号symbol以及版图layout;2、利用’gpdk090’工艺库实例化MOS管;3、运行设计规则验证Design Rule Check;DRC确保版图没有设计规则错误..二、实验要求1、打印出完整的CMOS反相器的电路原理图以及版图;2、打印CMOS反相器的DRC报告..三、实验工具Virtuoso四、实验内容1、创建CMOS反相器的电路原理图;2、创建CMOS反相器的电气符号;3、创建CMOS反相器的版图;4、对版图进行DRC验证..1、创建CMOS反相器的电路原理图及电气符号图首先创建自己的工作目录并将/home/iccad/cds.lib复制到自己的工作目录下我的工作目录为/home/iccad/iclab;在工作目录内打开终端并打开virtuoso命令为icfb &.在打开的icfb –log中选择tools->Library Manager;再创建自己的库;在当前的对话框上选择File->New->Library;创建自己的库并为自己的库命名我的命名为lab1;点击OK后在弹出的对话框中选择Attach to an exiting techfile并选择gpdk090_v4.6的库;此时Library manager的窗口应如图1所示:图1 创建好的自己的库以及inv创建好自己的库之后;就可以开始绘制电路原理图;在Library manager窗口中选中lab1;点击File->New->Cell view;将这个视图命名为invCMOS反相器..需要注意的是Library Name一定是自己的库;View Name是schematic;具体如图2所示:图2 inv电路原理图的创建窗口点击OK后弹出schematic editing的对话框;就可以开始绘制反相器的电路原理图schematic view..其中nmos宽为120nm;长为100nm.与pmos宽为240nm;长为100nm.从gpdk090_v4.6这个库中添加;vdd与gnd在analogLib这个库中添加;将各个原件用wire连接起来;连接好的反相器电路原理图如图3所示:图3 inv的电路原理图对电路原理图检查并保存左边菜单栏的第一个;check and save;接下来创建CMOS反相器的电气符号图创建电气符号图是为了之后在其他的门电路中更方便的绘制电路原理图..在菜单栏中选择design->Create cellview->From cellview;在symbol editing中编辑反相器的电气符号图;创建好的symbol如图4所示:图4 inv的电气符号图2、创建CMOS反相器的版图接下来可以创建并绘制CMOS反相器的版图;在Library Manager中选择File->new->cell view;将view name改为layout;tool改为virtuoso;具体如图5所示:图5 inv版图的创建窗口点击OK;会弹出两个对话框;一个LSW和一个layout editing在弹出来的layout editing中进行版图的绘制;利用快捷键‘i’在gpdk090_v4.6选择nmos和pmos;并将pmos摆放至nmos的上方;为方便确认各个金属或者mos管的距离或者长度;可以使用尺子作为辅助;使用快捷键’k’画一个尺子;使得nmos与pmos的源漏之间距离为0.6nm;如图6所示:图6 mos管源漏之间的距离图然后继续用尺子在nmos与pmos的正中间分别往上下延伸1.5nm;该点即为电源轨道和地轨道的中心点;轨道的宽为0.6nm;长为1.8nm;在LSW窗口中选择metal1作为电源轨道;返回layout editing窗口;使用快捷键’p’;然后设置金属的宽度;将其设置为0.6nm;接着在layout editing窗口中将轨道绘制出来;nmos与pmos 之间用poly金属层连接起来;pmos的源级用metal1金属与上层的电源轨道连接起来;nmos的源级用metal1金属与下层的电源轨道连接起来;并在vdd电源轨道上加一个M1_NWELL;在gnd轨道上加一个M1_PSUB;放置好选中并点击快捷钱’q’;将通孔个数改为3个如图7所示;将columns那一栏的1改为3;pmos及以上部分用nwell包裹起来;具体的连接如图8所示:图7 M1_NWELL的属性图8 连接好的inv版图3、设计规则检查DRC将连接好的inv版图保存;在菜单栏上选择verify->DRC;在弹出的对话框修改一些信息;如图9所示;确保路径正确;并且将Rules library前的勾选取消..图9 DRC的参数设置点击OK;验证完成并成功后会在icfb –log窗口出现如图10所示提示且版图上不会出现错误闪烁;如果有错误的话;可以在菜单栏中点击verify->markets->explain;并选中错误的地方;就会弹出详细的错误解释;然后根据提示修改错误..图10 DRC报告4、打印CMOS反相器的电路原理图以及版图在layout editing窗口的菜单栏上选择Design->plot->submit;然后再弹出来的窗口中修改参数;将header前的勾选取消;如图11所示:图11 打印参数设置继续点击Plot Options;将里面的参数修改如图12所示:图12 打印参数设置点击OK;可在自己的工作目录下找到inv.ps文件;打开文件即可看到打印出来的CMOS反相器版图;如图13所示:图13 打印出来的CMOS反相器版图同理;电路原理图也是如此打印;打印出来的CMOS反相器的电路原理图如图14所示:图14 打印出来的CMOS反相器的电路原理图。

第13章实际PCB板图设计实例PPT课件

元件所属Sch库: U1在Protel DOS Schematic Libraries.ddb

其余元件在Miscellaneous Devices.ddb Pcb元件封装库: Advpcb.ddb

元件封装

DIP14 AXIAL0.4 AXIAL0.4 RAD0.2

SIP3

实际PCB板图设计举例 广西工业职业技术学院

Protel 99SE---黄飞

第13章 实际PCB板图设计举例

放置元件U1B的方法:(U1C 同理)

① 放置元件4011。 ② 双击4011,调出其属性对话

框,如图13.4。 ③ 在第2个Part旁的文本框中

输入“2”,元件标号 Designator仍输入U1,如图 13.4。 ④ 此时4011第2个单元的图形 如图13.5所示,其元件标号 U1B中的B为系统自动加上。

实际PCB板图设计举例 广西工业职业技术学院

Protel 99SE---黄飞 第13章 实际PCB板图设计举例

本章重点:

1 自动布局和手工布线的方法绘制PCB图 2 自动布局和自动布线的方法绘制PCB图 3 原理图元件符号的引脚与元件封装中的焊盘 以及元件的实际尺寸之间的对应

实际PCB板图设计举例 广西工业职业技术学院

第1步:新建一个原理图文件“Li13_1.sch” 第2步:打开“Li13_1.sch”,加载元件库Miscellaneous Devices.ddb和Protel DOS Schematic Libraries.ddb。 第3步:按图13.3绘制原理图,元件的所有属性均按照 表13.1输入。

实际PCB板图设计举例 广西工业职业技术学院

(4)尽量避免信号线近距离平行走线。若无法避免平行分 布,可在平行信号线的反面布置大面积的“地”来大幅度减 少干扰。在相邻的两个工作层,走线的方向必须相互垂直。 (5)对于高频电路可对整个板进行“铺铜”操作,以提高 抗干扰能力。 (6)在布线过程中,应尽量减少过孔,尤其是在高频电路 中。因为过孔容易产生分布电容。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

④ N阱CMOS集成电路使用P型衬底,NMOS管直接制作在 P型衬底上,PMOS管做在N阱内。

精选ppt

3

⑤ 完整的MOS管版版图必须包含两个部分:a)由源、栅和 漏组成的器件;b)衬底连接。

精选ppt

4

5.1.2 MOS管阵列的版图实现

1.MOS管串联

(1) 两个MOS管的串联。 N1的源、漏区为X和Y,N0的源、漏区为Y和Z。Y是它们的公共区域,如 果把公共区域合并,得到图5.7(d)所示的两个MOS管串联连接的版图。 从电流的方向可以决定,当MOS管串联时,它们的电极按S-D-S-D-S-D方 式连接。

或非门分开布局,P管和N管各占一行。

精选ppt

10

(3)二输入端与门(and2)

特点:与门由与非门和反相器串联而成,采用合并公共区域 的技巧,将P管接电源的有源区公用,N管接地的有源区公用, 器件的排列很紧凑,面积很小。

精选ppt

11

(4) 与或非门(AOI)

(2)栅极竖直方向排列,节点连接既可用金属导线(图b),也 可用有源区进行连接(图c)。

精选ppt

6

(3)三个或三个以上MOS管并联。 ① 全部用金属进行源的连接和漏的连接(图a),称为叉指形结构; ② 分别用金属和有源区进行源和漏的并联连接; ③ 金属连接和有源区连接联合使用(图b)。

3.MOS管的复联 复联是MOS管先串后并和先并后串的连接。

精选ppt

16

2. CMOS RAM单元及阵列 (1)CMOS RAM单元

特点:版图用双层金属设计。两个反相器共源,它们的

交叉连接和衬底连接都用金属1,两条位线也用金属1作为连

线。Vdd、Vss和W用金属2作为导线。门管的多晶栅和金属1

连接,然后金属1经过通孔连接到用字线。阱和衬底的接触也

经过通孔连接到Vdd和Vss。

精选ppt

14

版图

精选ppt

15

特点: ① 和异或门相似,几个输入信号被几乎所有的器件公用, 设计版图时要充分注意这一特点。 ② 版图把A、B、C多晶分成二段且排成二列,A线在上面 (靠近Vdd)转折连接,B线在下面(靠近Vss)转折连接,C线二段 不能直接连接,在Vss附近用金属连接。 ③ 用左面一列A、B、C多晶布局器件的串并联,右面一列A、 B、C多晶布局器件的串联。整个电路分为4行,第2和第3行组 成进位电路的前级,第1行和第4行组成求和电路的前级。 ④ 进位与求和的输出反相器采用较大的宽长比。 ⑤ 在版图中间一条横的金属线阻挡了进位部分串并联电路 的输出从上至下进行连接,用多晶从该金属线下穿过将这段输 出金属连接。

精选ppt

17

(2) CMOS RAM阵列

特点:存储单元排成阵列时,列的方向只要求相邻单元位

线的间距符合设计规则;行的布局合并了公共区域,即Vdd和

Vss共用。

精选ppt

18

3. CMOS D触发器 (1) 无置位和复位端的D触发器

电路图

电路图中,用钟控反相器代替反相器和传输门(TG2)串联。

精选ppt

(a) 电路图

(b) N1版图 (c) N0版图 (d) N1和N0串联版图

(2) 任意个MOS管串联。例如3个MOS管串联的版图。

(a)电路图

(b) 版图

精选ppt

5

2.MOS管并联(并联是指它们的源和源连接,漏和漏连接,各 自的栅还是独立的。) (1)栅极水平放置,节点X和Y可用金 属连线连接(图b);也可用有源区连接(图c)。

版图设计实例

精选ppt

1

MOS 场效应管的版图实现

单个MOS管的版图实现

1. MOS管的结构和布局

① MOS管的四种布局图

精选ppt

2

③ 源区、沟道区和漏区合称为MOS管的有源区(Active),而有源区之外 的区域定义为场区(Fox)。有源区和场区之和就是整个芯片表面。

Fox + Active = Surface

提示:设计AOI或OAI的版图,一定要熟练掌握MOS管串联和

并联的画法后进行,看清每个MOS管的输入信号,用棍棒图画

出草图后再画版图。

精选ppt

12

(5) 或与非门(OAI)

提示:对比AOI和OAI电路图和版图的区别和画法,巩固和 熟练掌握CMOS复联电路版图的画法。

精选ppt

13

(6) 全加器

19

版图

特点:1)版图为4行结构,中间两行构成反相器,多晶从第2行延伸到第3行就 形成反相器。

2)第1行和第4行构成传输门,虽然被第2、3行分隔开,但这两行MOS管不需 要多晶共用,只用金属进行源漏连接,即使这些金属连线跨过中间两行有源区,也 不会形成寄生MOS管。

3)CP多晶放在Vdd线下,CPb多晶沿Vss水平布线,在中央部位,这两条多晶 都从有源区的空隙分别延伸到Vdd和Vss线附近,与传输门器件的栅级连接。

21

4. CMOS放大器

精选ppt

22

分割输入器件实现四方交叉:将M3变为M3a和M3b,M4变 为M4a和M4b,就可以实现四方交叉,保证输入器件的对称 性。

精选ppt

23

由于全部电流都要通过输入晶体管中的每一个,例如,有时整个电 流完全在M3,当差分信号关断时,M3关断M4接通,整个电流又完全在 M4,信号每摆动一次就切换一次,为了承受这一电流,在M3和M4之间 的金属线需要达到一定的宽度,采用二条金属线连接M3和M4的源极,并 且从M4b和M3b的中间向下,这样,M3导通时电流将通过M3a和M3b, 即它的两半把电流向下送到中心导线。

精选ppt

7

1. CMOS门电路

(1) 反相器

电路图

版图1

版图2

版图1特点:多晶栅竖直排列,MOS管源区面积小,因而反相器面积也小。

版图2特点:多晶栅水平排列,MOS管漏极金属与电源、地金属线之间的

空档允许其它金属线通过,因水平尺寸较大而使面积稍大一些。

精选ppt

8

(2) 异或门

版图1特点:多晶栅竖直放置;MOS管排成4行,第2和第4行构 成或非门,第1和第3行构成与或非门.整个版图较高。

4)主触发器采用钟控反相器,节省一根金属连线。

精选ppt

20

(2) 带置位端的D触发器

电路图

版图 精选ppt

特点:器件仍分 为4层,CP和CPb也 位于上下两边,并且 在CP多晶的上方增 加一条水平的多晶作 为复位(R)。CPb 线在水平和垂直方向 的连接采用金属过渡。 主触发器采用钟控或 非门,节省一根金属 连线。