Booth乘法器实验报告

实验二_乘法器

2 运算器部件实验:乘法器 (1)2.1、实验目的 (1)2.2、实验原理 (1)2.3、实验步骤 (7)2.4、实验现象 (7)2.5、思考题 (8)2 运算器部件实验:乘法器2.1、实验目的1、掌握乘法器以及booth乘法器的原理2.2、实验原理首先我们看一下十进制数的乘法。

为了方便起见,我们假定十进制数的各位要么为1要么为0,例如1000×1001:被乘数 1 0 0 010乘数× 1 0 0 1101 0 0 00 0 0 00 0 0 01 0 0 0积 1 0 0 1 0 0 010从上面的步骤我们可以看到,1)从右到左用乘数的每一位乘以被乘数,每一次乘得的中间结果比上一次的结果往左移一位。

2)积的位数比被乘数和乘数的位数要多的多。

事实上,如果我们忽略符号位,n位的被乘数和m位的乘数相乘的结果的位数有(n+m)位。

因此,乘法必须象加法那样处理溢出问题,如果两个32位的数相乘,积也只有32位的时候,就会出现溢出。

在上面的例子中,我们把十进制数的各位限制为0或1。

因此,每一步的乘法相当简单:1)如果乘数位是1,则简单的复制被乘数到合适的位置(1×被乘数);2)如果乘数位是0,则在合适的位置置0因为二进制数的各位是0或1,所以与上面情况类似。

既然已经知道了乘法的基本规律,下一步就是设计高度优化的乘法器硬件。

为了让大家更明了乘法器的原理,我们一一列举乘法器的三个版本的改进。

我们先假定被乘数和乘数都是正数。

1、第一代乘法器初始的设计模拟我们刚才提到的乘法流程,硬件结构如图2.1所示。

假定乘数在32位乘数寄存器里,64位的积寄存器初始化为0,显然每一步需要把被乘数左移一位。

左移32次之后,被乘数的32位会被移到左边,因此我们需要64位的被乘数寄存器,初始状态为低32位是被乘数,高32位是0。

这个寄存器每一步左移一位,和中间结果对齐,进行相加,相加的结果存在被乘数寄存器里。

计算机组成原理实验_乘法器

数学与计算机学院计算机组成原理实验报告年级08信计学号2008431066 姓名刘泽隶实验地点主楼528 指导教师陈昊实验项目运算器部件实验乘法器实验日期2010-11-10一、实验目的理解并掌握乘法器的原理。

二、实验原理(1)从右到左用乘数的每一位乘以被乘数,每一次乘得的中间结果比上一次的结果往左移一位。

(2)积的位数比被乘数和乘数的位数要多得多。

如果忽略符号位,n位的被乘数和m位的乘数相乘的结果的位数有(m+n)位。

每一位的乘法:(1)如果乘数位是1,则简单的复制被乘数到合适的位置(1*被乘数);(2)如果乘数位是0,则在合适的位置置0。

三、实验步骤(1) 打开QuartusⅡ,参照3.4节,安装ByteBlasterⅡ。

(2) 将子板上的JTAG端口和PC机的并行口用下载电缆连接。

打开实验台电源。

(3) 执行Tool->Progmmer命令,将Hamming.sof下载到FPGA中。

SOF(SRAMobject file)类型的文件是一种课下载到FPGA中的目标文件。

注意在执行Programmer命令中,英在program/configure下的方框中打钩,然后下载。

(4) 在实验台上通过模式开关选择FPGA-CPU独立调试模式010。

(5)将开关CLKSEL拨到0,将短路子DZ3短接且短路子DZ4断开,使FPGA-CPU所需要的时钟使用正单脉冲时钟。

四、实验现象本实验实现4位数的Booth乘法(有符号数乘法)输入输出规则对应如下:(1)输入的4位被乘数md3~md0对应开关SD11~SD8。

(2)输入的4位乘数mr3~mr0对应开关SD3~SD0。

(3)按单脉冲按钮,输入脉冲,也即节拍。

(4)乘积productp8-p0,对应灯A8-A0。

(5)当计算结束时,final信号为1,对应灯A7。

如表所示的booth算法运算过程,4位乘法一共需要0-8共9个小步骤计算出结果,本实验也是通过9个小步骤实现的,通过按单脉冲按钮输入脉冲,观察积寄存器的变化,掌握booth乘法器的原理。

67_67位乘法器的改进四阶Booth算法实现

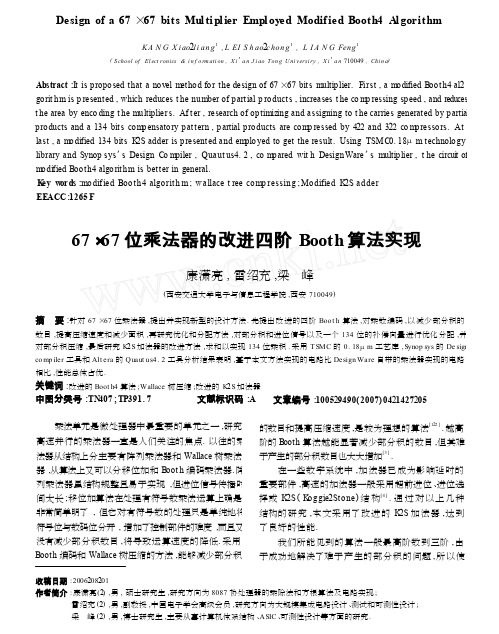

Design of a 67 ×67 bits Mul t i pl i er Empl oyed Modif ied Booth4 A l gorithmK A N G X i ao 2l i a n g 1, L E I S h a o 2c hon g 1, L I A N G Fe n g 1( S c h ool o f El ect roni c s & i n f o r m at i on , X i ’a n J i ao T on g U ni ve r si r y , X i ’a n 710049 , Chi n a )Abstract :It is p r opo s ed t h at a novel m et h od for t h e design of 67 ×67 bit s multiplier . Fir s t , a m odified B oot h 4 al 2 gorit hm is p resented , which reduces t he number of partial p roduct s , increases t he co m p ressing speed , and reduces t he area by enco ding t he multiplier s. Af ter , research of optimiz ing and assigning to t he carries generated by partial p r o d uct s and a 134 bit s co m pensatory pattern , partial p r oduct s are co m p ressed by 422 and 322 co m p r essor s . At last , a m odi fied 134 bit s K 2S adder is p r esented and em ployed to get t h e result . U s ing TSMC 0. 18μm technolo g y library and Synop sys ’s Design C o m piler , Quaut us4. 2 , co m pared wit h DesignWare ’s multiplier , t he circui t of m odi fied B oot h 4 algo r it h m is better in general .K ey w ords :mo d if ied Boo t h 4 al g o r it h m ; w allace t ree co m p r e s si n g ; M o d ified K 2S a d der EE ACC :1265 F67 ×67 位乘法器的改进四阶 Booth 算法实现康潇亮 , 雷绍充 ,梁 峰(西安交通大学电子与信息工程学院 ,西安 710049)摘 要 :针对 67 ×67 位乘法器 ,提出并实现新型的设计方法 . 先提出改进的四阶 Boo t h 算法 ,对乘数编码 ,以减少部分积的数目 ,提高压缩速度和减少面积 ,再研究优化和分配方法 ,对部分积和进位信号以及一个 134 位的补偿向量进行优化分配 ,并 对部分积压缩 ,最后研究 K 2S 加法器的改进方法 ,求和以实现 134 位乘积 . 采用 TSMC 的 0 . 18μm 工艺库 , Synop sys 的 De signco m p iler 工具和 Alt era 的 Q u aut u s4 . 2 工具分析结果表明 ,基于本文方法实现的电路比 Design Wa r e 自带的乘法器实现的电路相比 ,性能总体占优 .关键词 :改进的 Boo t h 4 算法 ; W allace 树压缩 ;改进的 K 2S 加法器 中图分类号 :TN 407 ; T P391 . 7 文献标识码 :A文章编号 :100529490( 2007) 0421427205的数目和提高压缩速度 ,是较为理想的算法[ 122 ] . 越高 阶的 B oot h 算法越能显著减少部分积的数目 ,但其难 于产生的部分积数目也大大增加[ 3 ] .在一些数字系统中 ,加法器已成为影响延时的 重要部件 ,高速的加法器一般采用超前进位 、进位选 择或 K 2S ( K o g gie 2Sto n e ) 结 构[ 4 ] . 通 过 对 以 上 几 种 结构的研究 , 本文采用了改进的 K 2S 加法器 , 达到 了良好的性能 .我们所能见到的算法一般最高阶数到三阶 ,由 于成功地解决了难于产生的部分积的问题 ,所以使乘法单元是微处理器中最重要的单元之一 ,研究 高速并行的乘法器一直是人们关注的焦点. 以往的乘 法器从结构上分主要有阵列乘法器和 Wallace 树乘法 器 ,从算法上又可以分移位加和 B oot h 编码乘法器. 阵 列乘法器虽结构规整且易于实现 ,但进位信号传播时 间太长 ;移位加算法在处理有符号数乘法运算上确是 非常简单明了 , 但它对有符号数的处理只是单纯地将 符号位与数码位分开 , 增加了控制部件的难度 ,而且又 没有减少部分积数目 ,将导致运算速度的降低. 采用 B oot h 编码和 Wallace 树压缩的方法 ,能够减少部分积收稿日期 :2006208201作者简介 :康潇亮 (2) ,男 , 硕士研究生 ,研究方向为 8087 协处理器的乘除法和方根算法及电路实现 ;雷绍充 (2) ,男 ,副教授 ,中国电子学会高级会员 ,研究方向为大规模集成电路设计 、测试和可测性设计 ; 梁 峰 (2) ,男 ,博士研究生 ,主要从事计算机体系结构 、A S IC 、可测性设计等方面的研究 .1428电 子 器 件第 30 卷表 1 四阶 Boo t h 编码表 得本文所采用的算法达到了四阶 ,部分积数目大大 减少 ,同时采用新型的 422 和 322 压缩器对部分积 进行压缩 ,最后通过一个改进的 134 位的 K 2S 超长 加法器得出乘积.由于在 8087 数学协处理器内部数据通路是 67位 ,作为配套的内部乘法器 ,本文乘法器的位宽也是 67 位 .二进制代码部分积二进制代码部分积0000 (0) 0000 (1) 0000 (0) 0000 (1) 0010 (0) 0010 (1) 0011 (0) 0011 (1) 0100 (0) 0100 (1) 0101 (0) 0101 (1) 0110 (0) 0110 (1) 0111 (0) 0111 (1)0 M 1000 (0) 1000 (1) 1001 (0) 1001 (1) 1010 (0) 1010 (1) 1011 (0) 1011 (1) 1100 (0) 1100 (1) 1101 (0) 1101 (1) 1110 (0) 1110 (1) 1111 (0) 1111 (1)- 8 M - 7 M - 7 M - 6 M - 6 M - 5 M - 5 M - 4 M - 4 M - 3 M - 3 M - 2 M - 2 M - M - M 0 M+ + M M + 2 M + 2 M + 3 M + 3 M + 4 M + 4 M + 5 M + 5 M + 6 M + 6 M + 7 M + 7 M + 8 M1 改进的 B ooth4 编码Boo t h 算法每次扫描连续的几位乘数 , 形成一个有符号的部分积来减少乘法中的部分积的数目 , 随着 Boo t h 编码的阶数 n 的增加 ,部分积的数目会 以因子 1/ n 减 少[ 3 ]. 所以 , 采 用越 高 阶的 Boo t h 算法 ,越有可能得到快速的乘法器.Boo t h 算法在软硬件实现上被广泛的应用 , 特别是高阶的 Boo t h 算法 能够 显 著减 少部 分积 的 数 目 ,从而使部分积相加的延时和压缩部分积阵列的 面积大大减少. Boo t h 算法能够应用于有符号数 ,也可应用于二进制补码而不需要额外的修正[ 526 ].本文采用改进的四阶 Boo t h 算法 ,一个 n 位的 二进制补码的改进四阶 Boo t h 编码可以表示成 :n- 2表 1 给出了每次扫描五位乘数以及其对应部分积相对于 M 的倍数 ( M 表示被乘数) . 在 67 位的四 阶 Boo t h 编码电路中 ,将乘数的最低位补一位零 ,最 高位补一位零 ,每个 Boo t h 编码电路输入 a , b , c ,d ,e 表示从高到低的 5 位 2 进制数 ,产生 N E G 、B0 、 B1 、B2 、B3 、B4 、B5 、B6 、B7 、B8 十个信号 ,如果 N E G为 1 ,则表示此部分积为负数 ,否则为正数 . B0 ~B8 表示 0 到 8 倍 M 的部分积. 电路图如图 1 .x n - 1 (2) n- 1 +∑x i2i= 2n- 4( - 23 x n - 1 + 22 x n - 2 +X = - i = 02 x n -3 + x n -4 + x n -5 ) + 2n- 8( - 23x n - 5 + 22x n - 6 + 2 x n - 8 +(1)x n- 9 ) +图 1 四阶 Boo t h 编码电路提前产生 ,即图 2 中的 G enerate Di fficult Multiplier s模块. 从图 2 中可以看出 , G enerate Difficult Multipli 2 2 部分积的产生对于高阶的 Boo t h 算法 ,其难点在于产生一些 不能由简单的左移来产生的部分积 . 例如对于三阶 的 Boo t h 算法 , ±3 M (3 倍的被乘数) 是难于产生的 部分积 ,而 ±2 M 和 ±4 M 则可以通过左移来产生 . 对于四阶的 Boo t h 算法 ,难于产生的部分积数目大大增加 ,有 ±3 M , ±5 M , ±6 M , ±7 M ,如果用文 献 [ 1 ]中的方法来实现这些部分积 ,其面积的增大和 延时的增加是不能忍受的.本文将难于产生的 ±3 M 、±5 M 、±6 M 、±7 Mer s 模块和 B oot h 编码电路是并行的 ,有利于提高速 度. 将产生部分积的电路分为两个模块 ,有利于降低 前一级的负载 ,减小延时. 在 DC 综合后可以看到 ,这 样做后尺寸很大 、延时很大的管子将会被避免 ,有利 于缩短关键路径的时间 ,提高工作频率.如图 2 ,本 文 共 有 17 个 部 分 积 和 3 个 补 偿 向 量 ,共 20 个压缩部分积 , ±2 M 、±4 M 、±8 M 可以 通过对 M 的移位直接产生 ,对于难于通过移位产生 的部分积则需要由{ M 、2 M , 4 M , 8 M }中的某两个产第 4 期康潇亮 , 雷绍充等 :67 ×67 位乘法器的改进四阶 Boo t h 算法实现 1429生 . 3 M 由 2 M 加上 M 产生 ,5 M 由 4 M 加上 M 产 生 ,6 M 由 4 M 加上 2 M 产生 ,7 M 由 8 M 减去 M 产生.由相加 (减法也被转化为加法) 产生的部分积均 需要一个 70 位的超长加法器 ,如果用常规 C L A 或 者 B 2 K 或者 K 2S 加法 器来 完成 , 其 延 时 都 是 很 大 的 . 所以在本文中采用分段相加 ,将进位保留的办法 冗余的表示部分积 ,如图 3 :图 2 乘法器流程图图 3 部分积的冗余表示我们用 3 个改进的 16 位 K 2S 加法器和一个改 进的 22 位 K 2S 加法器来完成 70 位的加法 .在每个加法器之间没有进位信号 ,而是将进位 信号引出来 ,冗余的表示和 . 如图 4 :和 322 压缩器.422 压缩器 在高 速 的乘 法器 中被 广 泛的 应用 , 因为其有规律的互联引线 ,在构建互连复杂程度较 低的 Wallace 树结 构 上 , 422 压 缩器 是 较 理 想 的 部 件[ 8 ] . 传统 422 压缩器输入与输出的逻辑关系表达 式为 :( I 1 © © © I 4 ) © (2) S = I 2 I 3 C inC = ( I 1 © I 2 © I 3 © I 4 ) ·C i n + ( I 1 © I 2 © I 3 © I 4 )(3) (4), C 是 输+ ( I 1 ·I 2 + I 3 ·I 4 ) C o ut = ( I 1 + I 2 ) ·( I 3 + I 4 )图 4 冗余表示部分积图 4 中 , C o ut 表示紧邻低位加法器的进位 , S 15 ~S 0 表示当前加法器的和 .为了能够满足冗余的和取反时只是给每一位取其中的 I , I , I , I , C 是输 入 , S , C 1 2 3 4 in o ut 出 . 该结构的缺点是 S 与 C 的到达时间不一样. 对式 (5) 、(6) 进行逻辑等价变换得 : ( I 1 © © © I 4 ) ·C in C = I 2 I 3 +反 ,还需要再加上一个 70 位的偏移量 0 0 1 0 0( I 1C o ut ©= © © © I 4 ) ·I 4(5)(6)I 2( I 1 I 3 0 0 00 0 0 10 0 0 0 00 0 0 1 0 0I 2 ) ·I 3 + ( I 1 © I 2 ) ·I 10 0 0 0 0 0 ,偏移量的构成规则为 : 在与 C o u t 权值相同的列加 1 ,其余地方为零. 通过一个全加器将s 0 、C o ut 和 1 压缩为和 x 和进位 y.这样 ,我们就实现了冗余的表示部分积 ,包含两 个数据 ,一个 70 位的数据和四个进位信号 . 将每一 个部分积产生的 4 个进位信号 ( 17 个部 分积 共 68 个) 和每一个部分积的偏移向量 (共 17 个 70 位的偏 移向量) 按权值的不同组合成 3 个压缩部分积在压 缩阵列中被压缩.变换后的电路可由异或门和 221 的数据选择器 构成[ 10 ],新结构缩短了关键路径的延时 ,并使 S 与C 的到达时间一致 .322 压缩器同 422 压缩器相比较 ,互连线更简单 ,面积和延时更小 ;522 压缩器同 422 压缩器相比 ,虽然 延时相当 ,但面积几乎增加一倍 ,并且其互连引线更 加复杂 ,不利于 Wallace 树的布局布线. 基于对本文乘 法器部分积的优化压缩以及降低 Wallace 树的布局布 线难度 ,缩短延时 ,在本文中选择使用新型的 422 和322 压缩器相结合压缩部分积 ,采用了图 2 中的流程图 ,达到了比较理想的效果. 表 2 是 422C o m p r esso r 、322 C o mp r e s so r 和 522C o mp r e s so r 面积和时延比较 表[ 8 ,10 ] .3 压缩阵列压缩阵列占用了乘法器绝大部分面积 ,因此提 高压缩效率 ,减小压缩面积成为提高乘法器性能的 主要途径 ,常用的压缩器有 522 压缩器 、422 压缩器1430 电 子 器 件第 30 卷表 2 不同 C o m p r e s so r 的性能比较 允许对一个块的位进位组合进行运算 :( G , P ) ·( G ’ , P ’) = ( G + PG ’ , P P ’)(11)压缩器延时/ n s面积/μm 2故 ( G 30 , P 30 ) = ( G 3 , P 3 ) ·( G 2 , P 2 ) ·( G 1 , P 1 ) ·( G 0 , P 0 ) = ( G 3 :2 , P 3 :2 ) ·( G 2 :0 , P 2 :0 ) . 点操作服从结合律 ,但不服从交换律.本文采用的改 进 型的 K 2S 加法 器实 现 134 位 加法如图 5 :322C o m p r e s so r 422C o m p r e s so r0 . 37 0 . 63 76 . 507 202 159 . 667 206 522 C o m p r e s so r 0 . 57 302 . 702 393超长加法器由于 6767 位的乘法器需要一个 134 位的加法 器 ,加法器的延时成为整个乘法器的瓶颈 . 本文采用 的加法器是改进的 K 2S 加法器 .在设计更快速的加法器时 ,避免逐级进位效应 至关重要 . 超前进位原理提供了一种有可能解决这 一问题的方法. 在 N 位加法器中每一位的位臵上都 存在下列关系[ 11 ] :4 图5 改进的 134 位 K 2S 加法器(7)C o , k = f ( A k , B k , C o , k - 1 ) = G k + P k C o , k - 15 实验和结果本文采用 TSMC0. 18μm 的工艺库 ,综合工具采用通过展开 C o , k - 1 可以消除 C o , k 对 C o , k - 1 的依赖 关系 :Synop s ys 公司的 Design com piler 工具和 Altera 的 Qu 2 art u s4. 2 实现对乘法器的综合和 FP G A 实现.表 3 为本文采用的改进型的 K 2S134 位加法器 和传统的 134 位超前进位加法器在所给工艺库条件 下的综合结果 ,从表中可以看出 ,改进型的 K 2S134 位加法器在延时上比传统的 134 位超前进位加法器 快约 20 . 32 %.表 3K 2S 加法器和超前进位加法器性能比较 (DC 综合) (8)C o , k = G k + P k ( G k - 1 + P k - 1 C o , k - 2 ) C o , k 的完全展开为 :C o, k = G k + P k ( G k- 1 + P k- 1 (+ P 1 ( G 0 + P 0 C i ,0 ) ) ) (9) 研究这一加法器的细节电路图时就会很清楚的 发现 ,真正加法器的延时至少会随位数 N 呈线性增 加 ,而不可能做到与位数无关 . 公式 (10) 建议的超前结构只有在 N 值较小 ( Φ4) 时有良好的性能 . 本文 选用 N = 4 和改进的 K 2S 算法相结合.C o , 1 = G 0 + P 0 C i , 0延时/ n s面积/μm 2加法器C o , 3 = G 1 + P 1 G 0 + P 1 P 0 C i , 0 = ( G 1 + P 1 G 0 ) ( P 1 P 0 ) C i , 0 = G 1 :0 + P 1 :0 C i , 0C o , 2 = G 2 + P 2 G 1 + P 2 P 1 G 0 + P 2 P 1 C i , 0 = ( G 2 134 位超前进位加法器134 位改进的 K 2S 加法器 5 . 07 17583 . 343750+ 4 . 04 14456 . 538086表 4 为 本 文 和 De s ign W a r e 自 带 的 乘 法 器 在DC 综合下性能的比较 . 本文算法无论在面积还是时延上均占优 .+P 2 G 1 + P 2 P 1 G 0 ) + ( P 2 P 1 P 0 ) C i , 0 = C 2 :0 + P 2 :0 C i , 0( 10)表 4 不同方法性能比较 (67 位宽) C o , 3 = G 3 + P 3 G 2 + P 3 P 2 G 1 + P 3 P 2 P 1 G 0 P 3 P 2 G 1 ++ ( G 3 P 3 P 2 P 1 P 0 C i , 0 = + P 3 G 2 + 算法延时/ n s面积/μm 2P 3 P 2 P 1 G 0 ) + ( P 3 P 2 P 1 P 0 ) C i , 0 = G 3 :0 + P 3 :0 C i , 0在公式 (12) 中 ,进位传播过程被分解成为两位的 子组合. C i : j 和 P i : j 分别表示一组位的进位产生和进位 传播函数. 我们称之为块进位产生和块进位传播信号.引入新的布尔运算 ,称为点操作 ( ·) ,这一操作 Design Wa r e改进的 Boo t h 4 算法15 . 58 10 . 85589943 . 812500 375625 . 937500为了考虑布局布线的影响 ,将以上两种乘法器 的网表在 A lt e ra 的 F P G A 上实现 ,采用 Cyclo n e 的EP1C20 F 400C8 . 表 5 为其性能对比.表 5 考虑布线的各算法的 F P G A 实现算法To t a l cell delay/ n s To t al int erco n nect delay/ n sTo t al delay/ n s To t al lo g ic element s33 . 201 (21 . 45 %) 26 . 833 (21 . 32 %)121 . 584 (78 . 55 %) 99 . 033 (78 . 68 %)Design Wa r e改进的 Boo t h 4 算法154 . 785 125 . 8669 ,227 10 ,792实验结果分析6 本文算法和 De s i g n W a r e 乘法器性能的比较 :第 4 期康潇亮 , 雷绍充等 :67 ×67 位乘法器的改进四阶 Boo t h 算法实现 1431(1) 在只追求速度的前提下 ,DesignWare 最快的乘 法器延时在 DC 里为 15. 58 ns ,面积为 589 943. 812 500μm 2 ;而本文算法在综合考虑面积和速度的情况下 ,延时为 10. 85 ns ,面积为 375 625. 937 500μm 2;这说明 ,本文算 法在不考虑布局布线的情况下较 DesignWare 提供的乘法器性能占优.A H . A No vel Co valent Redunda nt Bi na r y Boot h Enco der [J ] . 2005 , I E E E. Faroo qui Aa mi r A , O klo bdzija Voji n G. Sait Sadi q M. A rea 2 Ti me Op ti mal Adder Wit h Relati ve Place ment G enerato r [ J ] . 2003 , I E E E.Villeger D and O klo bdzija V G , Eval uat io n of Boo t h Enco di ng Techni ques f o r Pa rall el Mul t iplier Impl e ment a t io n [ J ] . EL EC 2TRON ICS L E T T ERS , 11t h No ve mber 1993 , 29 ( 23) .罗莉 ,胡守仁. 一个并行高速乘法器芯片的设计与实现[J ] . 计算机工程与科学 ,1997 ,11 ,19 ( 4) .Hi ro shi Ma ki no , Y a suno bu Na ka se , Hi r oa ki Suzu ki , Hi r o yuki Mo ri na ka , Hi rof umi Shi no ha ra , a nd K oichi ro Ma shi ko , Mem 2 ber , I EE E. A n 8 . 82ns 54 x 542Bit Mul tiplier wit h H i gh Sp e e d Redunda nt Bi na r y A rchit ect ure . I EE E J O U RN AL O F SOL ID 2 S TA T E CIRCU I TS ,J U N E 1996 ,31 ( 6) .Ma rti n Ma r gala a nd Dur dle Nel so n G . Lo w 2Po w er Lo w 2Vol t 2age 422 Co mp re sso r f o r VL SI Applicatio n s. Radha kri shna n D , Preet hy A P . Lo w Po wer CMO S Pa ss Lo gic 422 Co mp re sso r f o r Hi gh 2S peed Mul tiplicatio ns [ C ] / / Ci rcuit s a nd Syst e ms. Proceedi ngs of t he 43 r d I EE E Mi dwe st Sympo si 2 u m L an si ng , M I. : 2000 , 3 , 1296 ∃ 1298 . Cha ng Chip 2Ho ng , G u J ia ngmi n , Zha ng Mi ngya n . Ul t r a Lo w 2Vol t age Lo w 2Po wer CMO S 422 a nd 522Co mp resso r s f o r Fa st A rit h metic Ci rcuit s [ J ] . I E EE T RA N SA C TION S ON CIRCU I TS A ND S Y S T EMS —I : R E GUL A R PA P ERS ,OC TOB ER 2004 ,51 ( 10) .Ra baey J a n M , A na nt ha Cha ndra ka sa n , Bo ri voje Ni kolic . Di gt al Int egrat ed Ci rcui t s A De si gn Per spect i ve [ M ] . ( Se c 2 o nd Editio n ) : 5782581 . Pea r so n Educatio n A sia Li mit ed a nd Tsi ng Hua U ni ver s it y Pre ss ,2004 .[ 4 ][ 5 ] (2) 为了考虑布局布线的影响 ,将本文乘法器 [ 6 ] 的网表和 De s i g n W a r e 乘法器的网表输入 A lt e ra 的 Cyclo n e 的 EP1C20 F 400C8 内核 , 在 L e s 几 乎 相 等 前提下 , 本文算法的延时特性比 De s i gn W a re 提 供 乘法器的特性要提高约 18 . 7 %.[ 7 ]结论本文采用 Boo t h4 算法 ,部分积数目显著减少 ,在部分积的产生和压缩阵列 ,以及最后的超常加法 器做了优化和改进后 ,与低阶的 Boo t h 算法和冗余 的 Boo t h 算法相比 ,压缩阵列的面积和延时显著减 小 ,超长加法器的性能显著提高 ,达到了比较理想的 性能要求 ,可以作为高速乘法单元应用于微处理器 和数字信号处理芯片中 .7 [ 8 ] [ 9 ][ 10 ]参考文献 :[ 11 ][ 1 ] 邹刚 , 邵志标 , 赵宁 , 许 琪. 32 位嵌入 式定/ 浮点乘 法器 设计 [J ] . 微电子学与计算机 ,2004 ,21 ( 8) .傅志晖 ,程东方 ,梅其元 ,李娇 , 薛忠杰 ,吴鼎祥. 32 位浮点阵列乘法器的设计及算法比较[J ] . 微电子学 , 2003 ,6 ,33 ( 3) .He Y aj ua n , Cha ng Chip 2Ho ng , G u J ia ngmi n , Fa h my Ho ssa m[ 2 ] [ 3 ] (上接第 1422 页)由于双谱能很好地抑制噪声 ,能充分地获取了隐含 在数据中的信息 ,本文主要采用基于非高斯 A R 模 型的双谱估计方式 . 同时考虑到双谱估计比现代谱 估计的运算量大 ,在实际的信号测量过程中 ,我们还 采用了双通道检测方式 ,在小信噪比情况下选择使 用双谱检测 ,在大信噪比情况利用现代谱分析的方 式 ,不仅很好地解决了小信噪比情况下 F S K 信号频 率检测的问题 ,而且尽可能地减少了运算量. 参考文献 :t r u m Esti matio n . Aco u stics[ C ] / / S peech , a n d S i gnal Process 2 i n g , I E EE Int er natio nal Co nf erence o n ICA S SP apo s ; Ma r1984 ,84 ( 9) : 1202123 .L u ki n V V . To t sky A V . K ure ki n A A . K ur bat o v I V . A stolaJ T. Egiaza ria n K O . Si gnal Wavef o r m Reco nst r uct io n f r o m Noi sy Bi sp ect r um Esti matio n s p re 2Proce ssed by Vecto r Fil 2 t er s . S i gnal Proce ssi ng a nd It s Applicatio n s [ C ] / / 2003 . Pro 2 ceedi ngs. Sevent h Int er nat io nal Sympo si u m o n Vol u me 2 , Is 2 sue , 124 ,J ul y 2003 : 1692172 . K let t er D. Me sser H . Subop ti mal Det ectio n of No n G a u ssia n Si gnal s by Thi r d Or der Spect ral A nal ysi s [ J ] . I EE E Tra n s o n A S SP . 1990 ,38 ( 6) :901 .徐岩 ,罗冠炜 ,低信噪比弱信号提取算法研究 [ J ] . 甘肃工业大 学学报 ,2003 ,9 . 邢晓异 ,仲新莉 , FS K 信号检测的高分辨率实现方法[ J ] . 华东交通大学学报 ,2000 ,9 .樊养余 , 孙进才等 , 基于双谱的谐波信号重构 [ J ] . 声学学报 ,1999 ,7 .邓革 ,陈怒兴 ,超宽带雷达回波的双谱分析方法 [ J ] . 国防科技大学学报 ,1997 ,6 .[ 4 ] [ 5 ][ 6 ] [ 1 ] Er de m A T. Te kalp A M. Li nea r Bi sp ect r u m of Si gnal s and I 2dent i f icat io n of No nmi n i mu m Pha se F IR Syst em s Dri ven by Colo red Inp ut [ J ] . I EEE Tran sactio n s o n Aco ust ics , Sp eech ,a nd Si gnal Proce ssi n g , J un 1992 40 ( 6) :146921479 . [ 2 ]K u sumop ut ro B . Tri ya nto A . Fana ny M I. J at mi ko , W. Spea ker Identi f i catio n i n Noi sy Envi ro n ment U si ng Bi sp e c t r u 2 ma nal ysi s a nd Pro ba bili stic Neural Net wo r k . Co mp ut atio na l Int elli gence a nd Mul ti media Appli catio n s [ C ] / / 2001 . ICCIMA 2001 . Proceedi ngs. Fo u r t h Int e r natio nal Co nf e rence o n Vol 2 ume , Issue , 2001 : 2822287 .[ 3 ] Raghuveer , M. Ni k ia s , C A Pa r a m et ric App r o ach to Bi s p ec 2[ 7 ] [ 8 ] [ 9 ] [ 10 ] 林品兴 ,毛士艺 ,张朝阳 ,高斯噪声中非高斯弱信号的双谱检测[J ] . 航空学报 ,1993 ,7 .。

基于修正Booth算法的实用型移位式二进制乘法器电路

算数运算电路扩展实验(基于修正Booth算法的实用型移位式二进制乘法器电路)1、电路功能设计一个16-bit的移位式乘法器电路,要求:(1)采用修正Booth算法产生部分积;(2)采用右移部分积之和的部分积求和累加方式;(3)结果乘积寄存器为32-bit。

2、电路设计(1)电路设计方案整体框图将电路分为6个子模块进行独立的设计,最后在采用一个顶层模块将之综合起来,6个子模块分别:①部分积产生电路:设被乘数为x,该电路功能是产生0,x,2x,并且x要进行符号位扩展。

②加减法器电路该加减法器为17bit的加减法器,能够由Booth译码产生的控制信号en_add来控制进行加法运算还是减法运算(高电平为加法,低电平为减法),将结果送给乘积寄存器的左半部分。

③Booth译码产生电路通过乘数y右移2位,与之前保留的一位,总共三位构成译码电路的输入,最终将译码结果送给MUX8_3选择器,让其选出正确的部分积(0,x,2x)来参与下次的加法运算,同时Booth译码电路还产生一位控制加法器电路的控制信号en_add。

④MUX数据选择器该MUX选择电路是通过译码电路产生的译码信号来选择下一步所需的部分积(0,x,2x)。

⑤乘数y的右移电路先给y最高位和最低位均补0,然后每个时钟上升沿到来,将之右移2位,在通过内部控制信号,向右移9次。

⑥部分积之和右移电路将加法器产生的输出放在其高16位,同时进行右移2位操作,并进行符号位的扩展。

然后再将移位后的高16位送给加法器的被加数端,进行下一次的部分积求和,再通过内部控制信号,控制其向右移9次,最终得到正确的乘积。

(2)电路设计①部分积的产生电路module Creat_part_pro(input [15:0] x,output reg [16:0] x_0,output reg [16:0] x_1,output reg [16:0] x_2);always@(*)beginif (x[15])beginx_0 = 17'b0;x_1 = {1'b1,x};x_2 = {x<<1};endelsebeginx_0 = 17'b0;x_1 = {1'b0,x};x_2 = {x<<1};endendendmodule电路说明:x:输入的16位被乘数x_0: 输出0x_1:输出x,并进行符号位扩展x_2:输出2x②加减法器module Add(input rst_n,input en_add,//高为加法,低位减法input [16:0] add1,input [16:0] add2,output reg [16:0] part_sum//部分积之和,送往移存器);always @(*)beginif (!rst_n)part_sum = 17'b0;else if(en_add)part_sum = add1 + add2;elsepart_sum = add2 - add1;endendmodule电路说明:add1:被加数add2:加数en_add:加减控制信号(高为加,低为减)part_sum:输出和③数据选择器module Mux_3_1(input [16:0] x_0,//产生的0,X,2Xinput [16:0] x_1,input [16:0] x_2,input [2:0] en_x,//译码产生的控制信号output reg [16:0] addx_i ///送往加法器,与部分积之和相加);always @(*)begincase (en_x)3'b010 : addx_i = x_2;default : addx_i = x_0;endcaseendendmodule电路说明:x_i :分别是电路①产生的0,x,2xenx:选择控制信号,由Booth译码电路产生addx_i:输出送往加法器④Booth译码电路module Booth_encode(input [2:0] y_n,//乘数y的三位需要译码output reg [2:0] en_x,output reg en_add //决定加法器加减,高加低减);always@(*)begincase (y_n)3'b000 : en_x = 3'b000;3'b001 : en_x = 3'b001;3'b010 : en_x = 3'b001;3'b011 : en_x = 3'b010;3'b100 : en_x = 3'b010;3'b101 : en_x = 3'b001;3'b110 : en_x = 3'b001;3'b111 : en_x = 3'b000;default : en_x = 3'b000;endcaseendalways@(*)begincase(y_n)3'b000 : en_add = 1'b1;3'b001 : en_add = 1'b1;3'b010 : en_add = 1'b1;3'b011 : en_add = 1'b1;3'b100 : en_add = 1'b0;3'b101 : en_add = 1'b0;default : en_add = 1'b1;endcaseendendmodule电路说明:y_n:由y产生的三位译码输入en_x:译码电路的输出,送往数据选择器en_add:送往加法器,决定加减⑤乘数y右移电路module Shift_y_right_2bit(input clk,input rst_n,input [15:0] y,output reg [2:0] encode_in);reg [3:0] shift_cnt;wire en_shift;always@(posedge clk or negedge rst_n)beginif (!rst_n)beginshift_cnt <= 4'b0000;endelse if (shift_cnt == 4'b1001)shift_cnt <= 4'b0000;elseshift_cnt <= shift_cnt + 1'b1;endassign en_shift = (shift_cnt == 4'b1001) ? 1'b0 : 1'b1;reg [17:0] y_r;always@(posedge clk or negedge rst_n)beginif (!rst_n)beginy_r <= 18'b0;encode_in <= 3'b000;endelse if(en_shift)beginencode_in <= {y_r[2:0]};y_r <= y_r >> 2;endelsebeginy_r <= {1'b0,y,1'b0};endendendmodule电路说明:clk:系统时钟rst_n:系统复位信号y:乘数encode_in:产生的译码,送往Booth译码器shift_cnt:移位计数器en_shift:允许移位标志⑥求积电路module Creat_product(input clk,input rst_n,input [16:0] part_pro,output reg [32:0] product);reg [3:0] shift_cnt;wire en_shift;always@(posedge clk or negedge rst_n)beginif (!rst_n)beginshift_cnt <= 4'b0000;endelse if (shift_cnt == 4'b1001)beginshift_cnt <= 4'b0000;endelsebeginshift_cnt <= shift_cnt + 1'b1;endendassign en_shift = (shift_cnt == 4'b1001) ? 1'b0 : 1'b1;always@(posedge clk or negedge rst_n)beginif (!rst_n)beginproduct <= 33'b0;product[32:16] <= 17'b0;endelse if(!en_shift)beginproduct <= 33'b0;product[15:0] <= 16'b0;endelsebeginproduct <= {product[32],product[32],product[32:2]}; product[32:16] <= part_pro;endendwire [32:0] product_test;assign product_test = {product[32],product[32],product[32:2]}; endmodule电路说明:clk:系统时钟rst_n:复位信号part_pro:部分积之和,由上述的加法器电路产生product:输出积(此处由于时序问题,并不是正确的乘积)shift_cnt:移位计数器en_shift:允许移位标志product_test:经过仿真,这个才是正确的乘积⑦顶层模块module Booth_16bit_TOP(input clk,input rst_n,input [15:0] x,input [15:0] y,output [32:0] product);wire [16:0] x_0;wire [16:0] x_1;wire [16:0] x_2;Creat_part_pro U_Creat_part_pro //部分积产生模块(.x (x),.x_0 (x_0),.x_1 (x_1),.x_2 (x_2));wire [2:0] encode_in;wire [2:0] en_x;wire en_add;Booth_encode U_Booth_encode //Booth译码电路产生模块(.y_n (encode_in),.en_x (en_x),.en_add (en_add));Shift_y_right_2bit U_Shift_y_right_2bit //右移y产生译码信号(.clk (clk),.rst_n (rst_n),.y (y),.encode_in (encode_in));wire [16:0] addx_i;Mux_3_1 U_Mux_3_1 //选择加x,还是2x(.x_0 (x_0),.x_1 (x_1),.x_2 (x_2),.en_x (en_x),.addx_i (addx_i));wire [16:0] part_sum; ///部分积产生模块Add U_Add(.rst_n (rst_n),.en_add (en_add),.add1 (addx_i),.add2 ({product[32],product[32],product[32:18]}),.part_sum (part_sum));Creat_product U_Creat_product //积的产生(.clk (clk),.rst_n (rst_n),.part_pro (part_sum),.product (product));endmodule电路说明:将之前的六个模块联系起来,形成一个完整的乘法器电路。

booth算法浮点乘法器

booth算法浮点乘法器(原创版)目录1.Booth 算法简介2.Booth 算法的原理3.Booth 算法的实现4.Booth 算法的应用5.Booth 算法的优缺点正文1.Booth 算法简介Booth 算法是一种用于计算机中浮点数乘法的算法,它可以提高计算机中浮点数乘法的运算速度。

在计算机科学中,浮点数乘法是一个非常重要的运算,因为许多科学计算和工程应用都需要进行大量的浮点数乘法运算。

2.Booth 算法的原理Booth 算法的原理是减少乘法过程中所需的乘法次数。

在传统的浮点数乘法中,我们需要进行多次乘法运算才能得到最终的结果。

而 Booth 算法通过观察两个数的小数点位置,可以减少乘法次数,从而提高运算速度。

3.Booth 算法的实现Booth 算法的实现过程可以分为以下几个步骤:(1) 观察两个数的小数点位置,确定它们的乘积的小数点位置。

(2) 根据小数点位置,将两个数分成整数部分和小数部分。

(3) 对整数部分进行乘法运算,得到一个中间结果。

(4) 对小数部分进行乘法运算,得到最终的结果。

4.Booth 算法的应用Booth 算法广泛应用于计算机科学中,它可以提高计算机中浮点数乘法的运算速度。

Booth 算法不仅可以用于普通的浮点数乘法,还可以用于大量的并行计算中,进一步提高运算速度。

5.Booth 算法的优缺点Booth 算法的优点是可以减少乘法次数,提高运算速度。

与传统的浮点数乘法相比,Booth 算法可以大大提高运算速度,特别是在大规模数据处理中。

Booth 算法的缺点是它的实现过程比较复杂,需要进行多次条件判断和指针操作。

booth8乘法器实验

8位booth乘法器设计实验一、实验分析:4 位位宽:A=7(0111),B=2(0010)。

A = (7) 0000 0111;2A = (14) 0000 1110;-2A = (-14) 1111 0010。

在这里我们必须注意一下当B[1:-1] 等于011 或者100 的时候,4 位的被乘数A 的取值范围最大是-7 ~ 7 然而,+2(被乘数) 或者-2(被乘数) 都会使得A 的最大值突破取值范围。

所以需要从4 位位宽的空间向更大的位位宽空间转换。

这里就选择向8 位位宽的空间转换。

B 乘数加码为B[1:-1] = 3'b100 ,亦即-2(被乘数) 和B[3:1] = 3'b100 ,亦即+被乘数。

二、实验所需程序:module booth8(A,B,clk,product);input [7:0] A,B;input clk;output [15:0] product;reg [3:0] i;reg [15:0] a;reg [15:0] a2;reg [15:0] s;reg[15:0] s2;reg [15:0] p;reg [3:0] M;reg [8:0] N;reg [15:0] p1;always @(posedge clk)begini <= 4'd0;case(i)0:begina <= A[7] ? { 8'hFF , A } : { 8'd0, A };a2 <= A[7] ? { 8'hFF ,A + A} :{ 8'd0,A + A };s <= ~A[7] ? { 8'hFF , (~A + 1'b1 )} : { 8'd0 ,( ~A + 1'b1 )};s2 <=~A[7] ? {8'hFF , ( ~A + 1'b1 ) + (~A+1'b1)} : { 8'd0 , (~A + 1'b1) + (~A + 1'b1)};p <= 16'd0;p1<=16'd0;M <= 4'd0;N <= { B , 1'b0};i <= i+ 1'b1;end1,2,3,4:beginif( N[2:0] == 3'b001 || N[2:0] == 3'b010 ) p <= p+ (a<< M);else if (N[2:0] == 3'b011 ) p <= p+ ( a2 << M );else if (N[2:0] == 3'b100 ) p <= p + ( s2 << M);else if ( N[2:0] == 3'b101 || N[2:0] == 3'b110 ) p <= p + (s << M);M <= M + 2'd2;N <= ( N >> 2);i <= i + 1'b1;end5:beginif(i==5) p1<= p;endendcaseendassign product = p1;endmodule二、实验结果及功能仿真:(下页)功能仿真图可以看到,在得到正确解之前经历了多个时钟,这是因为需要计算四次所致的,本来应该在正确解之前会有三个数值的,为了更好的查看结果,本程序采用屏蔽手段使其前三个值为零了。

基于FPGA的Booth算法乘法器

Booth算法乘法器可以看做是一种“加码”乘法运算。

这是数学角度的Booth算法。

这里的B[-1]是什么意思呢?B的最右边的后面一位就称为B[-1],假设B是2即4’b0010。

加上B[-1]位的效果就是4’b0010_0。

后边这个0是默认的。

实现B[0:-1]时,可以将B 对某个变量赋值,例N<={B,1’b1},此时的N[1:0]就是B[0:-1]。

从数学的角度来看Booth算法是比较麻烦的,需要进行移位相加等操作。

当从位操作的角度来看,Booth算法的优势就可以体现出来。

这是位操作的Booth算法。

设乘数和被乘数都为4位,即n=4。

这里要建立一个P空间,容量为2*n+1,还要将p空间初始化,默认为0;第一步:先用补码的形式表现出-1*被乘数,方便一会儿做减法,将p[4:1]填入乘数B,空出来的p[0]相当于前边的N[0],即为了方便使用B[-1];第二步:判断p[1:0],因为已经将乘数B填入到P[4:1],所以p[1:0]即对应的B[0:-1];判断p[1:0]的值于上表对应,进行相应的操作。

表中提到的加减被乘数,是要在p[2n:n+1]位进行,这个需要注意。

所谓的p空间右移一位,高位需要补充一位。

补充的这一位,要由进行加减被乘数以后的p[8](p[2n])决定,p[8]是1补充1,是0补充0;此步骤循环n次,最后结果取p[8:1];相应核心代码(8位)case(i)0:begin a<=A;s<=(~A+1’b1);p<={8’d0,B,1’b0};i<=i+1’b1;end//a寄存被乘数,s寄存被乘数的补码,对p空间装填乘数B1:If(X==8) begin X<=4’d0;i<=i+1’b2;endelse if(p[1:0]==2’b01)begin p<={p[16:9]+a,p[8:0]};i<=i+1’b1;endelse if(p[1:0]==2’b10)begin p<={p[16:9]+s,p[8:0]};i<=i+1’b1;endelsei<=i+1’b1;在八次循环前对p[1:0]进行判断,然后进行相应的操作(加减被乘数)。

八位二进制乘法器booth

八位二进制乘法器booth八位二进制乘法器Booth是一种快速计算二进制乘法的方法,其原理是将被乘数与乘数一起转化为二进制补码形式,然后进行位移和相加运算,最终得出乘积。

下面我们就来详细了解Booth乘法器的实现流程。

1. 将被乘数和乘数转化为二进制补码形式Booth乘法器的第一步是将被乘数和乘数转化为8位二进制补码形式。

具体来说,要将它们分别转化为8位带符号的二进制数,如果是正数则其二进制与原数相同,如果是负数则其二进制为其绝对值的原码取反加1。

2. 初始化Booth乘法器Booth乘法器的第二步是对其进行初始化。

具体来说,要先在最左侧添加一个0,然后添加8个辅助位,辅助位一般初始化为0。

3. 进行循环,执行移位和加减运算Booth乘法器的第三步是进行循环,每次循环都要进行移位和加减运算。

具体来说,在每一次循环中,都将乘数向右移动一位,并将最后一位的值赋给辅助位。

然后,根据当前乘数的最后一位和辅助位的值,选择加上或者减去被乘数。

4. 得出结果Booth乘法器的最后一步是得出结果。

具体来说,将得到的答案转化为二进制补码形式,然后去掉最左侧辅助位即可得到最终的八位乘积。

除了上述四个步骤外,还有一些细节需要注意。

例如,在进行加减运算时,要先将乘数和被乘数进行符号扩展,将它们分别扩展为一个9位数,扩展时要将第8位的符号复制到第9位。

此外,在进行移位时,要注意移位后最左侧位的值是否为1,如果是1,要进行2次减法。

综上所述,Booth乘法器可以大大加快二进制乘法的运算速度,是一种十分实用的计算方法。

Booth编码在补码乘法中的应用

Booth编码在补码乘法中的应用摘要:在数字信号处理中,乘法器是运算单元的核心部件之一,通过Booth编码减少部分积的数量,能提高乘法运算的速度。

该文分析了优化乘法器的两种思路,推导了2基Booth编码及4基Booth编码,指出在实现乘法器中优先考虑4基Booth编码的原因,阐述了在应用Booth编码时注意的问题,在实际应用中验证了该方案的有效性和稳定性。

关键词:补码Booth编码乘法器在数字信号处理芯片或一般微处理器芯片中,乘法器是芯片的核心之一,是处理器中进行数据处理的关键部件。

乘法器完成一次操作的周期基本上决定了处理器的主频。

乘法器的速度和面积优化对于整个处理芯片的性能来说是非常重要的。

为了加快乘法器的执行速度,减少乘法器的面积,有必要对乘法器的算法、结构及电路的具体实现做深入的研究。

乘法器工作的基本原理是首先生成部分积,再将这些部分积相加得到乘积,如对于补码形式N位有符号数乘法A×B来说,常规的乘法运算会产生N个部分积,这和一般手算乘法的过程没有什么区别。

从乘法器工作的基本原理可以看出,要提高乘法运算的性能,可以从两方面入手,一个是减少部分积的数量,另一个是缩短部分积的相加的运算时间。

在节省部分积相加的运算方面,通常使用3:2CSA(Carry Saved Add)等压缩编码方法。

而该文就是针对第一方面,就如何减少部分积的数量,着重推导Booth编码原理,并简要分析了Booth编码的算法实现中的关键点。

1基和4基Booth编码通过(5)式可以看出,A和B的乘积P,也可以通过对B/-B进行移位相加得到,这就是4基Booth编码,共产生[n/2]个部分积([*]表示向上取整运算)。

从上面的推导过程可以看出,数A还可以进行其他基的Booth 编码等,但是编码复杂度有所增加。

另外,主要考虑到在芯片实现时,出现部分积不是的这种情况,使得部分积不是被乘数左移若干位的情况,这种情况下要在芯片实现增加很多难度。

《乘法器设计报告》word版

有符号乘法器设计报告——VLSI课程设计2010年12月复旦大学专用集成电路与国家重点实验室第一章 设计要求完成16*16有符号乘法器的设计。

具体设计方案选择要求如下:1、 编码方式:non-booth 编码,Booth 编码,Booth2编码(任选一种)2、 拓扑结构:简单阵列,双阵列,二进制树,Wallace 树(任选一种)3、 加法器:Ripple Carry Adder ,Carry bypass ,Carry select ,Carrylook ahead (任选一种或采用混合方法)设计报告必须包含设计方案说明及选择该方案的理由、仿真和设计结构等。

第二章 设计分析在微控制器(MCU )、微处理器(MPU )、数字信号处理器(DSP )、滤波器(FIR/IIR )等各种电路中都会用到乘法器,乘法器是最基本、最重要的运算模块之一。

并且乘法器往往还是处在关键路径上,所以乘法器的性能就显得更加重要。

伴随着现在工艺水平的提高,模块的面积也随着减小,在一定程度下以面积为代价来追求性能的提升,这也是允许的。

本设计是以追求性能为设计目标的,采用全并行的乘法器电路,设计指标设为传播延时为5ns 。

第三章 乘法器原理分析乘法器通常有三种结构形式,全串行乘法器、串并行乘法器以及全并行乘法器。

全串行乘法器都可以是串行的,需要多个时钟周期,速度很慢;串并行乘法器的一个输入是并行的,另一输入是串行的,乘积串行输出;全并行乘法器,输入和输出都是并行的,电路较为复杂,但是速度极快。

本设计追求的就是速度,所以采用全并行乘法器机构。

16位有符号乘法器可以分为三个部分:根据输入的被乘数和乘数产生部分积、部分积压缩产生和和进位、将产生的和和进位相加。

这三个部分分别对应着编码方式、拓扑结构以及加法器。

3.1 编码方式本设计采用booth2编码。

Booth 算法的提出主要是为了解决有符号数乘法运算中的复杂的符号修正的问题,所以采用booth2编码对于补码表示的两数就不需要考虑符号的问题。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

运算器部件实验:Booth乘法器

班级:软件工程

一、实验目的

理解并掌握乘法器的原理。

二、实验原理

Booth算法是一种十分有效的计算有符号数乘法的算法。

算法的新型之处在于减法也可用于计算乘积。

Booth发现加法和减法可以得到同样的结果。

因为在当时移位比加法快得多,所以Booth发现了这个算法,Booth算法的关键在于把1分类为开始、中间、结束三种,如下图所示

当然一串0或者1的时候不操作,所以Booth算法可以归类为以下四种情况:

Booth算法根据乘数的相邻2位来决定操作,第一步根据相邻2位的4中情况来进行加或减操作,第二部仍然是将积寄存器右移,算法描述如下:

(1)根据当前为和其右边的位,做如下操作:

00: 0的中间,无任何操作;

01: 1的结束,将被乘数加到积的左半部分;

10:1的开始,积的左半部分减去被乘数;

11: 1的中间,无任何操作。

(2)将积寄存器右移1位。

因为Booth算法是有符号数的乘法,因此积寄存器移位的时候,为了保留符号位,进行算术右移。

同时如果乘数或者被乘数为负数,则其输入为该数的补码,若积为负数,则输出结果同样为该数的补码。

三、实验步骤

(1)打开QuartusII

(2)将子板上的JTAG端口和PC机的并行口用下载电缆连接,打开试验台电源。

(3)执行Tools→Programmer命令,将booth_multiplier.sof下载到FPGA 中。

(4)在实验台上通过模式开关选择FPGA-CPU独立调试模式010.

(5)将开关CLKSEL拨到0,将短路子DZ3短接且短路子DZ4断开,使FPGA-CPU 所需要的时钟使用正单脉冲时钟。

四、实验现象

五、具体代码实现

端口声明:

port

( clk: in std_logic;

md : in std_logic_vector(3 downto 0);

mr : in std_logic_vector(3 downto 0);

p : out std_logic_vector(8 downto 0);

final: out std_logic );

信号量声明:

signal p_s:std_logic_vector(8 downto 0);

signal counter:std_logic_vector(3 downto 0):="0000"; --counter

具体算法实现如下:

process(clk)is

begin

if(clk'event and clk='1')then --时钟沿到来

if(counter="0000")then

p_s(8 downto 0)<="0000"&mr(3 downto 0)&"0"; --进行初始化操作elsif(counter(0)='0')then

p_s(8 downto 0)<=p_s(8)&p_s(8 downto 1); --计数为偶数时进行移位操作elsif(counter(0)='1')then --计数位奇数是进行加或减操作--由于计算过程中会进行移位操作,所以p_s(1 downto 0)始终表示当前位和当前位的右边--一位

if(p_s(1 downto 0)="10")then

p_s(8 downto 5)<=p_s(8 downto 5)+((not md)+"0001"); --减法操作elsif(p_s(1 downto 0)="01")then

p_s(8 downto 5)<=p_s(8 downto 5)+md(3 downto 0); --加法操作end if;

end if;

if(counter<"1001")then --计数器counter及final输出的操作

counter<=counter+"0001";

elsif(counter="1001")then

final<='1';

counter<="0000";

else

final<='0';

end if;

p<=p_s;

end if;

end process; --进程结束。