19-总线及总线标准(一)

计算机总线标准

计算机总线标准计算机总线标准是指计算机硬件中用于连接各个组件的一组规范和接口标准。

它定义了计算机内部各个组件之间的通信方式和数据传输规则,使得不同厂商生产的计算机硬件能够互相兼容和交互。

计算机总线标准的出现,使得计算机硬件的设计和制造变得更加灵活和高效。

它不仅简化了硬件设计的复杂性,还提高了计算机系统的可扩展性和可维护性。

通过遵循总线标准,计算机硬件可以实现模块化设计,不同的组件可以独立开发和升级,从而降低了硬件的成本和开发周期。

在计算机总线标准中,最常见的是PCI(Peripheral Component Interconnect)总线标准。

PCI总线标准是由Intel公司于1992年推出的,它定义了计算机主板上各个插槽之间的通信规则和电气特性。

通过PCI 总线,计算机主板可以连接各种外部设备,如显卡、声卡、网卡等。

PCI总线标准的出现,使得计算机主板的设计更加灵活,用户可以根据自己的需求选择不同的外部设备,从而提高了计算机的性能和功能。

除了PCI总线标准,还有许多其他的计算机总线标准,如ISA (Industry Standard Architecture)、AGP(Accelerated Graphics Port)、USB(Universal Serial Bus)等。

这些总线标准都有各自的特点和应用领域。

例如,ISA总线标准是早期计算机中使用的一种总线标准,它的传输速度较慢,适用于连接一些低速外部设备。

而AGP总线标准是专门用于连接显卡的一种总线标准,它的传输速度较快,可以满足高性能图形处理的需求。

USB总线标准是一种通用的外部设备连接接口,它的传输速度较快,可以连接各种外部设备,如打印机、键盘、鼠标等。

随着计算机技术的不断发展,计算机总线标准也在不断演进和更新。

例如,PCI总线标准的后续版本PCI Express(PCIe)已经成为现代计算机中最常用的总线标准之一。

PCIe总线标准采用了串行传输的方式,传输速度更快,同时还支持热插拔和多路复用等功能,使得计算机系统更加灵活和高效。

总线的标准

总线的标准包括以下几个方面:

ISA总线:是一种计算机本地总线标准,定义了计算机应如何与低速的I/O设备(如键盘、打印机等)通信。

EISA总线:扩展工业标准体系(Extended Industry Standard Architecture),主要用于286微机。

EISA对ISA完全兼容。

VESA总线:视频电子标准协会(Video Electronic Standard Association),是按照局部总线标准设计的一种开放总线,只适合于486的一种过渡标准,已淘汰。

PCI总线:外围设备互联(Peripheral Component Interconnection),PCI局部总线是高性能的32位或64位总线,它是专门为高集成度的外围部件、扩充插板和处理器/存储器系统而设计的互连机制。

以上就是一些常见的总线标准,如需了解更多信息,请查阅专业书籍或咨询专业人士。

总线与总线标准

率的通信。SerDes技术将广泛应用于各种高速总线和接口协议中,推

动总线技术的发展。

03 总线的应用领域

工业控制领域

实时性要求高

安全可靠性

工业控制领域中,总线需要满足高实 时性要求,确保设备之间的快速通信 和精确控制。

工业控制领域对安全可靠性要求极高, 总线需要具备高度的稳定性和可靠性, 以避免因通信故障导致的生产事故。

灵活性高

总线结构允许节点在总线上任意接入 或断开,提高了系统的灵活性。

总线的缺点

带宽有限

总线的带宽有限,限制了数据 的传输速率。

竞争激烈

多个节点共享总线资源,导致 资源竞争激烈,影响系统性能 。

故障排除困难

一旦总线发生故障,故障排除 比较困难。

对线缆要求高

总线结构的线缆要求较高,需 要高质量的线缆以保证信号传

灵活性

通信领域中,总线需要具 备较好的灵活性,能够适 应不同传输介质和传输距 离的需求。

计算机硬件领域

高速数据传输

计算机硬件领域中,总线需要满 足高速数据传输的要求,确保

CPU、内存、硬盘等硬件设备之 间的快速信息交换。

兼容性

计算机硬件领域中,总线需要遵 循国际通用的标准协议,以确保

不同硬件设备之间的兼容性。

扩展性

计算机硬件技术不断发展,总线 需要具备良好的扩展性,以适应 新的硬件设备和更高的性能要求。

04 总线的优缺点分析

总线的优点

可靠性高

总线结构简单,减少了故障发生的可 能性,提高了系统的可靠性。

可扩展性强

总线采用分支结构,方便增加和减少 节点,具有良好的可扩展性。

成本低

总线结构减少了线缆的使用量,降低 了布线和维护成本。

总线技术与总线标准

汇报人:

单击输入目录标题 总线技术概述 总线标准类型 总线技术的性能指标 总线技术的优势与局限性 总线技术的应用案例

添加章节标题

总线技术概述

总线技术的定义

总线技术通常用于计算机系 统中的各个部件之间的通信

总线技术是一种用于连接和 传输数据的通信技术

总线技术可以包括多种不同 的协议和标准

单击此处添加标题

单位:比特率通常以bps(bits per second)或Kbps(kilobits per second)、Mbps(megabits per second)等表示

单击此处添加标题

性能评估:数据传输速率是总线技术的重要性能指标之一,它直接影响到 系统的整体性能和效率

传输距离

定义:传输距离 是指总线技术能 够传输信号的最 大距离

• CAN总线技术:CAN总线技术是一种广泛应用于汽车、航空航天、工业自动化等领域中的通信协 议。它具有高可靠性、实时性和灵活性等特点,可以实现设备之间的快速数据传输和实时监控。

• LIN总线技术:LIN总线技术是一种低成本的串行通信协议,被广泛应用于汽车、智能家居等领域 中。它具有简单、可靠、低成本等特点,可以实现设备之间的简单数据传输和通信。

传输速度快: 总线技术采用 高速传输协议, 因此具有较快 的传输速度。

灵活性好:总 线技术采用总 线控制方式, 因此具有较强 的灵活性和可

扩展性。

可靠性高:总 线技术采用差 分信号传输方 式,因此具有 较高的可靠性。

局限性

成本较高:总线 技术的硬件成本 相对较高,增加 了整个系统的成 本。

传输距离有限: 总线技术的传输 距离有限,限制 了其在大型系统 中的应用。

总线技术的应用领域

第4章 总线技术与总线标准

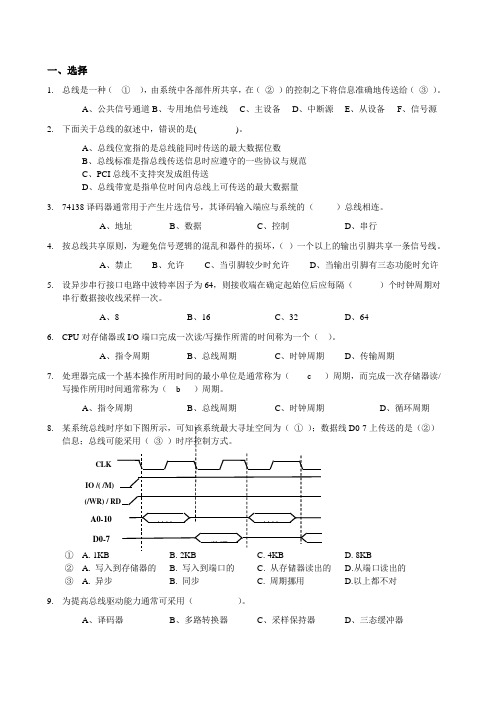

一、选择1. 总线是一种( ① ),由系统中各部件所共享,在( ② )的控制之下将信息准确地传送给( ③ )。

A 、公共信号通道B 、专用地信号连线C 、主设备D 、中断源E 、从设备F 、信号源2. 下面关于总线的叙述中,错误的是( )。

A 、总线位宽指的是总线能同时传送的最大数据位数B 、总线标准是指总线传送信息时应遵守的一些协议与规范C 、PCI 总线不支持突发成组传送D 、总线带宽是指单位时间内总线上可传送的最大数据量3. 74138译码器通常用于产生片选信号,其译码输入端应与系统的( )总线相连。

A 、地址B 、数据C 、控制D 、串行4. 按总线共享原则,为避免信号逻辑的混乱和器件的损坏,( )一个以上的输出引脚共享一条信号线。

A 、禁止B 、允许C 、当引脚较少时允许D 、当输出引脚有三态功能时允许5. 设异步串行接口电路中波特率因子为64,则接收端在确定起始位后应每隔( )个时钟周期对串行数据接收线采样一次。

A 、8B 、16C 、32D 、646. CPU 对存储器或I/O 端口完成一次读/写操作所需的时间称为一个( )。

A 、指令周期B 、总线周期C 、时钟周期D 、传输周期7. 处理器完成一个基本操作所用时间的最小单位是通常称为( c )周期,而完成一次存储器读/写操作所用时间通常称为( b )周期。

A 、指令周期B 、总线周期C 、时钟周期D 、循环周期8. 某系统总线时序如下图所示,可知该系统最大寻址空间为( ① );数据线D0-7上传送的是(②)信息;总线可能采用( ③ )时序控制方式。

① A. 1KB B. 2KBC. 4KBD. 8KB② A. 写入到存储器的 B. 写入到端口的 C. 从存储器读出的 D.从端口读出的 ③ A. 异步 B. 同步 C. 周期挪用 D.以上都不对9. 为提高总线驱动能力通常可采用( )。

A 、译码器B 、多路转换器C 、采样保持器D 、三态缓冲器地址数据地址CLK IO /( /M) D0-7A0-10 (/WR) / RD10.通常来说,同种总线上的数据传送速率与距离成( )。

总线

21

2、分布式仲裁

分布式仲裁方式没有独立的总线控制器,总线上每个 主设备都有自己的总线仲裁逻辑。每次总线仲裁都由 各个设备的总线仲裁逻辑根据一定的仲裁算法来决定 自己是否占用总线。 常用的分布式仲裁方式分为: ① ② ③ 自举分布式仲裁 冲突检测分布式仲裁 并行竞争分布式仲裁

22

①自举分布式仲裁

5

二、总线的分类

3. 按总线的通信定时方式分类

① 同步总线:指互联的部件或设备均通过统一的时 钟进行同步,即所有的互联的部件或设备都必须 使用同一个时钟(同步时钟),在规定的时钟节 拍内进行规定的总线操作,来完成部件或设备之 间的信息交换。 ② 异步总线:指没有统一的时钟而依靠各部件或设 备内部定时操作,所有部件或设备是以信号握手 的方式进行,即发送设备和接受设备互用请求 (request)和确认(acknowledgement)信号来 协调动作,总线操作时序不是固定的。因此,异 步总线能兼容多种不同的设备,而且不必担心时 钟变形或同步问题使得总线长度不受限制。例如, 火线协议(Firewire 或IEEE1394)和USB2.0协议 都是异步总线协议。

25

二、总线的定时

总线的一次信息传送过程,大致可分为五个阶段: ① 请求总线阶段; ② 总线仲裁阶段; ③ 寻址阶段; ④ 信息传送阶段; ⑤ 结束阶段。 为了同步主方、从方的操作,必须制订定时协议 定时协议。 定时协议 定时:是指事件出现在总线上的时序关系。 数据传送过程中采用两种定时方式: ① ② 同步定时 异步定时

14

总线信息的传送方式

3. 分时传送

分时传送有两种含义。 一种是:指采用总线复用,即在传输线上既传送 地址信息,又传送数据信息,这样可以减少总线 的线数,为此,必须划分时间片,使得同一总线 上在不同的时间片中完成传送地址和传送数据的 任务。 二种是:指共享总线的部件分时使用总线。因为, 总线是系统的公共资源,可以有很多部件挂在总 线上,但在一个时间片内,总线只为一对互相交 换信息的源设备和目的设备提供服务。所以,如 果有多个设备要求使用总线时,要由总线控制器 按时间片来分时提供服务。

总 线 概 述

通信总线

用于主机和I/O设备或者微 机系统与微机系统之间通信 的总线,又称为外部总线。

1)按总线分级 结构划分

系统总线

通常一个模块就是一块插件 板,各个插件板的插座之间采 用总线连接,以实现相互间的 信息交换和数据传输,这样的 总线叫做系统总线。

2)按总线功能或信号类型划分

地址总线 用于传输地址信息, 一般采用三态逻辑。

寻址阶段

取得总线使用权的主控模块,通过总线发出本 次打算访问的从属模块的地址及有关命令,以 启动参与本次传输的从属模块。

传输阶段

主控模块和从属模块之间进行数据传输,数据 由源模块发出经数据总线流入目的模块。

结束阶段

主控模块的有关信息均从系统总线上撤 除,让出总线。

2021年1月30日星期六

1.3 总线标准的基本内容

2021年1月30日星期六

2.总线的分类

CPU总线

又称为片内总线,是微机系统 中速度最快的总线,位于CPU内 部,作为运算器、控制器、寄 存器组等功能单元之间的信息 通路。

局部总线

直接连接到CPU总线的I/O总 线,因此使有高需求的外设和 处理器更密集地集成,为外设 提供了更宽更快的高速通路。

2021年1月30日星期六

此种方式是前两种方式的折中。 从总体上看,它是一个同步系 统,仍用系统时钟来定时,用 某一时钟脉冲的前沿或后沿判 断某一信号的状态,或控制某 一信号的产生或消失,使传输 操作与时钟同步。

2021年1月30日星期六

1.5 PC系列机中系统总线的发展简介

早期的PC系列机采用的系统总线叫PC总线、PC/AT总线,后来经 过标准化后称为ISA(Industrial Standard Architecture)总线。 为了赢得市场,IBM公司公布了ISA总线的全部规范和机器的硬件结构。 这确实见效,其机器迅速占领微机市场,但随之而来出现了一大批兼 容机厂家。为此IBM公司在推出第一台80386机时创立了一种和ISA总 线不兼容的MCA(Micro Channel Architecture)总线。IBM公司吸取 以前的教训,未公布其标准,企图垄断市场。

总线的基本概念

05 总线的优缺点

总线的优点

可靠性高

总线结构简单,各部件具有标 准的接口,因此可靠性较高。

可扩展性强

总线采用分支结构,易于扩展 ,可以适应系统规模的变动。

灵活性好

总线允许挂接多个设备,设备 间互不影响,增删设备方便。

成本较低

由于总线结构简单,所以成本 较低,适用于中小型系统。

总线的缺点

速度慢

由于总线上设备较多,每个设备都需要时间 来访问总线,导致整体速度较慢。

总线的传输方式

同步传输

同步传输是指总线上的所有节点都按 照同一个时钟信号进行操作,数据在 时钟信号的控制下进行传输。

异步传输

异步传输是指总线上的节点按照各自 的时钟信号进行操作,数据传输不受 时钟信号的控制,但需要额外的握手 信号来保证数据传输的正确性。

03 总线的应用场景

计算机总线

01

计算机总线是连接计算机各部件的一组公共信号线, 用于传输数据、地址和控制信号。

总线的分类

按照传输性质分类

可以分为数据总线、地址总线和控制总线。数据总线用于传输数据,地址总线 用于传输地址信息,控制总线用于传输控制信号。

按照连接设备分类

可以分为内部总线和外部总线。内部总线连接计算机内部设备或模块,如CPU、 内存、显卡等;外部总线连接计算机外部设备,如打印机、扫描仪、摄像头等。

低功耗总线技术

随着移动设备和物联网设备的普及, 低功耗总线技术越来越受到关注,如 I2C、SPI等,以延长设备续航时间和 降低能源消耗。

总线标准的统一

标准化组织

为了促进总线技术的发展和应用

,许多标准化组织致力于制定总

线标准,如PCI

SIG、USB

Implementers Forum等。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Indicatesthefirsttransferofaburstorasingletransfer. Theaddressandcontrolsignalsareunrelatedtothe previoustransfer.(NONSEQUENTIAL)

TheremainingtransfersinaburstareSEQUENTIALand theaddressisrelatedtotheprevioustransfer.Thecontrol informationisidenticaltotheprevioustransfer.

写传输:从模块采样HWDATA信号,完成传输 读传输:主模块采样HRDATA信号,完成传输

《微型计算机原理》 15

时序图2:从模块插入等待周期的传输

扩展

扩展

未准 备好

主模块 发出地址 从模块 采样地址

未准 备好

准备好

主模块采样读数据 从模块采样写数据

《微型计算机原理》 16

从模块插入等待周期的典型情况

主模块2

从模块2

从模块3

译码器

《微型计算机原理》 4

总线模块

总线主模块(Bus Master)

具有总线控制能力,在获得总线控制权之后能 启动总线传输(读数据或写数据) 示例:CPU、DMA控制器

总线从模块(Bus Slave)

能够对总线传输作出响应(接收写数据、返回 读数据、返回“错误”响应等),但本身不具 备总线控制能力 示例:存储器

主要内容

一、总线的基本结构 二、总线协议实例

教材相关章节: 《微型计算机基本原理与应用(第二版)》 第14章 总线及总线标准 第7章 微处理器的内部结构及外部功能特性 参考材料: “AMBA Specification” (Rev 2.0) Chapter 3 AMBAAHB

《微型计算机原理》 1

10010H

…… …..

对应地址

《微型计算机原理》 29

地址回卷的要点说明

地址回卷的边界(假设数据宽度为4字节)

WRAP4:在16的整数倍的地址处回卷(4×4) WRAP8:在32的整数倍的地址处回卷(4×8) WRAP16:在64的整数倍的地址处回卷(4×16)

传输地址变化示例

INCR4: 0x38 0x3C 0x40 0x44 WRAP4:0x38 0x3C 0x30 0x34 INCR4: 0x30 0x34 0x38 0x3C

仲裁策略示例

《微型计算机原理》

6

总线译码器(Bus Decoder)

功能:根据当前控制总线的主模块提供的地 址,选择作为本次总线传输目标的从模块

case ( addr[15:12] ) 4’b0000: sel1 = 1 ; 4’b0001: sel2 = 1 ; 4’b0010: sel3 = 1 ; ... endcase

sel3

总线逻辑电路示意图

授 权

仲裁器

申请

主模块 1

地址和控制

从模块 1 从模块 2 从模块 3 译码器

选中

《微型计算机原理》 8

写数据

主模块 2

读数据 和响应

80386DX所对应的总线模型

主模块

从模块

80386DX 仲裁器

HOLD HLDA

I/O接口

总 线

存储器 译码器

从模块

DMA 控制器

主模块

起始地址相同

访问区域相同

《微型计算机原理》

30

主模块控制信号:HSIZE

HSIZE[2:0]定义了传输数据的宽度

编码

000

宽度(bit)

8

说明

字节(Byte)

001 010 011

100 101 110 111

16 32 64

128 256 512 1024

半字(Halfword) 字(Word) 四字(4-wordline) 八字(8-wordline) -

未命中,读主存地址10010H,添 加表项1,返回03H

MOV MOV

Cache

地址 表项0 表项1 表项2 表项3 …… 1001H 04 H 03 H 02 H 01 H 数据块

问题: 实际上,地址[10018H]对 应的数据是“关键字”, 是影响性能的关键因素

10010H

…… …..

对应地址

《微型计算机原理》 28

主要内容

一、总线的基本结构 二、总线协议实例

《微型计算机原理》

11

《微型计算机原理》

12

AHB的基本结构

《微型计算机原理》

13

时序图1: 一次简单AHB传输

主模块发出 地址和控制 主模块发出 写数据 主模块采样 读数据

时钟

主 模 块 从 模 块

地址

控制

写数据 准备好 读数据

从模块采样 地址和控制 从模块采样 写数据

CPU作为主模块,读取内存数据时,内存控 制器作为总线从模块,往往需要插入数十到 数百个等待周期

列选 预充电

数据输出 数据 CPU 内存 BUS 控制器 地址 行选 BUS

Data In/Out Buffers Column Decoder Sense Amplifiers

Bit Lines ……

Block

4444 Cache Line 8888 Cache Line 1111 Cache Line ……

《微型计算机原理》 25

Burst传输的应用(2)

外设和主存之间的大量连续数据传输

若传输过程中出现外设未准备好的情况,则可 以使用传输状态“BUSY”

主存中不同区域之间的大量连续数据传输

发出 地址A 发出 地址B 发出 地址C

发出 数据A

传输A 完成 未准 备好

扩展

注意不同传输的地址和数据 在时间上的重叠(overlap)

传输B 完成

传输C 完成

《微型计算机原理》 19

要点说明

等待周期

地址A和C的传输中没有等待周期 地址B的传输中有一个等待周期,该传输的数据 阶段扩展了一个周期

CPU M

M S S 存储器

DMAC

M S

网络 控制器

DMAC

M: 主模块接口

S: 从模块接口

《微型计算机原理》 26

时序图5:地址回卷的四个数据的传输

地址回卷

*HWRITE信号:1表示写传输,0表示读传输

《微型计算机原理》 27

地址回卷的传输应用举例

“关键字优先”的高速缓存行填充

设:DS=1000H ES=2000H MOV ;数据地址 BX, [18H] ;10018H CX, [30H] ;10030H DX, ES:[10H] ;20010H

地址回卷的传输应用举例

“关键字优先”的高速缓存行填充

本例中可采用WRAP4类型的总线传输 地址[10080H]对应的数据将首先返回 若采用INCR4类型的总线传输,则地址[10080H] 对应的数据将作为第三个数据返回,延迟较大

Cache

地址 表项0 表项1 表项2 表项3 …… 1001H 04 H 03 H 02 H 01 H 数据块

IDLE

INCR4

地址递增的4个数据的传输

《微型计算机原理》 23

要点说明

T1:传输开始,主模块发出第一个地址,驱 动HTRANS=NONSEQ,HBURST=INCR4 T2:主模块由于自身原因,暂时无法发出第 二个地址,因此驱动HTRANS=BUSY T3:主模块恢复正常传输,发出第二个地址, 驱动HTRANS=SEQ T7:主模块发出的第四个地址已被从模块采 样,无需再发出新的地址和控制信号,因此 驱动HTRANS=IDLE

《微型计算机原理》 24

Burst传输的应用(1)

高速缓存的行填充(读)、行替换(写)

地址 地址

CPU Core

数据

Cache

数据

Block

Main Memory

有效位 1 0 1

地址 1000 3018 4530

数据 1111 5555 4444

……

……

……

2222 6666 3333 ……

3333 7777 2222 ……

等待周期的副作用

因为地址B的传输中的等待周期,所以地址C的 传输的地址阶段受其影响而扩展了一个周期

《微型计算机原理》

20

主模块控制信号:HTRANS

HTRANS[1:0]定义传输中各周期的类型

编码 00 01 10 11 类型 IDLE BUSY NONSEQ SEQ 说明

Indicatesthatnodatatransferisrequired.TheIDLE transfertypeisusedwhenabusmasterisgrantedthebus, butdoesnotwishtoperformadatatransfer. Indicatesthatthebusmasteriscontinuingwithaburstof transfers,butthenexttransfercannottakeplace immediately.Thetransfershouldbeignoredbytheslave.

《微型计算机原理》 5

总线仲裁器(Bus Arbiter)

功能:在总线上有多个主模块同时请求使用 总线时,决定由哪个主模块获得总线控制权 目的:让总线得到合理、高效地使用

主模块 1

主模块 2

req1

gnt1

req2 gnt2

仲 裁 器

bus_busy

if ( bus_busy is false) begin if ( req1 == 1 ) gnt1= 1 ; else if ( req2 == 1 ) gnt2= 1 ; end