MAXPLUS2基本元件库

Max+Plus II 使用说明 (一)

Max+Plus II 使用说明 (一)Max+Plus II 是一款基于计算机辅助设计 (CAD) 技术的数字逻辑电路仿真软件。

这款软件由美国英特尔公司 (Intel) 开发,可用于设计和验证数字逻辑电路,包括组合逻辑电路和时序逻辑电路。

本文将详细介绍 Max+Plus II 的使用说明,帮助用户更好地了解和应用该软件。

一、软件下载与安装Max+Plus II 可以从英特尔公司的官方网站上下载,安装过程简单,用户只需要按照安装向导逐步完成即可。

注意,该软件只能在 32 位版本的 Windows 操作系统上运行,所以用户需要确保自己的电脑系统符合要求。

二、主要功能介绍1. 逻辑设计:Max+Plus II 提供了完整的数字逻辑设计工具箱,包括位宽选择、时钟控制、计数器设计等工具,支持标准硬件描述语言VHDL 和 Verilog。

2. 仿真调试:Max+Plus II 可以进行逻辑仿真和时序仿真,模拟电路的输入输出信号,检查电路设计的正确性和可行性。

3. 器件库管理:Max+Plus II 内置了丰富的器件库,用户可以根据需要选择和添加器件,支持包括 FPGA、CPLD、RAM、ROM 等在内的多种器件类型。

4. 项目管理:Max+Plus II 支持多个项目的并行管理,用户可以轻松创建、打开、保存和关闭项目,以及在不同的项目之间进行切换操作。

三、使用步骤1. 创建项目:用户需要先创建一个新项目,然后选择适当的器件和设计语言,制定设计规范和参数,创建设计文件,并建立测试目标。

2. 设计与仿真:用户可以使用逻辑设计工具箱,将逻辑元件(例如逻辑门、寄存器、计数器等)组合起来构建数字逻辑电路,并在仿真界面中进行测试和验证。

3. 下载与调试:用户完成设计和仿真之后,可以将设计文件下载到目标设备中,然后进行实际调试和测试,以验证电路的正确性和可行性。

四、注意事项1. 在使用 Max+Plus II 进行数字逻辑电路设计时,需要遵循设计规范和标准,保证设计的正确性和可靠性。

qq※EDA技术概述参考答案

※EDA技术概述参考答案填空题1.2000年推出的Pentium 4微处理器芯片的集成度达4200 万只晶体管。

2.一般把EDA技术的发展分为cad、cae 和eda 三个阶段。

3.在EDA发展的cad 阶段,人们只能借助计算机对电路进行模拟、预测以及辅助进行集成电路版图编辑、印刷电路板(PCB)布局布线等工作。

4.在EDA发展的cae阶段,人们可以将计算机作为单点设计工具,并建立各种设计单元库,开始用计算机将许多单点工具集成在一起使用。

5.EDA设计流程包括设计准备、设计输入、设计处理和器件编程四个步骤。

6.EDA的设计验证包括功能仿真、时序仿真和三个过程。

7.EDA的设计输入主要包括图形输入方式、文本输入方式和波形输入方式。

8.文本输入是指采用硬件描述语言进行电路设计的方式。

9.功能仿真是在设计输入完成之后,选择具体器件进行编译之前进行的逻辑功能验证,因此又称为前仿真。

10.时序仿真是在选择了具体器件并完成都局、布线之后进行的时序关系仿真,因此又称为后仿真或延时仿真。

11.当前最流行的并成为IEEE标准的硬件描述语言包括 vhdl 和verilog 。

12.采用PLD进行的数字系统设计,是基于芯片的设计或称之为自底向上的设计。

13.硬件描述语言HDL给PLD和数字系统的设计带来了更新的设计方法和理念,产生了目前最常用的并称之为自顶向下的设计法。

14,EDA工具大致可以分为设计输入编辑器、仿真器、 hdl综合器、适配器以及下载器等5个模块。

15.将硬件描述语言转化为硬件电路的重要工具软件称为综合器。

单项选择题1.将设计的系统或电路按照EDA开发软件要求的某种形式表示出来,并送入计算机的过程称为( 1 )。

①设计输入②设计输出③仿真④综合2.一般把EDA技术的发展分为( 2 )个阶段。

①2 ②3 ③4 ④53.AHDL属于( 1 )描述语言。

①普通硬件②行为③高级④低级4.VHDL属于(1 )描述语言。

4位串行进位加法器Max+plus II仿真

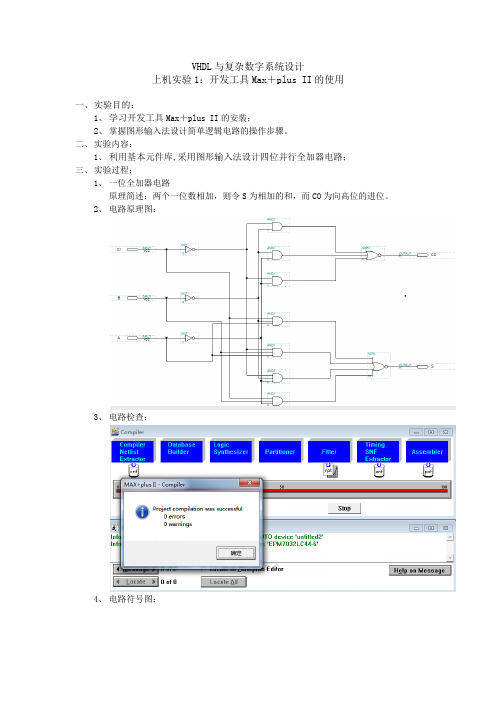

VHDL与复杂数字系统设计

上机实验1:开发工具Max+plus II的使用

一、实验目的:

1、学习开发工具Max+plus II的安装;

2、掌握图形输入法设计简单逻辑电路的操作步骤。

二、实验内容:

1、利用基本元件库,采用图形输入法设计四位并行全加器电路;

三、实验过程:

1、一位全加器电路

原理简述:两个一位数相加,则令S为相加的和,而CO为向高位的进位。

2、电路原理图:

3、电路检查:

4、电路符号图:

2、4位串行进位加法器

原理简述:四位串行进位加法器就是将四个一位加法器串联,低一位的进位就是上一位的CI输入。

最低位的进位为低低电平(没有进位)。

电流原理图

电路检查:

有以上的电路图所仿真得出的波形图为:

图形与理论的结果相同。

结论:四位串行进位加法器的电路图就是以上所得的电路图。

与实际的图形相比有延时。

但总的图形是非常吻合的。

MaxplusII简介及原理图设计法

编译您的项目

FLEX 器件的进位 级联链 器件的进位/级联链

进位链提供逻辑单元之间的非常快的向前进位功能。 利用级联链可以实现扇入很多的逻辑函数。 如选择FAST 综合方式,则进位/级联链选项自动有效。按如 下步骤可人工选择该选项是否有效:

1. 在 Global Project Logic Synthesis 对话框内选择 Define Synthesis Style 项,将出现 Define Synthesis Style 窗口。

2009 Arria® II GX FPGA 业界功耗最低的成本最优40-nm FPGA,它带有3.75-Gbps收发器,进一步提 高了可用性,使设计人员能够更迅速地完成工程。 2009 Stratix® IV GT FPGA 业界唯一集成了11.3-Gbps收发器的FPGA,适合40G/100G应用。 2008 Stratix ® IV FPGA 业界的首款40-nm FPGA,具有最高的密度、最好的性能、最低的功耗、最大 的收发器带宽(高达8.5-Gbps 的收发器),并为PCI Express Gen 1/2提供硬核知识产权(IP)模块。 2007 ArriaTM GX FPGAs 业界的首款低成本,基于收发器的中端,协议优化的FPGA。 2007 Cyclone® III FPGA 业界的首款低成本65nm FPGA,前所未有地同时实现了低功耗、低成本和高性能。 2006 Stratix III FPGA 65nm FPGA以更高的密度和性能支持高级集成,实现更复杂的产品。 2006 Quartus® II 软件 自然支持SDC设计约束 2006 C2H 编译器 嵌入式处理器的首款自动ANSI C至寄存器级(RTL)生成工具 2006 Stratix II GX FPGA 速度最快,密度最大的90nm FPGA架构,含有工作在622Mbps至6.375Gbps的20个低功耗收发器。 2005 HardCopy® II 结构化 ASIC 精细粒度体系结构;从90nm Stratix II FGPA原型无缝移植。 2005 Cyclone II FPGA 90nm FPGA,业界首款低成本FPGA,成本降低30%,密度提高3倍。 2004 Stratix II FPGA 90nm FPGA,含有名为ALM的8输入“分段式”查找表(LUT),以此替代了4输入LUT体系结构。 2003 Quartus II 软件 可编程逻辑软件包,提供Tcl脚本支持。 2003 Stratix GX FPGA 0.13µm FPGA,分块收发器体系结构。 2003 HardCopy 结构化 ASIC 业界唯一原型至量产0.13µm的完整解决方案

MAX+plusⅡ操作指南

4.1 Altera MAX+plusⅡ操作指南Alter公司的MAX+plusⅡ是一个高度集成化的可编程逻辑器件开发系统,可以开发Alter公司的MAX系列和FLEX系列的可编程器件。

该系统的主要特点如下:①支持多种设计输入方式。

如:原理图、VHDL语言、AHDL语言、波形图等。

同时还支持主流的第三方EDA工具,如:Synopsys、Cadence、ViewLogic、Synplicity、Mentor和Model Technology等等。

②提供完善的功能仿真,同时还提供精确的时间仿真。

③该系统把设计输入、功能仿真、时间仿真、设计编译以及器件编程集成于统一的开发环境下,从而更方便、更快捷。

④ MAX+plusⅡ开发系统还具有编译快捷,设计实现优化的功能。

MAX+plusⅡMAX+PLUSII PC版可以在以下几种操作系统下运行:Windows NT 4.0/Windows 98/Windows 2000/Windows XP。

表4.1中列出了用于不同器件所需的有效内存。

表4.1 MAX+PLUSII系统所需的存储器器件系列ACEX1K MAX7000MAX9000FLEX6000FLEX8000FLEX10K最小内存/MB256 48 64 64 64 256物理RAM/MB128 16 32 32 32 1282)安装MAX+PLUSII10.2 PC版下面介绍MAX+PLUSII PC版在Windows 98操作系统下的安装过程。

若在其他操作系统下安装,可参照此方法操作。

(1)将MAX+PLUSII10.2安装光盘放入光驱,安装窗口将自动出现图4.1所示的界面。

图4你可以选择MAX+PLUSII 10.2安装类型如下:Custom、BASELINE、Programmer Only和ACCESS Key Guidelines。

开始安装之前,你还可以阅读Help文件、Read Me文件、License Agreement 文件和ACCESS Key Guidelines。

第三章MAX+PLUS Ⅱ开发系统

第三章 MAX+PLUS Ⅱ开发系统

3.2 可编程逻辑器件的开发环境

如前所述,EDA技术在当代迅猛发展,同时各种EDA 软件也如雨后春笋般呈现在用户面前。它们一般分为两种, 一种是PLD芯片制造商为推广自己的芯片而开发的专业 EDA软件,本书所使用的Altera公司推出的 MAX+plusⅡ就属于此类。另一种是EDA软件商提供的 第三方软件,如知名的Synplify、Synopsys、 Viewlogic、Cadence等,这种软件可以支持大部分芯片 公司的PLD器件。

设计输入有多种表达方式,主要包括原理图输入、硬件描 述语言输入、网表输入和波形输入四种。其中最常用的是 原理图输入和硬件描述语言输入。

1.原理图输入

原理图是图形化的表达方式,它是利用软件中所提供的元 件符号和连线来描述设计。其特点是比较直观,便于进行 接口设计和管脚锁定,容易实现仿真,便于信号的观察和 电路的调整,系统运行速率较高,但当描述复杂电路时则 比较繁琐。

第三章 MAX+PLUS Ⅱ开发系统

7.仿真器(Simulator)

它的主要作用是校验设计中的逻辑操作以及时延的正 确性。仿真器允许用户脱离硬件仅对设计逻辑进行仿真, 这可大大减少仿真时间。

第三章 MAX+PLUS Ⅱ开发系统

8.时间分析器(Timing Analyzer)

它可用来分析预测器件的时延特性。时延分析结束后, 在窗口中会列出相关源节点与目标节点的延时路径及延时 的大小,用户可以根据需要选择原设计中的时延路径。借 助时间分析的功能可达到最佳布局规划,加快所设计器件 的处理速度。

第三章 MAX+PLUS Ⅱ开发系统

右图为引脚平面 编辑器的逻辑阵列块 视图 。

《EDA技术基础》复习资料

EDA复习资料【EDA技术根底】题库及参考答案〔试用版〕目录一、填空题 ....................................................................................................... 错误!未定义书签。

二、单项选择题............................................................................................. 错误!未定义书签。

三、简答题 ....................................................................................................... 错误!未定义书签。

四、应用题 ....................................................................................................... 错误!未定义书签。

五、上机实验题............................................................................................. 错误!未定义书签。

一、填空题1.现代电子技术经历了CAD 、CAE 和EDA 三个主要的开展阶段。

2.EDA技术包括大规模可编程器件、硬件描述语言HDL 、EDA工具软件和实验开发系统四大要素。

3.EDA的设计输入主要包括文本输入方式、图形输入方式和波形输入方式三种形式。

4.目前已经成为IEEE标准、应用最为广泛的硬件描述语言有VHDL 和Verilog HDL 。

仿真是一种对所设计电路进行间接检测的方法,包括_ 功能仿真和_ 时序仿真。

text1(MAX库元件介绍之一:基本逻辑元件库primitives)

基本逻辑元件库Primitives1. 库简介数字电路的基本逻辑元件都放在maxplus2\max2lib\prim\子目录中。

详细说明参考Maxplus2软件Help/Primitives。

2. 常用元件2.1 缓冲器CARRY 进位基元CASCADE 与门或门的级联基元GLOBAL (SCLK) 全局同步信号基元TRI 带输出使能(高电平有效)的三态门OPNDRN 类似TRI,无输出使能;输入为高电平时输出为高阻。

WIRE (GDFs only) 重命名基元(针对端口或总线)2.2 触发器及锁存器DFF D触发器DFFE 带时钟使能的D触发器JKFF JK触发器JKFFE 带时钟使能的JK触发器LATCH 锁存器SRFF SR触发器SRFFE 带时钟使能的SR触发器TFF T触发器TFFE 带时钟使能的T触发器2.3 输入输出单元INPUT 输入基元OUTPUT 输出基元BIDIR 双向基元2.4 逻辑基元AND 与门;后接数字(2, 3, 4, 6, 8, or 12)表示输入个数,例and3 BAND (GDFs only) 输入端带反相器的与门;后接数字同上BNAND (GDFs only) 输入端带反相器的与非门;后接数字同上BNOR (GDFs only) 输入端带反相器的或非门;后接数字同上BOR (GDFs only) 输入端带反相器的或门;后接数字同上GND (GDFs only) 地端NAND 与非门;后接数字同上NOR 或非门;后接数字同上NOT 非门OR 或门;后接数字同上VCC (GDFs only) VCC端XNOR 异或非门XOR 异或门2.5 其它基元CONSTANT 常量PARAM 参数Title Block 标题栏。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

MAXPLUS2基本元件库

打开图形编辑器(graphic editor),双击窗口,就可出现元件选项下拉菜单;

在c:\windows\temporary internet files 中,保存有用户自己编制的元件(实体);

在c:\maxplus2\max2lib\prim中,有各类基本门电路及输入/输出端口;

c:\maxplus2\max2lib\mf中,有74系列各类数字集成电路

c:\maxplus2\max2lib\mega_lpm中为可调参数库,包括参数化模块,功能复杂的高级功能模块,如可调模值的计数器,FIFO,RAM等

c:\maxplus2\max2lib\edif中元件的功能和mf库类似

现将常用的prim和mf库中的主要元件罗列如下:

c:\maxplus2\max2lib\prim

and12 and2 and3 and4 and6 and8 一般与门

band12 band2 band3 band4 band6 band8 输入反向与门= 或非门

bdir bdirc 双向端口、可控双向端口

bnand12 bnand2 bnand3 bnand4 bnand6 bnand8 输入反向与非门= 或门

bnor12 bnor2 bnor3 bnor4 bnor6 bnor8 输入反向或非门= 与门

bor12 bor2 bor3 bor4 bor6 bor8 输入反向或门= 与非门

carry cascade globol exp icell mcell opndrn sclk soft wire

constant 常量gnd 接地latch D锁存器

dff dffe 带低电平置位/清零的D触发器,后者带使能端

input inputc 输入端口

jkff jkffe 带低电平置位/清零的JK触发器,后者带使能端

nand12 nand2 nand3 nand4 nand6 nand8 与非门

nor12 nor2 nor3 nor4 nor6 nor8 或非门

not 反相器

or12 or2 or3 or4 or6 or8 或门

output outputc 输出端口param 参量

srff srffe 带低电平置位/清零的RS触发器,后者带使能端

tff tffe 带低电平置位/清零的t触发器,后者带使能端

title 标题框tri 三态门vcc 正电源

xnor xor 同或、异或

c:\maxplus2\max2lib\mf

161mux 16选1 * 81mux

16cudslr 16cudslr 16位计数/移位*

16dmux 16ndux 4-16 译码器*

21mux 2选1 *

2x8mux 8位2选1 * 4count 4位计数器*

74系列电路的分类:

“74”指的是商用器件,“54”是军用的,它们的适用温度范围不同,军用的范围大。

商用:0℃~70℃;军用:-55℃~125℃。

LS等是子系列的名称。

L:低功耗H:高速S:肖特基LS:低功耗消特基ALS:先进低功耗肖特基AS:先进肖特基LS:低功耗消特基

简单门电路

7400 4nand2 7402 4nor2 7404 6not 7408 4and 7410 3nand3

7411 3and3 7420 2nand4 7421 2and4 7423/25 2nor4 7427 3nor3

7428 4nor2 7430 nand8 7432 4or2 7437 4nand2 7440 2nand4 7450/51/53/54/55/64 2与或非7452 与或7486 异或2

74133/134 nand12 74135 4xor/nxor 74260 2nor5 74386 4xor

码制转换

7442/45/445 BCD-BEC 7443 余3-BEC 7444 GREY-BEC

7446/47/48/49/246/247/248 BCD-7段74137/138 3-8译码器

74139/155/156 双2-4译码器74143 4位计数/7段74145 BCD-DEC

74147/148 编码器74154 4-16译码器74184 BCD-二-十进制

74185 二-十进制-BCD

数据选择

74151/153/157/158/251/253/257/258/298/352/353/354/356/398/399/ mutilplexer

算术运算

7480/82/83 全加器74183 全加器74283 4位加法器74385 加/减器74284/285 4x4mult 7485 ALU

74518/684/686/688/ 比较器数值比较器74181/381/382/ 7487 true/comp 74180/280 奇偶发生器

总线缓冲

74240/241/244/465/466/467/468/540/541/ 8位总线缓冲

74365/366/367/368 16位总线缓冲

74265 COMP OUT ELE (互补输出)

锁存触发

7470/71/72/73/76/78/107/109/112/113/114//276/376 JK触发器

7474/171/273/374/377/378/379/821/822/823/824/825/826/ D触发器

7475/77/116/373 /375/841/842/843/844/845/846/990/ D锁存器

74279 RS锁存器

计数分频

7456/57 分频器74292/294 分频器7468 DEC计数器

7469 BIN计数器7490/92/93/176/177/196/197/592/ 计数器

74160/161/162/163/168/169/190/191/192193//290/293/393/490/568/569/668/669/690/691/693/69 6/697/698/699/ 计数器74390 双计数器

移位寄存

7491/94/95/96/164/165/166/178/179/194/195/198/199/295/299/589/590/594/595/597/673/ 移位寄存器7498/99/173/174/175/604/ 寄存器7497 rate mult。