DDR3内存插槽各针脚定义

SDDDR1DDR2DDR3内存外观区别

《内存区别》SD、DDR1、DDR2、DDR3内存外观区别(附图)SD:两个缺口、单面84针脚、双面168针脚DDR1:一个缺口、单面92针脚、双面184针脚、左52右40、内存颗粒长方形DDR2:一个缺口、单面120针脚、双面240针脚、左64右56、内存颗粒正方形、电压1.8VDDR3:一个缺口、单面120针脚、双面240针脚、左72右48、内存颗粒正方形、电压1.5VDDR1 DDR2 DDR3内存的区别对比DDR SDRAM 是 Double Data Rate SDRAM 的缩写,是双倍速率同步动态随机存储器的意思。

DDR内存是在SDRAM内存基础上发展而来的,仍然沿用SDRAM生产体系,因此对于内存厂商而言,只需对制造普通SDRAM的设备稍加改进,即可实现DDR内存的生产,可有效的降低成本。

目前DDR已经发展到了第三代,下面来看一下几代内存的区别:外观不同之处/showpic. html - blogid=01000bvy&url=/43fdfd51303a8参数不同之处电压 VDD/VDDQ 2.5V/2.5V 1.8V/1.8V(±0.1) 1.5V/1.5V(±0.075)I/O接口SSTL_25 SSTL_18 SSTL_15数据传输率(Mbps) 200~400 400~800 800~2000256M~4G 512M~8G容量标准64M~1GMemory Latency(ns) 15~20 10~20 10~15CL值 1.5/2/2.5/3 3/4/5/6 5/6/7/8预取设计(Bit) 2 4 8逻辑Bank数量2/4 4/8 8/16突发长度2/4/8 4/8 8封装TSOP FBGA FBGA引脚标准184Pin 240Pin 240Pin。

SD,DDR,DDR2引脚定义

SD内存插槽及测试点一、实物图上图中,黑色插槽就是SD内存插槽二、测试点SD内存插槽测试点:1个供电、4个时钟、6个信号测试点VCC:供电测试点,正常电压3.3V,由场管或橙色线提供CLK0、CLK1、CLK2、CLK3:时钟测试点,频率66/100/133MHZ,电压1.1V-1.6V,由北桥或时钟芯片提供6个信号测试点:CAS#:列选信号RAS#:行选信号/WE#:允许信号(高电平允许读,低电平允许写)/CS#:片选信号SCL:串行时钟,SDA:串行数据,由南桥提供3.3V电压DDR内存插槽及测试点一、实物图上图就是DDR内存插槽实物图二、测试点DDR内存插槽测试点:2个供电、6个时钟、6个信号测试点VCC=2.5V,1.25V:供电测试点CLK0、CLK1、CLK2、CLK3、CLK4、CLK5:时钟测试点,频率266/333/400MHZ,电压1.1V-1. 6V,如果主板有两块时钟芯片,内存时钟由靠近内存的时钟芯片提供;如果只有一个时钟芯片,内存的时钟由北桥提供6个信号测试点:CAS:列选信号RAS:行选信号WE:允许信号(高电平允许读,低电平允许写)CS:片选信号SCL:串行时钟,SDA:串行数据,由南桥提供3.3V电压D58、D56、D18等:是数据线,对地打阻值正常值300-800DDR2内存插槽测试点2009-10-2 10:37:43文/xiaowang 出处:电脑维修家园DDR2内存插槽实物图如下:1、时钟信号点,共有8个时钟信号点,分别位于52、137、138、171、185、186、220、221针脚,正常进,时钟信号点工作电压为1.1V。

2、电压信号点,DDR2内存插槽有2种电压,其中238针脚为3.3V供电脚,51、53、56、59、62、64、69、72、75、78、170、172、175、1 78、181、187、189、191、194针脚为1.8V供电脚。

SD、DDR1、DDR2、DDR3内存外观区别

《内存区别》SD、DDR1、DDR2、DDR3内存外观区别(附图)

SD:

两个缺口、单面84针脚、双面168针脚

DDR1:

一个缺口、单面92针脚、双面184针脚、左52右40、内存颗粒长方形

DDR2:

一个缺口、单面120针脚、双面240针脚、左64右56、内存颗粒正方形、电压1.8V

DDR3:一个缺口、单面120针脚、双面240针脚、左72右48、内存颗粒正方形、电压1.5V

DDR1 DDR2 DDR3内存的区别对比

DDR SDRAM 是 Double Data Rate SDRAM 的缩写,是双倍速率同步动态随机存储器的意思。

DDR内存是在SDRAM内存基础上发展而来的,仍然沿用SDRAM生产体系,因此对于内存厂商而言,只需对制造普通SDRAM的设备稍加改进,即可实现DDR内存的生产,可有效的降低成本。

目前DDR已经发展到了第三代,下面来看一下几代内存的区别:外观不同之处

参数不同之处。

DDR3详解

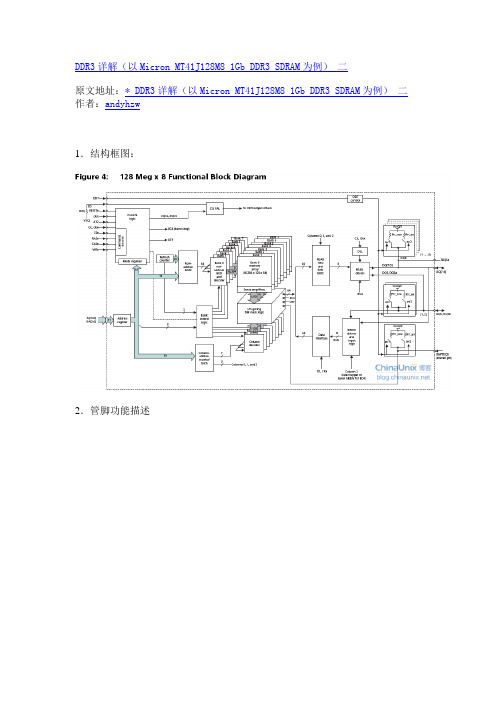

DDR3详解(以Micron MT41J128M8 1Gb DDR3 SDRAM为例)二原文地址:* DDR3详解(以Micron MT41J128M8 1Gb DDR3 SDRAM为例)二作者:andyhzw1.结构框图:2.管脚功能描述3.状态图:Power on: 上电Reset Procedure: 复位过程Initialization: 初始化ZQCL: 上电初始化后,用完成校准ZQ电阻。

ZQCL会触发DRAM内部的校准引擎,一旦校准完成,校准后的值会传递到DRAM的IO管脚上,并反映为输出驱动和ODT阻值。

ZQCS: 周期性的校准,能够跟随电压和温度的变化而变化。

校准需要更短的时间窗口,一次校准,可以有效的纠正最小0.5%的RON和RTT电阻。

Al:Additive latency.是用来在总线上保持命令或者数据的有效时间。

在ddr3允许直接操作读和写的操作过程中,AL是总线上的数据出现到进入器件内部的时间。

下图为DDR3标准所支持的时间操作。

Write Leveling:为了得到更好的信号完整性,DDR3存储模块采取了FLY_BY 的拓扑结构,来处理命令、地址、控制信号和时钟。

FLY_BY的拓扑结构可以有效的减少stub的数量和他们的长度,但是却会导致时钟和strobe信号在每个芯片上的flight time skew,这使得控制器(FPGA或者CPU)很难以保持Tdqss ,tdss和tdsh这些时序。

这样,ddr3支持write leveling这样一个特性,来允许控制器来补偿倾斜(flight time skew)。

存储器控制器能够用该特性和从DDR3反馈的数据调整DQS和CK之间的关系。

在这种调整中,存储器控制器可以对DQS信号可调整的延时,来与时钟信号的上升边沿对齐。

控制器不停对DQS进行延时,直到发现从0到1之间的跳变出现,然后DQS的延时通过这样的方式被建立起来了,由此可以保证tDQSS。

DDR3内存引脚功能定义

DDR3内存引脚功能定义

1.VDDQ:电源电压引脚,提供内存模块的电源。

2.VSS:地引脚,为内存模块提供地连接。

3.DQ[0:63]:数据引脚,用于传输数据。

4.DM[0:7]:差分引脚,用于传输数据。

5.DQS[0:7]:数据时钟引脚,用于接收和发送数据。

6.DQS#:数据时钟反相引脚。

7.CLK:频率引脚,用于DDR3内存控制器的时钟输入。

8.RAS#:行地址选通引脚,用于指示访问的行地址。

9.CAS#:列地址选通引脚,用于指示访问的列地址。

10.WE#:写使能引脚,用于指示写操作。

11.CS#:片选引脚,用于选择内存芯片。

12.CKE:时钟使能引脚,用于控制内存芯片的时钟。

13.ODT:输出驱动器强制引脚,用于控制输出阻抗。

14.RESET#:复位引脚,用于将内存芯片复位到初始状态。

15.VREFCA:输入和输出引脚,用于提供中心对齐参考电压。

16.VREFDQ:数据引脚的输入和输出引脚,用于提供数据对齐参考电压。

17.ZQ:零电阻引脚,用于控制内存模块的电阻值。

18.SA[0:1]:副功能地址引脚,用于选择内存模块的副功能。

以上是DDR3内存引脚功能定义的主要内容。

每个引脚的具体功能可能会有一些变化,取决于内存模块的制造商和具体型号。

在使用DDR3内存时,正确连接和使用各个引脚是非常重要的,以确保内存模块的正常运行和性能。

PC机内存条引脚定义.docx

PC机内存条引脚定义SIMM 30线内存条SIMM 是Single Inline Memory Module (单列直插)的缩写,最高容量为4MBx9,在无校验内存条中,QP和DP引脚是空的,外观为:3020DQ5 Data 521 /WE Write Enable22 GND Ground23 DQ6 Data 624 A11 Address 1125 DQ7 Data 726 QP Data Parity Out27 /RAS Row Address Strobe28 /CASP Something Parity ????29 DP Data Parity In30 VCC +5 VDCSIMM 是Single Inline Memory Module (单列直插)的缩写,72线内存条的外观为:引脚定义Pin无校验有校验Description1 VSS VSS Ground2 DQ0 DQ0 Data 03 DQ16 DQ16 Data 164 DQ1 DQ1 Data 15 DQ17 DQ17 Data 176 DQ2 DQ2 Data 27 DQ18 DQ18 Data 18SIMM 72 线内存条SIMM ECC 72线内存条SIMM 是Single Inline Memory Module (单列直插)的缩写,ECC 是ErrorCorrecting Code (纠错码)的缩写,外观为:SO DIMM 72线内存条DIMM 是Dual Inline Memory Module (双列直插)的缩写,SO 是Small Outline 的缩写SO DIMM 144线内存条DIMM 是Dual Inline Memory Module (双列直插)的缩写,SO 是Small Outline 的缩写52 DQ46DQ46 Data 46 53 DQ15DQ15 Data 15 54 DQ47DQ47 Data 47 55 VSSVSS Ground 56 VSSVSS Ground 57 n/cCB0 58 n/cCB4 59 n/cCB1 60 n/cCB5 61 DUDU Don't use 65 DU DUDon't use 66 DU DUDon't use 67 /WE /WERead/Write 68 n/cn/c Not connected 69 /RASO /RAS0 Row Address Strobe 070 n/c n/c Not connected71 /RAS1 /RAS1 Row Address Strobe 172 n/cn/c Not connected 73 /OE/OE 74 n/cn/c Not connected 75 VSSVSS Ground 76 VSSVSS Ground 77 n/cCB2 78 n/cCB6 64 VCC VCC+5 VDC CB379 /c 62 DU Don't use +5 VDC 80 n/c CB781 CC VCC+5 VDC 82 CCVCC +5 VDC 83 DQ16DQ16 Data 16 84 DQ48DQ48 Data 48 85 DQ17DQ17 Data 17 86 DQ49 DQ49 Data 49DUCC VCC63123 DQ25 DQ25 Data 25124 DQ57 DQ57 Data 57125 DQ26 DQ26 Data 26126 DQ58 DQ58 Data 58127 DQ27 DQ27 Data 27128 DQ59 DQ59 Data 59129 VCC VCC +5 VDC130 VCC VCC +5 VDC131 DQ28 DQ28 Data 28132 DQ60 DQ60 Data 60133 DQ29 DQ29 Data 29134 DQ61 DQ61 Data 61135 DQ30 DQ30 Data 30136 DQ62 DQ62 Data 62137 DQ31 DQ31 Data 31138 DQ63 DQ63 Data 63139 VSS VSS Ground140 VSS VSS Ground141 SDA SDA142 SCL SCL143 VCC VCC +5 VDC144 VCC VCC +5 VDCDIMM DRAM 168 线内存条DIMM 是Dual Inline Memory Module (双列直插)的缩写引脚定义正面,左方:1 VSS VSS VSS VSS Ground43 VSS VSS VSS VSS Ground44 /OE2 /OE2 /OE2 /OE245 /RAS2 /RAS2 /RAS2 /RAS2 Row Address Strobe 246 /CAS2 /CAS2 /CAS2 /CAS2 Column Address Strobe 247 /CAS3 /CAS3 /CAS3 /CAS3 Column Address Strobe 348 /WE2 /WE2 /WE2 /WE2 Read/Write Input49 VCC VCC VCC VCC +5 VDC or +3.3 VDC50 n/c n/c n/c CB10 Parity/Check Bit Input/Output 1051 n/c n/c n/c CB11 Parity/Check Bit Input/Output 1152 n/c CB2 CB2 CB2 Parity/Check Bit Input/Output 253 n/c CB3 CB3 CB3 Parity/Check Bit Input/Output 354 VSS VSS VSS VSS Ground55 DQ16 DQ16 DQ16 DQ16 Data 1657 DQ18 DQ18 DQ18 DQ18 Data 1858 DQ19 DQ19 DQ19 DQ19 Data 19CC VCC VCC VCC +5 VDC or +3.3 VDCDQ20 DQ20 DQ20 DQ20 Data 20n/c n/c n/c n/c Not connected38 A10 A10 A10 A10 Address 1039 A12 A12 A12 A12 Address 1240 VCC VCC VCC VCC +5 VDC or +3.3 VDC41 VCC VCC VCC VCC +5 VDC or +3.3 VDC42 DU DU DU DU Don't Use6 DQ17 DQ17 DQ17 DQ17 Data 17n/c3 n/c n/c n/c Not connectedDIMM SDRAM 168 线内存条DIMM 是Dual Inline Memory Module (双列直插)的缩写124 VDD VDD VDD +5 VDC or +3.3 VDC 125 CK1CK1 CK1 Clock signal 1 126 A12A12 A12 Address 12 133 VDD VDD VDD+5 VDC or +3.3 VDC 134 n/c n/c CB14Parity/Check Bit Input/Output 14 135 n/c n/c CB15Parity/Check Bit Input/Output 15 136 n/c CB6 CB6Parity/Check Bit Input/Output 6 137 n/c CB7 CB7Parity/Check Bit Input/Output 7 138 VSS VSS VSSGround 139 DQ48 DQ48 DQ48Data 48 140 DQ49 DQ49 DQ49Data 49 141 DQ50 DQ50 DQ50Data 50 132 A13 A13A13 Address 13 DQ51 DQ51DQ51 142 Data51 128 CKEO CKEO CKEO Clock Enable Signal 0 129 /S3 /S3 /S3 Chip Select 3 130 DQMB6 DQMB6 DQMB6 Byte Mask signal 6 131 DQMB7 DQMB7 DQMB7 Byte Mask signal 7 143 VDDVDD VDD +5 VDC or +3.3 VDC 144 DQ52 DQ52 DQ52 Data 52 145 n/cn/c n/c Not connected 146 Vref,NC Vref,NC Vref,NC 147 n/cn/c n/c Not connected 148 VSSVSS VSS Ground 149 DQ53 DQ53 DQ53 Data 53 150 DQ54 DQ54 DQ54 Data 54 151 DQ55 DQ55 DQ55 Data 55 152 VSSVSS SS Ground 153 DQ56 DQ56 DQ56 Data 56 154 DQ57DQ57 DQ57 Data 57 155 DQ58 DQ58 DQ58 Data 58VSS VSS VSS Ground 127。

DDR3,DIMM在FPGA上引脚分配规则,完全手打中文

FPGA BANK选择页面中的图是所选部件物理表示的架构视图。

默认情况下, MIG 将使用推荐的选择,地址/控制BANK和数据BANK是根据V6对不同频率的规则限定的。

选择您想要使用的BANK for内存接口,你用不着选择的实际的引脚。

默认情况下MIG将使用所选bank中的任意引脚for内存接口。

设计规则:∙设计最大频率:o-1 FPGA 速度级器件: 400 MHzo-2 和-3 FPGA 速度级器件: 533 MHzo只有-2 FPGA 速度等级的 CXT 设备只要303 MHz支持o低功耗V6设备只需303303 MHz∙频率超过333 MHz,只有数据宽度低于72位被容许。

频率低于333 MHz 数据宽度低于144 位被允许∙内存类型、内存部件和数据宽度被限制基于所选的 FPGA 器件、 FPGA 器件速度等级和设计频率BANK的选择规则:∙地址/控制组只能选择在内部列BANK∙第一个选定的地址/控制组将有 CK [0] 和 CK #[0] 引脚∙包含CK [0] 和 CK #[0]的BANK,会有该MMCM应用与该H-Row∙对于设计频率400 MHz或更高,只有内部列BANK被允许用于数据组的选择。

对于设计频率为400 MHz以下,内部和外部列BANK被允许数据组的选择o内部或外部列BANK被唯一的允许for选择∙位于,包含CK [0]和CK #[0] 的BANK的上面一行、下面一行和同一行,的内外侧BANK,是可用的for数据组引脚选择∙此限制被一个称为vicinity box的边界箱描述∙系统时钟组只能被选择在包含GC引脚的BANK或者位于,和分配的MMCM 同一H-ROW的内部BANK。

∙控制和状态引脚即sys_rst,error等,在系统时钟BANK中分配.∙由于采用不同的电压标准,系统时钟组与其余的设计组针脚(地址/控制组和数据组)不能共存于同一BANK。

∙一个主BANK必须被选择for每个列,假如系统时钟BANK不能作为主BANK引脚分配规则:∙地址/控制组:o包含 A、BA、 CK、 CK #、 CKE、 CS #、 RAS #、 CAS #、 WE#、 ODT, RESET #o只能选择内部列BANKo内存时钟信号(CK [0] 和 CK#[0]) 分配给差分对引脚(P Npair)o VRN/VRP 引脚若被用于引脚分配,DCI级联应该被采用,用以支持地址/时钟的 DCI 标准PS: XILINX公司的Virtex系列FPGA芯片上,每个BANK都有一对VRP/VRN管脚。

不同内存的外观区别和区分(附图)

《内存区别》SD、DDR1、DDR2、DDR3内存外观区别(附图)SD:两个缺口、单面84针脚、双面168针脚DDR1:一个缺口、单面92针脚、双面184针脚、左52右40、内存颗粒长方形DDR2:一个缺口、单面120针脚、双面240针脚、左64右56、内存颗粒正方形、电压1.8VDDR3:一个缺口、单面120针脚、双面240针脚、左72右48、内存颗粒正方形、电压1.5V内存分SD,DDR,DDR2,DDR3型号,请对照以下列表,知道自己电脑已经安装了什么内存,你应该购买什么内存。

PC2100是DDR 266内存PC2700是DDR 333内存PC3200是DDR 400内存PC4200是DDRII533内存PC4300是DDRII533内存PC5300是DDRII667内存PC6400是DDRII800内存PC8500是DDRIII1066内存PC10700是DDRIII11333内存DDR、DDR2、DDR3互相不通用,插槽插口也不一样,更不能霸王硬上弓强行插进去,以免损坏内存和主板,切记!1、DDR代表是1代内存、DDR2代表是2代内存、DDR3代表是3代内存。

2、比如金士顿 512M DDR 400 台式机内存的“400”是频率的意思!常用内存频率有266、333、400、533、667、800、1066、1333……等频率。

频率越高,速度越快!3、内存须选择同型号的。

注意:不同型号内存,不要“硬插”!开机容易烧坏不能提供保修服务!4、常用内存有DDR、DDR2、DDR3之分,3种内存不能混用,拍前请确定自己电脑使用的是什么型号内存、什么频率。

5、如果您不确定自己电脑使用什么内存!可以用下面这个“CPU-Z”软件检测一下,谢谢!运行软件后看“SPD”选项的“最大带宽”一栏,会看到“PCxx00”,如下:DDR 是“1代内存”频率分266 333 400 规格PC2100是DDR 266内存PC2700是DDR 333内存PC3200是DDR 400内存DDR2 是“2代内存”频率分533 667 800 规格PC4200是DDRII533内存PC4300是DDRII533内存PC5300是DDRII667内存PC6400是DDRII800内存DDR3是“3代内存”频率分1066 1333 1600 1800 2000 规格PC8500是DDRIII1066内存PC10600是DDRIII1333内存。

DDR内存条引脚定义图 管脚定义图

DQ10

51

VDDQ

81

DQ33

111

DQ57

141

DQ15

171

CKE1

201

VSS

231

VSS

22

DQ11

52

CKE0

82

VSS

112

VSS

142

VSS

172

VDD

202

DM4/DQS13

232

DM7/DQS16Fra bibliotek23VSS

53

VDD

83

DQS4#

113

DQS7#

143

DQ20

173

NC

203

DM2/DQS11

176

A12

206

DQ39

236

DQ63

27

DQS2#

57

A11

87

DQ35

117

DQ59

147

NC/DQS11#

177

A9

207

VSS

237

VSS

28

DQS2

58

A7

88

VSS

118

VSS

148

VSS

178

VDD

208

DQ44

238

VDDSPD

29

VSS

59

VDD

89

DQ40

119

69

VDD

99

DQ49

129

DQ7

159

DQ31

189

VDD

219

VSS

10

DQ3

40

DQ27

70

DDR内存条引脚定义图 管脚定义图

DQ10

51

VDDQ

81

DQ33

111

DQ57

141

DQ15

171

CKE1

201

VSS

231

VSS

22

DQ11

52

CKE0

82

VSS

112

VSS

142

VSS

172

VDD

202

DM4/DQS13

232

DM7/DQS16

23

VSS

53

VDD

83

DQS4#

113

DQS7#

143

DQ20

173

NC

203

DQ55

18

RESET#

48

CB2

78

VDDQ

108

DQ51

138

RFU

168

CB7

198

VSS

228

VSS

19

NC

49

CB3

79

VSS

109

VSS

139

VSS

169

VSS

199

DQ36

229

DQ60

20

VSS

50

VSS

80

DQ32

110

DQ56

140

DQ14

170

VDDQ

200

DQ37

230

DQ61

NC/DQS13#

233

NC/DQS16#

24

DQ16

54

NC/BA2

84

DQS4

114

DQS7

144

DQ21

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

DDR3内存插槽各针脚定义我是大笨熊

针脚信号定义说明针脚信号定义说明针脚信号定义说明针脚信号定义说明1 VREFDQ 2 VSS 地址线121 VSS 地址线122 DQ4 数据线3 DQ0 数据线 4 DQ1 数据线123 DQ5 数据线124 VSS 地址线5 VSS 地址线 6 DQS#0 效验位置125 DM0 126 NC 空7 DQS0 效验位置8 VSS 地址线127 VSS 地址线128 DQ6 数据线9 DQ2 数据线10 DQ3 数据线129 DQ7 数据线130 VSS 地址线11 VSS 地址线12 DQ8 数据线131 DQ12 数据线132 DQ13 数据线13 DQ9 数据线14 VSS 地址线133 VSS 地址线134 DM1

15 DQS#1 效验位置16 DQS1 效验位置135 NC 空136 VSS 地址线17 VSS 地址线18 DQ10 137 DQ14 138 DQ15

19 DQ11 数据线20 VSS 地址线139 VSS 数据线140 DQ20 数据线21 DQ16 数据线22 DQ17 数据线141 DQ21 数据线142 VSS 地址线23 VSS 地址线24 DQS2# 数据线143 DM2 数据线144 NC 数据线25 DQS2 数据线26 VSS 地址线145 VSS 地址线146 DQ22

27 DQS#2 效验位置28 DQ19 数据线147 DQ23 空148 VSS 地址线29 VSS 地址线30 DQ24 数据线149 DQ28 数据线150 DQ29 数据线31 DQ25 数据线32 VSS 地址线151 VSS 地址线152 DM3 数据线33 DQS3# 数据线34 DQS3 数据线153 NC 数据线154 VSS 地址线35 VSS 地址线36 DQ26 数据线155 DQ30 156 DQ31 空37 DQ27 数据线38 VSS 地址线157 VSS 地址线158 DQ30 数据线39 NC 数据线40 NC 数据线159 NC 数据线160 VSS 地址线41 VSS 地址线42 NC 空161 NC 空162 NC 空43 NC 空44 VSS 地址线163 VSS 地址线164 NC

45 NC 数据线46 NC 数据线165 NC 空166 VSS 地址线47 VSS 地址线48 VTT 空167 NC 空168 RESET# 复位49 VTT 空50 CKE0 时钟169 CKE1 时钟170 VDD 1.5v 51 VDD 1.5V 52 BA2 171 NC 172 NC

53 NC 1.8V 54 VDD 1.5v 173 VDD 地址线174 A12/BC# 地址线55 A11 空56 A7 175 A9 176 VDD 地址线57 VDD 1.5 58 A5 地址线177 A8 地址线178 A6 1.8v 59 A4 60 VDD 1.5v 179 VDD 1.5v 180 A3 地址线61 A2 地址线62 VDD 1.5v 181 A1 182 VDD 1.5v 63 CK1 时钟64 CK1# 时钟183 VDD 1.5v 184 CK0 时钟

65 VDD 1.5v 66 VDD 1.5v 185 CK0# 时钟信号186 VDD 1.5v 67 VREFCA 68 NC 空187 NC 188 A0 地址线69 VDD 1.5v 70 A10/AP 189 VDD 1.5v 190 BA1

71 BA0 72 VDD 1.5v 191 VDD 1.5v 192 RAS#

73 WE# 低电平信号74 CAS# 193 S0# 194 VDD 1.5v 75 VDD 1.5v 76 S1# 195 QDT0 196 A13 地址线77 QDT 78 VDD 1.5v 197 VDD 1.8v 198 NC 地址线79 NC 80 VSS 数据199 VSS 数据200 DQ36 数据81 DQ32 数据线82 DQ33 地址线201 DQ37 地址线202 VSS

注:DDR3内存插槽各针脚定义测试要点:电压、时钟、复位、复位168脚。