反相器设计实验

数字集成电路实验-反相器实验报告

第三次实验课 反相器(下)实验日期:20142.3 分析如下电路,解答下列问题上面的电路用两种方式实现了反相器,左图只使用了NMOS ,右图则使用了CMOS(NMOS 和PMOS)。

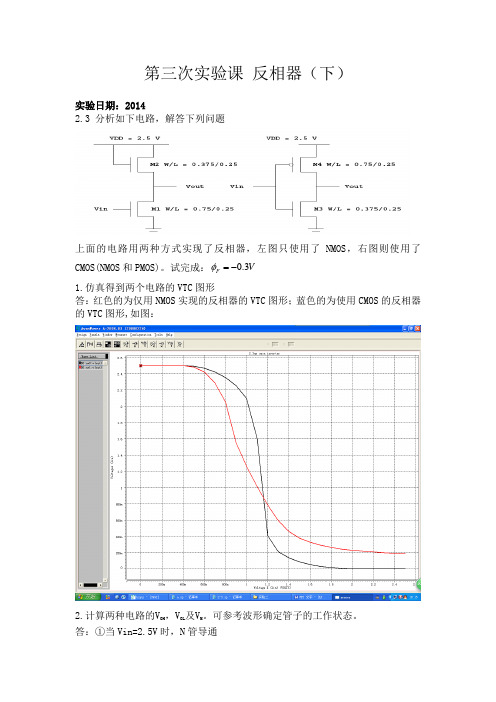

试完成:V F 3.0-=φ1.仿真得到两个电路的VTC 图形答:红色的为仅用NMOS 实现的反相器的VTC 图形;蓝色的为使用CMOS 的反相器的VTC 图形,如图:2.计算两种电路的V OH ,V OL 及V M 。

可参考波形确定管子的工作状态。

答:①当Vin=2.5V 时,N 管导通有在体偏置条件下阀值电压公式:)22(0F SB F T T V V V φφγ-+-+=()()()⎥⎦⎤⎢⎣⎡--=⎥⎦⎤⎢⎣⎡--=⎥⎦⎤⎢⎣⎡--=22220'2011'222'OL OL T in n DS DS T GS M M n d DSAT DSAT T DD M M n DSAT V V V V L W k V V V V L W k I V V V V L W k I (M2速度饱和)将下列数据代人VV V A k V V V D SAT n F T 63.0,/10115,3.0,43.026'0=⨯=-==-φ25.075.0,25.0375.01122==M M M M L W L W解得: V V OL 2875.0=当Vin=0V 时,N 管截止,Vout=OH V =2.5V求解M V :当out in V V =时,由于GS DS V V =,M1工作在饱和区此时流过M1(速度饱和)的电流为:()⎥⎥⎦⎤⎢⎢⎣⎡--=22011'1DSAT DSAT T in M M n DSAT V V V V L W k I (1) 流过M2的电流为(速度饱和)()⎥⎥⎦⎤⎢⎢⎣⎡---=2222'2DSAT DSAT T out DD M M n DSAT V V V V V L W k I (2) )22(0F SB F T T V V V φφγ-+-+=(3)M out in SB V V V V ===联立方程解得M V =1.017V②对于CMOS 器件当Vin=0时,V V V out O H 5.2==当Vin=2.5时,V V V out O L 0==求解M V :当out in V V =时,由于GS DS V V =,NMOS 与PMOS 工作在饱和区由于T M D SAT V V V -<,此时已经发生了速度饱和(参考波形)代入,联立解得:将下列数据V V V V V V V V V A k V A k L W k k L W k k V k V k r r V V V r V V V V V V V V k V V V V k DSATp DSATn Tp Tn p n pp p p nn n n DSATnn DSATpp DSAT TP DD DSAT Tn M DSATp Tp DD M DSATp p DSATn Tn M DSATn n 1,63.04.0,43.0,/1030,/101151)2/()2/(0)2/()2/(26'26'''-==-==⨯-=⨯====+++++==---+----M V =1.132315968V3.哪一种结构的反相器的功能性更好,为什么?(噪声容限,再生性,过渡区增益)答:CMOS 反相器更好。

反相器

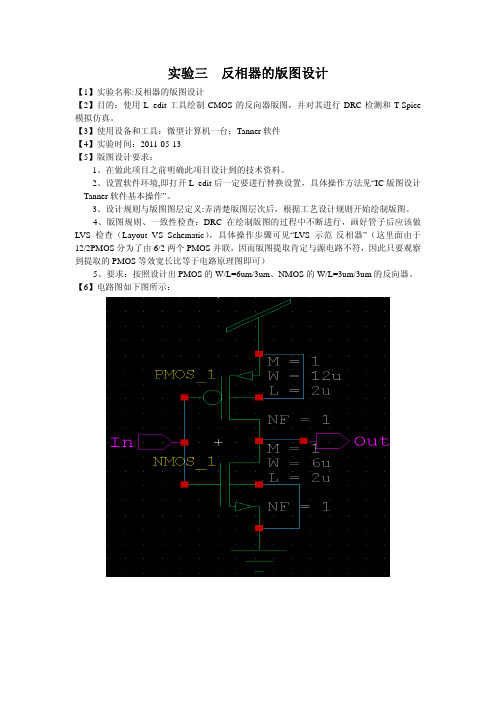

实验三反相器的版图设计【1】实验名称:反相器的版图设计【2】目的:使用L_edit工具绘制CMOS的反向器版图,并对其进行DRC检测和T-Spice 模拟仿真。

【3】使用设备和工具:微型计算机一台;Tanner软件【4】实验时间:2011-05-13【5】版图设计要求:1、在做此项目之前明确此项目设计到的技术资料。

2、设置软件环境,即打开L_edit后一定要进行替换设置,具体操作方法见“IC版图设计—Tanner软件基本操作”。

3、设计规则与版图图层定义:弄清楚版图层次后,根据工艺设计规则开始绘制版图。

4、版图规则、一致性检查:DRC在绘制版图的过程中不断进行,画好管子后应该做LVS检查(Layout VS Schematic),具体操作步骤可见“LVS示范-反相器”(这里面由于12/2PMOS分为了由6/2两个PMOS并联,因而版图提取肯定与源电路不符,因此只要观察到提取的PMOS等效宽长比等于电路原理图即可)5、要求:按照设计出PMOS的W/L=6um/3um、NMOS的W/L=3um/3um的反向器。

【6】电路图如下图所示:【7】具体绘制过程如下图所示;1、由于要求是需要那个规格为两个6/2 PMOS并联。

由于前面几次实验已经绘制过PMOS管的版图,所以这里就不详细的介绍。

将其连接起来如下图所示:2、反向器中还有一个NMOS,这个前面实验也绘制过,这里不详细的介绍绘制的过程。

结果如下图所示:3、输入输出端口的绘制,如下图所示:4、将绘制好的各种器件连接起来,并标注每个器件的名称( VDD,GND ,IN, OUT )结果如下图所示:5、绘制过程完成,下面进行仿真。

6、将反相器布局图成果转化成 T-Spice文件,可选择 Toos—Extract Setup命令(或单击按钮),打开Setup Extract 对话框,单击其中的按钮,在弹出的对话框中Browser选择D:\Documents and Settings\Administrator\My Documents\Tanner EDA\Tanner Tools v13.0\L-Edit and LVS\SPR\Lights\Layout\lights.ext,再到 Output 选项卡,SPICE include statement 文本框输入“.include F:\INV\bsim3_sample.md,点击提取按钮就可以了。

反相器实训报告

一、实验目的1. 理解反相器的工作原理,掌握反相器的设计方法;2. 学习使用模拟电路设计软件,进行反相器电路的搭建与仿真;3. 提高动手实践能力,培养团队协作精神。

二、实验原理反相器是一种基本的逻辑门电路,其功能是将输入信号进行反转输出。

本实验采用CMOS反相器,由P型MOSFET和N型MOSFET组成。

当输入信号为高电平时,P型MOSFET导通,N型MOSFET截止,输出信号为低电平;当输入信号为低电平时,P 型MOSFET截止,N型MOSFET导通,输出信号为高电平。

三、实验仪器与材料1. 实验仪器:示波器、信号发生器、电源、面包板、导线等;2. 实验材料:CMOS集成电路芯片、电阻、电容等。

四、实验步骤1. 设计反相器电路:根据实验要求,设计一个简单的CMOS反相器电路,并绘制电路原理图。

2. 电路搭建:按照电路原理图,在面包板上搭建反相器电路,包括P型MOSFET、N型MOSFET、电阻、电容等元件。

3. 信号输入:使用信号发生器产生不同幅值的正弦波信号,作为反相器的输入信号。

4. 信号采集:使用示波器分别测量反相器的输入信号和输出信号,观察信号的变化。

5. 数据分析:分析反相器的输入输出特性,验证反相器的工作原理。

6. 仿真实验:使用模拟电路设计软件,对反相器电路进行仿真实验,观察仿真结果与实际实验结果是否一致。

五、实验结果与分析1. 实验结果通过实际搭建电路和仿真实验,观察到了以下现象:(1)当输入信号为高电平时,输出信号为低电平;当输入信号为低电平时,输出信号为高电平。

(2)实际实验和仿真实验结果基本一致,说明实验设计合理,电路搭建正确。

2. 数据分析(1)输入输出特性:反相器的输入输出特性如图1所示。

当输入信号为高电平时,输出信号为低电平;当输入信号为低电平时,输出信号为高电平。

(2)电路功耗:反相器的功耗主要来源于电阻和电容的功耗。

在本实验中,电路功耗较小,约为几毫瓦。

六、实验总结1. 通过本次实验,掌握了反相器的工作原理,学会了反相器的设计方法。

反相器实验报告1

《VLSI》第一次实验报告系别:电子工程系班级:微电子11002学号:11160600230 姓名:赵良一、实验内容:1.对反相器电路进行Hspice仿真2.自己设计一个反相器电路版图。

3.用calibre工具绘制版图二、实验完成步骤及结果:1、反相器电路结构(绘制电路图)2、反相器电路的瞬态仿真1)仿真结果波形图截图2)测量t PLH和t PHL值、计算t P3)当t PLH =t PHL时P管和N管的宽度和长度1)2)t PLH=2 t PHL=2.46 t P =2.233)当t PLH =t PHL时P管=0.5u N管=1.5u3、反相器电路的直流仿真1)仿真结果波形图截图2)读取V M值3)改变W P/W N的大小,分别为2,3,4,记录V M的值。

1)2)V M=3)为2时V M=为3时V M=为4时V M=4、Hspice 网表文件(最终版)INVTER.protect.lib './TD-LO18-SP-2003v4R/l018ll_io50_v1p3.lib' TT.unprotect.temp 25.subckt invter in out vdd vssM0 out in vss vss n18ll L=0.18u W=0.72uM1 out in vdd vdd p18ll L=0.18u W=0.18u.endsx1 in out vdd vss invterC1 out vss 0.5pfVDD vdd 0 dc 'vddvalue_vdd'.param vddvalue_vdd=1.8vVSS vss 0 dc 'vddvalue_vss'.param vddvalue_vss=0vvin1 in 0 PWL 10ns 0v, 11ns 1.8v, 30ns 1.8v, 31ns 0v, 50ns 0v.dc vin1 0,1.8,.1 .tran 1ns 60ns.PROBE v(out) v(in) .end5、反相器版图三、调试和运行程序过程中产生的问题及采取的措施:问题:t PLH 和t PHL 的值一直不相等措施:多次取值选择其中最接近的一项。

反相器设计实验

实验一反相器电路设计一、实验目的和内容掌握反相器电路的设计流程。

完成反相器电路的设计和仿真,完成版图的设计及其DRC、LVS和LPE,最后完成后仿真。

二、实验器材1.计算机2.Cadence版图设计工具Virtuoso软件3.Hspice模拟电路仿真软件三、实验说明1.熟悉版图设计工具Virtuoso软件的操作,使用Virtuoso绘制反相器版图(Layout),利用Diva的DRC文件做设计规则检查,利用LVS文件做电路和版图的一致性检查。

2.熟悉Hspice软件的操作,使用Hspice验证反相器的电路特性。

四、SPICE仿真过程如何利用HSPICE对反相器电路进行仿真?以下是参考步骤:(1)利用windows自带的记事本编辑仿真程序,并把文件命名为inverter.sp。

(2)在记事本内编辑inverter.sp文件,程序说明如下:*Lab1Inverter.sp*********SPICE Library**************.include'hua05.sp'***************************************.global VDD GNDM1OUT IN VDD VDD PMOS W=20u L=0.6uM2OUT IN GND GND NMOS W=10u L=0.6uV1VDD GND5V2IN GND PULSE(050ns0.5ns0.5ns5ns10ns).OPTIONS POST.tran0.01ns100ns.end利用HSPICE对网表进行仿真,结果如下图所示:五、反相器Layout设计1.反相器的设计的设计经过以下几步:画n-well→PMOS和NMOS的active区→形成poly-si和栅氧化层→形成NMOS的源漏的掺杂→形成PMOS的源漏的掺杂→形成contact孔以及欧姆接触的重掺杂→形成金属层→金属层标注。

至此就完成了反相器Layout的设计。

实验一、反相器设计

实验一反相器设计一、实验目的1.学习tanner-pro中的s-edit,t-sipice和w-edit软件,完成inv的原理图设计与分析2.熟悉L-edit的使用,掌握L-edit进行集成电路版图设计的方法;3.掌握N/P MOS晶体管的工艺步骤、“N阱设计规则”。

4.掌握反相器的调试和性能指标测试方法5.掌握对反相器进行LVS的步骤与方法二、预习要求1、根据性能和指标要求,设计并计算电路的有关参数。

2、掌握s-edit编辑环境,设计inv的原理图3、掌握t-sipice和w-edit仿真环境,完成反相器的仿真4、掌握L-edit编辑环境,设计inv的版图5、掌握t-sipice和w-edit仿真环境,完成版图反相器的仿真6、掌握lvs环境变量7、写出预习报告三、反相器的设计方法1、确定电路(选择PMOS管、NMOS管)。

2、选择VDD和GND。

3、加入工作电源进行分析4、确定工艺规则。

5、绘制INV版图。

6、加入工作电源进行分析7、LVS比较四、实验内容1、设计一个具有反相器功能的电路。

反相器inv由一对互补的nmos和pmos管构成,通过对输入信号翻转完成输出信号,翻转时间长短有你nmos和pmos 工艺和尺寸决定,直接反映反相器的速度。

2、对所设计的电路进行设计、调试3、对电路的性能指标进行测试仿真,并改变设计参数(如沟道比等),对结果进行比较分析。

画出上述晶体管对应的版图,并且要求画出的版图在电学上,物理几何上,以及功能一致性上正确,版图的设计参考样式如下:4、版图规则/一致性检查对所设计的版图进行DRC、ERC规则检查对所设计的版图进行LVS一致性检查5、后仿真与改进对于设计的版图是否能够达到优异的性能,需要通过提取版图上的寄生参数,对含有版图寄生参数的电路进行仿真才能知道,很多时候版图上错误的走线,布图方法会导致致命的错误。

对于CMOS反相器版图设计,需要进行以下仿真:给反相器一个阶越信号的输入,观察反相器的输出信号的变化。

CMOS反相器的版图设计

实验一:CMOS反相器的版图设计一、实验目的1、创建CMOS反相器的电路原理图(Schematic)、电气符号(symbol)以及版图(layout);2、利用’gpdk090’工艺库实例化MOS管;3、运行设计规则验证(Design Rule Check,DRC)确保版图没有设计规则错误。

二、实验要求1、打印出完整的CMOS反相器的电路原理图以及版图;2、打印CMOS反相器的DRC报告。

三、实验工具Virtuoso四、实验内容1、创建CMOS反相器的电路原理图;2、创建CMOS反相器的电气符号;3、创建CMOS反相器的版图;4、对版图进行DRC验证。

1、创建CMOS反相器的电路原理图及电气符号图首先创建自己的工作目录并将/home/iccad/cds.lib复制到自己的工作目录下(我的工作目录为/home/iccad/iclab),在工作目录内打开终端并打开virtuoso(命令为icfb &).在打开的icfb –log中选择tools->Library Manager,再创建自己的库,在当前的对话框上选择File->New->Library,创建自己的库并为自己的库命名(我的命名为lab1),点击OK后在弹出的对话框中选择Attach to an exiting techfile并选择gpdk090_v4.6的库,此时Library manager的窗口应如图1所示:图1 创建好的自己的库以及inv创建好自己的库之后,就可以开始绘制电路原理图,在Library manager窗口中选中lab1,点击File->New->Cell view,将这个视图命名为inv(CMOS反相器)。

需要注意的是Library Name一定是自己的库,View Name是schematic,具体如图2所示:图2 inv电路原理图的创建窗口点击OK后弹出schematic editing的对话框,就可以开始绘制反相器的电路原理图(schematic view)。

CAD 反相器设计

GUIZHOU UNIVERSITY设计报告实验课程名称 CAD 实验实验项目名称反相器设计学院理学院专业班级电技091学生姓名学号指导教师周章瑜CMOS 反相器相当于非门,是数字集成电路中最基本的单元电路。

搞清楚CMOS 反相器的特性,可为复杂数字电路的设计打下基础。

如图所示电路为反相器,P 管衬底接Udd ,N 管衬底接地,栅极与各自的源极相接,消除了背栅效应,而且P 管和N 管轮流导通和截止,输出非0即Udd ,故CMOS 反相器又称为“无比电路”。

反相器的输入输出端口的关系如表一所示:表格 1 反相器输入输出端口 输入输出 10 01反相器关系式:OUT=~IN 。

一、使用S-Edit 编辑CMOS 反相器原理图在此次实例设计中采用Tanner Pro 软件中的S-Edit 组件设计CMOS 反相器的原理图,进而掌握S-Edit 的基本功能和使用方法。

操作流程如下:进入S-Edit —>建立新文件—>环境设置—>引用模块—>建立反相器电路。

1)打开S-Edit 程序,并将新文件另存以合适的文件名存储在一定的文件夹下:在自己的计算机上一定的位置处打开S-Edit 程序。

在本例中在S-Edit 文件夹中新建立“反相器原理图”文件夹,并将新文件以文件名“Ex1”存与此文件夹中。

如图1所示。

U1 UddV2U0V1图 CMOS 反相器图1 另存新文件为Ex12)环境设置:S-Edit默认的工作环境是黑底白线,但可以按照用户的喜好自行设定。

即选择Setup->Colors命令,打开Colors对话框,可分别设置背景色、前景色、选取颜色、栅格颜色、原点颜色和可更换颜色等。

如图2所示。

图2 环境设置3)编辑模块并浏览组件库:S-Edit编辑方式是以模块为单位而不是以文件为单位,一个文件中可以包含多个模块,而每一个模块则表示一种基本组件或者一种电路。

每次打开一个新文件时便自动打开一个模块并命名为“Module0”;也可以重命名模块名。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

实验一反相器电路设计

一、实验目的和内容

掌握反相器电路的设计流程。

完成反相器电路的设计和仿真,完成版图的设计及其DRC、LVS和LPE,最后完成后仿真。

二、实验器材

1.计算机

2.Cadence版图设计工具Virtuoso软件

3.Hspice模拟电路仿真软件

三、实验说明

1.熟悉版图设计工具Virtuoso软件的操作,使用Virtuoso绘制反相器版图

(Layout),利用Diva的DRC文件做设计规则检查,利用LVS文件做电路和版图的一致性检查。

2.熟悉Hspice软件的操作,使用Hspice验证反相器的电路特性。

四、SPICE仿真过程

如何利用HSPICE对反相器电路进行仿真?以下是参考步骤:

(1)利用windows自带的记事本编辑仿真程序,并把文件命名为inverter.sp。

(2)在记事本内编辑inverter.sp文件,程序说明如下:

*Lab1Inverter.sp

*********SPICE Library**************

.include'hua05.sp'

***************************************

.global VDD GND

M1OUT IN VDD VDD PMOS W=20u L=0.6u

M2OUT IN GND GND NMOS W=10u L=0.6u

V1VDD GND5

V2IN GND PULSE(050ns0.5ns0.5ns5ns10ns)

.OPTIONS POST

.tran0.01ns100ns

.end

利用HSPICE对网表进行仿真,结果如下图所示:

五、反相器Layout设计

1.反相器的设计的设计经过以下几步:

画n-well→PMOS和NMOS的active区→形成poly-si和栅氧化层→形成NMOS的源漏的掺杂→形成PMOS的源漏的掺杂→形成contact孔以及欧姆接触的重掺杂→形成金属层→金属层标注。

至此就完成了反相器Layout的设计。

我设计的反相器版图如下图所示:

2.DRC(Design Rules Check)版图设计规则检查

DRC检测的目的是:对IC版图做几何空间检查,以确保线路能够被特定加工工艺实现。

drc检测无错:

2.对版图进行lvs检测

Lvs检测的目的是将版图与电路原理图做对比,以检查电路的连接,与网表中MOS管的长宽值是否匹配。

Lvs版图与网表匹配:

3.寄生参数提取

寄生参数提取:从版图数据库提取电气参数(如MOS的W、L值BJT、二极管的面积,周长,结点寄生电容等)并以Hspice网表方式表示电路。

其结果如下图所示:

后仿真结果如下图所示:

七.实验心得体会

通过本次实验我了解了一个反相器设计的基本步骤,对软件的使用也已经变得

比较熟练,对数字集成电路设计有了一个宏观的理解,受益匪浅!。