数字集成电路反相器的设计

清华大学《数字集成电路设计》周润德 第5章 CMOS反相器

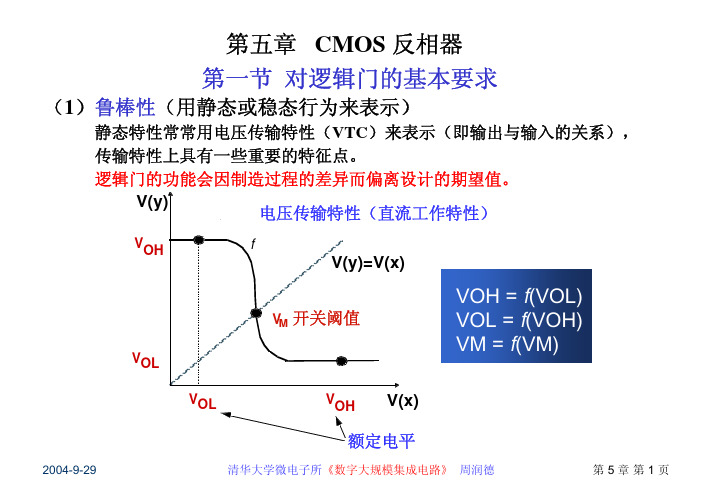

第五章 CMOS 反相器 第一节 对逻辑门的基本要求(1)鲁棒性(用静态或稳态行为来表示)静态特性常常用电压传输特性(VTC)来表示(即输出与输入的关系), 传输特性上具有一些重要的特征点。

逻辑门的功能会因制造过程的差异而偏离设计的期望值。

V(y) 电压传输特性(直流工作特性)VOH fV(y)=V(x)VM开关阈值VOL VOL VOHVOH = f(VOL) VOL = f(VOH) VM = f(VM)V(x)额定电平2004-9-29 清华大学微电子所《数字大规模集成电路》 周润德 第5章第1页(2)噪声容限:芯片内外的噪声会使电路的响应偏离设计的期望值 (电感、电容耦合,电源与地线的噪声)。

一个门对于噪声的敏感程度由噪声容限表示。

可靠性―数字集成电路中的噪声v(t) i(t)V DD电感耦合电容耦合电源线与地线噪声噪声来源: (1)串扰 (2)电源与地线噪声 (3)干扰 (4)失调 应当区分: (1)固定噪声源 (2)比例噪声源 浮空节点比由低阻抗电压源驱动的节点更易受干扰 设计时总的噪声容限分配给所预见的噪声源2004-9-29 清华大学微电子所《数字大规模集成电路》 周润德 第5章第2页噪声容限(Noise Margin)V“1” V OH V IHout OH 斜率 = -1V不确定区 斜率 = -1ILV “0” VVOLOL V IL V IH V in2004-9-29清华大学微电子所《数字大规模集成电路》 周润德第5章第3页噪声容限定义"1"噪声容限(Noise Margin) 容许噪声的限度V IH高电平 噪声容限VOHNM H未定义区 低电平 噪声容限V OL "0" NM L V IL抗噪声能力(Noise Immunity) 抑止噪声的能力门输出门输入2004-9-29清华大学微电子所《数字大规模集成电路》 周润德第5章第4页理想逻辑门V outg=∞Ri = ∞ Ro = 0 Fanout = ∞ NMH = NML = VDD/2V in2004-9-29清华大学微电子所《数字大规模集成电路》 周润德第5章第5页早期的逻辑门5.0 4.0 3.0 2.0 VM 1.0 NM H NM L0.01.02.03.0 V in (V)4.05.02004-9-29清华大学微电子所《数字大规模集成电路》 周润德第5章第6页(3) “再生”特性:逻辑门的“再生”特性使被干扰的信号能恢复到名义 的逻辑电平。

数字集成电路实验-反相器实验报告

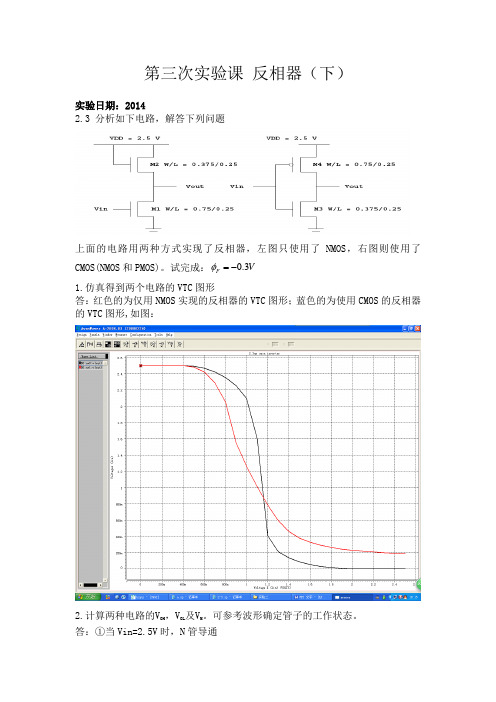

第三次实验课 反相器(下)实验日期:20142.3 分析如下电路,解答下列问题上面的电路用两种方式实现了反相器,左图只使用了NMOS ,右图则使用了CMOS(NMOS 和PMOS)。

试完成:V F 3.0-=φ1.仿真得到两个电路的VTC 图形答:红色的为仅用NMOS 实现的反相器的VTC 图形;蓝色的为使用CMOS 的反相器的VTC 图形,如图:2.计算两种电路的V OH ,V OL 及V M 。

可参考波形确定管子的工作状态。

答:①当Vin=2.5V 时,N 管导通有在体偏置条件下阀值电压公式:)22(0F SB F T T V V V φφγ-+-+=()()()⎥⎦⎤⎢⎣⎡--=⎥⎦⎤⎢⎣⎡--=⎥⎦⎤⎢⎣⎡--=22220'2011'222'OL OL T in n DS DS T GS M M n d DSAT DSAT T DD M M n DSAT V V V V L W k V V V V L W k I V V V V L W k I (M2速度饱和)将下列数据代人VV V A k V V V D SAT n F T 63.0,/10115,3.0,43.026'0=⨯=-==-φ25.075.0,25.0375.01122==M M M M L W L W解得: V V OL 2875.0=当Vin=0V 时,N 管截止,Vout=OH V =2.5V求解M V :当out in V V =时,由于GS DS V V =,M1工作在饱和区此时流过M1(速度饱和)的电流为:()⎥⎥⎦⎤⎢⎢⎣⎡--=22011'1DSAT DSAT T in M M n DSAT V V V V L W k I (1) 流过M2的电流为(速度饱和)()⎥⎥⎦⎤⎢⎢⎣⎡---=2222'2DSAT DSAT T out DD M M n DSAT V V V V V L W k I (2) )22(0F SB F T T V V V φφγ-+-+=(3)M out in SB V V V V ===联立方程解得M V =1.017V②对于CMOS 器件当Vin=0时,V V V out O H 5.2==当Vin=2.5时,V V V out O L 0==求解M V :当out in V V =时,由于GS DS V V =,NMOS 与PMOS 工作在饱和区由于T M D SAT V V V -<,此时已经发生了速度饱和(参考波形)代入,联立解得:将下列数据V V V V V V V V V A k V A k L W k k L W k k V k V k r r V V V r V V V V V V V V k V V V V k DSATp DSATn Tp Tn p n pp p p nn n n DSATnn DSATpp DSAT TP DD DSAT Tn M DSATp Tp DD M DSATp p DSATn Tn M DSATn n 1,63.04.0,43.0,/1030,/101151)2/()2/(0)2/()2/(26'26'''-==-==⨯-=⨯====+++++==---+----M V =1.132315968V3.哪一种结构的反相器的功能性更好,为什么?(噪声容限,再生性,过渡区增益)答:CMOS 反相器更好。

数字集成电路反相器

一、实验目的:

1、熟悉T-spice的使用,并且熟练掌握。

2、仿真出反相器的输出曲线,并观察它的特性。

二、实验原理:

CMOS反相器由一个P沟道增强型MOS管和一个N沟道增强型MOS管串联组成。

通常P 沟道管作为负载管,N沟道管作为输入管。

两个MOS管的开启电压VGS(th)P<0,VGS(th)N >0,通常为了保证正常工作,要求VDD>|VGS(th)P|+VGS(th)N。

若输入vI为低电平(如0V),则负载管导通,输入管截止,输出电压接近VDD。

若输入vI为高电平(如VDD),则输入管导通,负载管截止,输出电压接近0V。

三、实验步骤:

1、画出反相器的仿真图

实验小结:

通过这次Hspice仿真反相器的上机实验,我收获颇多。

第一、我更加熟悉了Hspice 仿真环境的使用,对T-spice更加的熟练。

这将对我以后再做其它实验奠定了良好的基础。

第二、以前只在课堂上听老师讲授那些反相器的原理和输出曲线等,但自己的意识当中对反相器的工作还是很疑惑,在做完这个仿真实验后,才恍然大悟,觉得反相器原来就是这么回事。

第三、反相器是我们学习数字集成电路的桥梁,我们后续将会用它进行许多的设计,所以这次实验的重要度是很高的。

我非常的重视这次实验。

集成电路课程设计--cmos反相器的电路设计及版图设计

目录摘要 (3)绪论 (5)1软件介绍及电路原理 (6)1.1软件介绍 (6)1.2电路原理 (6)2原理图绘制 (8)3电路仿真 (10)3.1瞬态仿真 (10)3.2直流仿真 (11)4版图设计及验证 (12)4.1绘制反相器版图的前期设置 (12)4.2绘制反相器版图 (13)4.3 DRC验证 (15)结束语 (17)参考文献 (18)摘要CMOS技术自身的巨大发展潜力是IC高速持续发展的基础。

集成电路制造水平发展到深亚微米工艺阶段,CMOS的低功耗、高速度和高集成度得到了充分的体现。

本文将简单的介绍基于ORCAD和L-EDIT的CMOS反相器的电路仿真和版图设计,通过CMOS反相器的电路设计及版图设计过程,我们将了解并熟悉集成电路CAD的一种基本方法和操作过程。

关键词:CMOS反相器ORCAD L-EDIT版图设计AbstractThe huge development potential of CMOS technology itself is the foundation of sustainable development of IC high speed. The manufacturing level of development of the integrated circuit to the deep sub micron technology, CMOS low power consumption, high speed and high integration have been fully reflected. In this paper, the circuit simulation and layout design of ORCAD and L-EDIT CMOS inverter based on simple introduction, through the circuit design and layout design process of CMOS inverter, we will understand and a basic method and operation process, familiar with IC CAD.Keywords: CMOS inverter layout ORCAD L-EDIT绪论20世纪是IC迅速发展的时代。

四CMOS反相器的设计

四CMOS反相器的设计CMOS反相器是一种使用互补金属氧化物半导体(CMOS)技术制造的电子电路元件,它能够将输入信号反向输出。

由于CMOS反相器具有低功耗、高噪声免疫性、广泛的电源电压范围和快速的切换速度等优点,因此被广泛应用于数字电路中。

接下来,我将详细介绍CMOS反相器的设计过程。

首先,我们需要选择适当的CMOS反相器拓扑结构。

在CMOS技术中,两种常见的CMOS反相器拓扑结构为P型金属氧化物半导体(PMOS)和N型金属氧化物半导体(NMOS)的串联结构,以及PMOS和NMOS的并联结构。

在本文中,我们选择串联结构的CMOS反相器作为设计示例。

接下来,我们需要设计PMOS和NMOS管的尺寸。

在CMOS技术中,尺寸设计对电路性能具有重要影响。

一般来说,PMOS管的尺寸应大于NMOS 管,以提高输出驱动能力。

此外,尺寸设计也需要考虑功耗和响应时间等因素。

在设计过程中,可以使用模拟电路设计工具进行参数优化,以获得最佳的尺寸方案。

接下来是电路的布线设计。

在CMOS反相器的布线设计中,需要考虑动态电压降、互连电容和电感等因素的影响。

在布线设计过程中,应将线宽和间距等参数进行折衷考虑,以满足电路性能和面积效益的要求。

设计完成后,需要进行电路的仿真验证和性能评估。

常用的仿真工具有HSPICE、LTSpice等。

在仿真过程中,可以通过输入不同的信号,并观察输出响应以评估电路的性能。

在CMOS反相器的设计中,还需要考虑到工艺和温度等因素的影响。

由于CMOS工艺受制于设备尺寸和工艺过程的变化,工艺参数的变化会导致电路性能产生偏差。

此外,温度对CMOS电路的性能也有显著影响,因此在设计中需要对工艺和温度进行适当的补偿。

最后,在设计完CMOS反相器后,还需要进行实际的制造和测试验证。

在制造过程中,需要遵循CMOS工艺流程,并进行工艺参数的控制和调整。

在测试验证过程中,可以使用专业的测试设备进行电路性能的测试和评估,以验证设计的正确性和可靠性。

CMOS反相器版图设计

XXXXXXX实验报告课程名称:集成电路设计实验名称:CMOS反相器版图设计学号姓名:指导教师评定:____________________________ 签名:_____________________________一、实验目的1、了解集成电路版图设计流程。

2、利用L-Edit 进行NMOSFET 版图设计。

3、利用L-Edit 进行CMOS反相器设计。

二、实验器材计算机一台,Tanner L-Edit软件三、实验原理CMOS 反相器由PMOS 和NMOS 晶体管组成,利用PMOS晶体管版图和NMOS 晶体管版图可以完成COMS反相器版图的设计。

四、实验步骤1、设计PMOS晶体管版图。

2、设计N MOS晶体管版图。

3、设计CMOS反相器版图:(1)启动版图编辑器L-Edit。

(2)新建文件。

新建一个Layout 文件,文件的设置信息可以从前面创建的文件中复制。

(3) 对文件进行重命名。

将L-Edit 编辑器默认的文件名Layout 改为Inverter。

(4) 设置格点与坐标。

格点与坐标的设定方式与创建PMOS 晶体管时设定的方法一致。

(5) 调用PMOS 和NMOS 晶体管作为例化单元。

使用Cell---Instance 命令来调用PMOS 单元。

在出现的Select Cell to Instance 对话框中,通过点击Browse按钮浏览到“MOS”文件,可以看到该文件下面有PMOS 和NMOS 两个单元,点击PMOS,然后点击“OK”,可以看到Inverter 文件cell0 单元的版图已经添加了PMOS 单元。

利用同样的方法,可以将NMOS 单元也添加进来。

(6) 连接PMOS 和NMOS 晶体管的栅极。

从CMOS 反相器电路可知,PMOS晶体管和NMOS 晶体管的栅极要连在一起作为反相器的输入端,所以在放置这两个晶体管的时候可以将两者的栅极对准,以便连接。

具体操作是,选择Layer的多晶硅(Poly)层和方框绘图工具后,在版图区域中画一个宽度与晶体管栅极相等的多晶硅矩形,如图1 所示。

cmos反相器逻辑电路设计的方法

cmos反相器逻辑电路设计的方法CMOS反相器是基本的逻辑门之一,可以用来构建更复杂的逻辑电路。

以下是设计CMOS反相器逻辑电路的方法:

1.选择合适的器件:CMOS反相器由PMOS和NMOS组成,

需要选择合适的器件来满足电路的要求。

通常,PMOS

的沟道为空穴,具有高电导率,适合作为开关,而NMOS

的沟道为电子,具有低电导率,适合作为负载。

2.设计电路结构:根据反相器的设计要求,设计电路结构,

包括PMOS和NMOS的排列方式、输入和输出的连接方式

等。

3.确定参数:根据电路的要求,确定参数,如阈值电压、

静态电流、动态电流等。

4.进行模拟验证:使用电路模拟软件进行验证,确认电路

的功能和性能是否达到设计要求。

5.进行版图设计:根据电路设计的要求,进行版图设计,

包括器件的排列、布线、电学参数的优化等。

6.进行制造和测试:将版图提交给制造厂家进行制造,并

进行测试,确认电路的性能和可靠性是否符合设计要

求。

需要注意的是,在设计CMOS反相器逻辑电路时,需要考虑电路的稳定性、速度、功耗等因素,以满足实际应用的要求。

同时,还需要遵循基本的电路设计规则和安全规范,如避免电流过大、避免信号过冲等。

数字集成电路设计第5章cmos反相器教材

线性化

Ceq = Keq Cj0

高到低 低到高 Keqbp Keqsw Keqbp Keqsw NMOS 0.57 0.61 0.79 0.81

PMOS

0.79

0.86

0.59

0.7

2019/4/17

33

一个0.25umCMOS反相器的电容

2019/4/17

27

即使电源电压很低时,晶体管仍能导通,仍然 具有反相器的特性,因为亚阈值电流足以使该门在 低电平和高电平之间切换,并提供足够的增益从而 得到可接受的VTC。

但使得门的特性变的很差。VOL和VOH不再等于 电源的两个电平,并且过渡区的增益接近1。 为了能得到足够的增益以用于数字电路,必须使 电源为热电势的两倍,否则就只能降低热电势,即 降低环境温度,冷却该电路

能量效率:由能耗和功耗决定。

2019/4/17 2

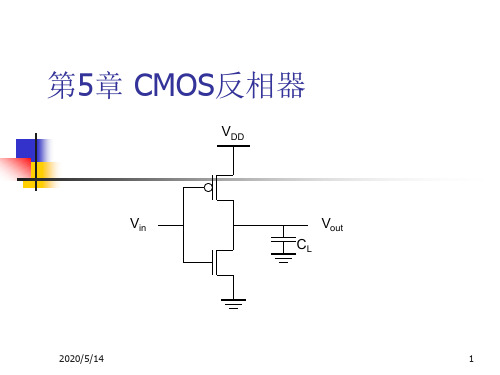

5.2静态CMOS反相器—综述

VDD

Vin CL

Vout

把MOS晶体管当成简单的开关模型。即晶体管只不过是一个具有无限关断电阻 和有限导通电阻的开关。(VGS与VT 的关系所决定)

2019/4/17 3

VDD

VDD

VDD

0 0

CL

CL

VDD CL

2019/4/17

7

IDn

IDSp = -IDSn VGSn = Vin ; VGSp = Vin - VDD VDSn = Vout ; VDSp = Vout - VDD

Vout

Vin = 0 Vin = 1.5

Vin = 0 Vin = 1.5

VGSp = -1 VGSp = -2.5

Vin = VDD + VGSp IDn = -IDp

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

他们和理想逻辑电平之间的范围为CMOS电路的直流噪声容限。

VTH VOH VC2 VDD VC 2

VNL VC1 VOL VC1

若CMOS反相器中的NMOS晶体管和PMOS晶体管性能完全对称,即

VTN VTP VT 及 K N KP

3.由反相器阈值点定义的最大噪声容限

CMOS反相器的阈值点是反相器状态变化的临界点,当输入小于反相器阈值 时,输出必然大于反相器的阈值;反之也成立。若以反相器的阈值作为所允 许的最坏输入电平,则阈值点与理想逻辑电平之间的范围就是CMOS反相器 的最大的噪声容限,即

VTHM VDD Vit

VNLM Vit

(2) VTN Vin Vout VTP (如bc段)

在此范围内,NMOS管导通,工作在饱和区,PMOS管仍工作在线性区,由

可得到 IDN IDP

12

V V V V V V V Vout

in

TP

2

1

in

TP

DD

0

2

in

TN

其中

0 KP KN

特点:

Vin作为PMOS和NMOS的共栅极; Vout作为共漏极; VDD作为PMOS的源极和体端; GND作为NMOS的源极和体端

第一章 概 论

5.1 CMOS反相器的直流特性

第一章 概 论

5.1 CMOS反相器的直流特性

对称的电流方程

第一章 概 论

电流方程如下:设 Vtn = -Vtp

V 0

第一章 概 论

5.3 CMOS反相器的瞬态特性

当CMOS反相器的输入信号随时间变化时,输出电平要随之变化,由于输出节电 存在着容性负载,在输出电平变化的过程中,需要对输出节点的负载电容充放电, 由此决定了电路的瞬态特性。 阶跃输入情况:

在阶跃输入的近似下,可以用反相器的上升时间 tr 和下降时间 t f 来反映反相器

IDN IDP 0

KP

V inV TPV

DD

2

V inV TPV out

2

0

由此得到

V V

out

DD

这就使输出高电平区,故CMOS反相器输出高电平等于电

源电压

V V

OH

DD

如直流电压传输特性曲线中的ab段

第一章 概 论

5.1 CMOS反相器的直流特性

VTH VOH VON VDD VON

输入低电平时的噪声容限为

VNL VOFF VOL VOFF

第一章 概 论

5.2CMOS反相器的直流噪声容限

1.由极限输出电平定义的噪声容限

第一章 概 论

5.2CMOS反相器的直流噪声容限

2.由单位增益点定义的噪声容限 在增益为0和增益很大的输入电平的区域之间必然存在单位增益点,即

V inVTP V

S

2

V inVTP V D

V V 2

in

out VTP线性

第一章 概 论

5.1 CMOS反相器的直流特性

在直流情况下,反相器没有输出电流,总满足

IDN IDP

(1)

V V 0

in

TN

(如ab段)

在此范围内,NMOS管截止,PMOS管工作在线性区

第一章 概 论

2.CMOS反相器的下降时间 类似于上升时间的推导,可以得到u从0.9下降到0.1所需要 的下降时间:

tf

N

1

N

0.1

2

N

1

2 1 N

ln

1.9

2

in

TN

in

TN 2 0

in

TP

2

1

2

DD

第一章 概 论

5.1 CMOS反相器的直流特性

(5) VDD Vin VDD VTP (如ef段) 在这个区域,PMOS管由导通变成截止,而NMOS管仍然在线性导通区。由

于PMOS管截止,使得

IDN IDP 0

P

总的上升过程包括饱和区充电与非饱和区充电两段时间。

使u从0.1达到0.9所需要的上升时间为

tr

P

P

1

0.1

P 2

1

21P

ln

1.9

2

0.1

P

第一章 概 论

2.CMOS反相器的下降时间 当输入信号从低电平跃变到高电平时,CMOS反相器中的PMOS管截止,

Vit VTN

0

1

VDD VTP

0

第一章 概 论

5.1 CMOS反相器的直流特性

(4) Vout VTN Vin VDD VTP (如de段) 在此区域内,NMOS管进入线性导通区,而PMOS管仍工作在饱和区,由

可得到

IDN IDP

V V V V V V V Vout

out VTN

线性

in

I V V V V V V VV V p

0

K

P

in

TP

S

2

DD

VTP

out

in

VTP

截止

DD

in

DD VTP饱和

K

P

的瞬态特性。上升时间定义为使反相器的输出电平从高电平的10%上升到高电平 的90%所需要的时间;下降时间定义为输出电平从高电平的90%下降到高电平的 10%所需要的时间。 分析采用以下近似: (1)输入信号是理想的方波; (2)忽略MOS晶体管本身的驰豫时间; (3)把与输出节点相联系的所有本征电容和寄生电容等效为一个常值的集总负载

in VTN 0截止

I V V V V V n KN

in TN

2

S

VTN

in

out VTN 饱和

KN

V inVTN

VS

2

V inVTN V D

V V 2

输特性曲线将向右偏移。

第一章 概 论

5.1 CMOS反相器的直流特性

器件参数对CMOS反相器电平传输特性的影响

第一章 概 论

5.2CMOS反相器的直流噪声容限

为了反映逻辑电路的抗干扰能力,引入了直流噪声容限作为电路性能参数。 直流噪声容限反映了电流能承受的实际输入电平与理想逻辑电平的偏离范围。 1.由极限输出电平定义的噪声容限

31 VC1 8VDD 4 VT

,则可以得到

VC 2

5 8

VDD

1 4

VT

这种情况下,CMOS反相器的输入高电平和输入低电平的噪声容限相等,

VTH

VNL

3 8

VDD

1 4

VT

第一章 概 论

5.2CMOS反相器的直流噪声容限

2.由单位增益点定义的噪声容限

第一章 概 论

5.2CMOS反相器的直流噪声容限

叫做CMOS反相器的比例因子,它是CMOS反相器的重要设计参数,在一定工艺条

件下其决定于PMOS管和NMOS管的宽长比。

第一章 概 论

5.1 CMOS反相器的直流特性

(3)Vout VTP Vin Vout VTN (如cd段)

在这个区域,NMOS管和PMOS管都处在饱和区,因此有

Vi Vth

第一章 概 论

引入归一化输入、输出电平表示CMOS反相器的电压传输特性。定义归一化

电平:

N

VTN VDD

P

VTP VDD

u Vout VDD

v Vin VDD

在对称情况下,CMOS反相器的传输特性可简单地表示为

(1) v N , u 1

(2) N v vit ,u v N 1 2N 1 2v

(1)在 N P 平 vit 0.5 ;若

vit 0.5 。

情况下,若 0 1 ,则反相器的阈值电 0 1 ,则 vit 0.5 ;若 0 1 ,则

(2)在 N P 情况下, N 减小使输出电平更早地开始下降,传输特 性曲线向左偏移,若 P 减小,则使输出电平更晚地达到低电平(0V),传

电容 CL 。

第一章 概 论

5.3 CMOS反相器的瞬态特性

1.CMOS反相器的上升时间

当输入信号从高电平跃变到低电平时,CMOS反相器中的NMOS管截止, PMOS管导通,靠PMOS管的导通电流对输出结点的负载电容充电,使输出上

升为高电平。在上升过程中 Vin 0 ,PMOS管是在恒定栅源电压下,

当CMOS反相器中的两个管子完全对称时,有

VTHM

VNLM

VDD 2

实际管子很难完全对称,使得 VTHM VNLM ,它们中较小的一个决定了电路

所能承受的最大直流噪声容限。

VTHM VNLM VDD

第一章 概 论

5.2CMOS反相器的直流噪声容限