数字集成电路分析与设计考试(广工)

GDOU广东海洋大学数字电路试题集1

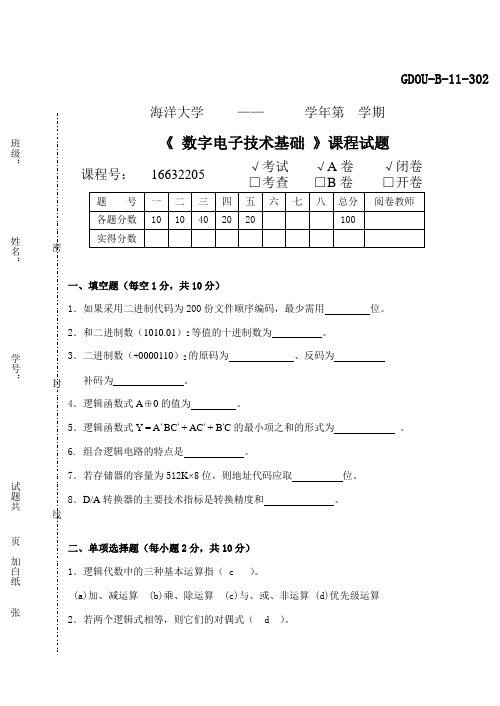

海洋大学 —— 学年第 学期《 数字电子技术基础 》课程试题课程号: 16632205√ 考试 √ A 卷 √ 闭卷□ 考查□ B 卷□ 开卷一、填空题(每空1分,共10分)1.如果采用二进制代码为200份文件顺序编码,最少需用 位。

2.和二进制数(1010.01)2等值的十进制数为 。

3.二进制数(+0000110)2的原码为 、反码为补码为 。

4.逻辑函数式A ⊕0的值为 。

5.逻辑函数式Y = A ′ BC ′ + AC ′ + B ′C 的最小项之和的形式为 。

6. 组合逻辑电路的特点是 。

7.若存储器的容量为512K×8位,则地址代码应取 位。

8.D/A 转换器的主要技术指标是转换精度和 。

二、单项选择题(每小题2分,共10分) 1.逻辑代数中的三种基本运算指( c )。

(a)加、减运算 (b)乘、除运算 (c)与、或、非运算 (d)优先级运算 2.若两个逻辑式相等,则它们的对偶式( d )。

班级:姓名:学号:试题共页加白纸张密封线GDOU-B-11-302(a)不一定相等 (b)可能为0 (c) 可能为1 (d) 一定相等 3.正逻辑的高电平表示为( b )。

(a) 0 (b)1 (c)原变量 (d)反变量 4.三态门电路的输出可以为高电平、低电平及( c )。

(a)0 (b)1 (c)高阻态 (d)导通状态 5.随着计数脉冲的不断输入而作递增计数的计数器称为( a )。

(a)加法计数器 (b)减法计数器 (c)可逆计数器 (d)加/减计数器 三、分析题(每小题10分,共40分)1.已知逻辑函数Y 1 和Y 2的真值表如表1所示,试写出Y 1 和Y 2的逻辑函数式。

表12.分析图1所示时序电路的逻辑功能,写出电路的驱动方程、状态方程和输出方程,画出电路的状态转换图和时序图。

图13.写出如图2A B C Y 0 0 00 0 10 1 00 1 11 0 01 0 11 1 01 1 1Y 121 11 00 10 01 11 00 11 0F=ABC+ABC+ABA B C图24.由两个三态门组成的逻辑电路如图3所示,试分析其逻辑功能。

集成电路设计岗位招聘笔试题与参考答案(某大型集团公司)

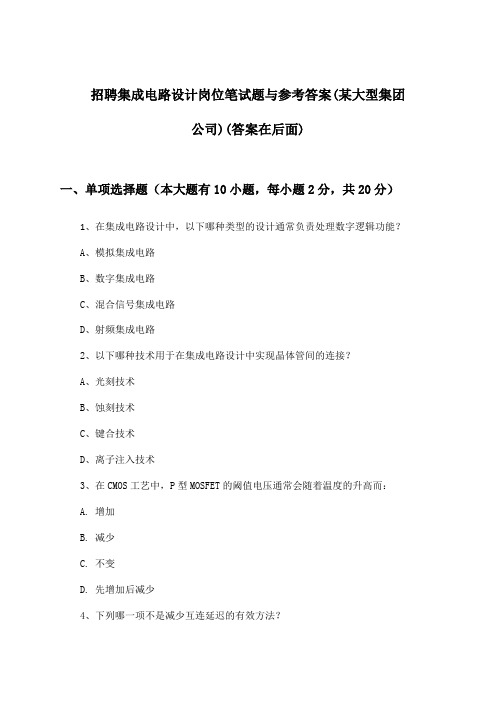

招聘集成电路设计岗位笔试题与参考答案(某大型集团公司)(答案在后面)一、单项选择题(本大题有10小题,每小题2分,共20分)1、在集成电路设计中,以下哪种类型的设计通常负责处理数字逻辑功能?A、模拟集成电路B、数字集成电路C、混合信号集成电路D、射频集成电路2、以下哪种技术用于在集成电路设计中实现晶体管间的连接?A、光刻技术B、蚀刻技术C、键合技术D、离子注入技术3、在CMOS工艺中,P型MOSFET的阈值电压通常会随着温度的升高而:A. 增加B. 减少C. 不变D. 先增加后减少4、下列哪一项不是减少互连延迟的有效方法?A. 使用更细的金属线B. 使用更高介电常数的绝缘材料C. 减少金属层之间的距离D. 使用铜代替铝作为互连线材料5、集成电路设计中,以下哪种工艺主要用于制造CMOS(互补金属氧化物半导体)逻辑电路?A. 双极型工艺B. 金属氧化物半导体工艺C. 双极型/金属氧化物半导体混合工艺D. 双极型/CMOS混合工艺6、在集成电路设计中,以下哪个参数通常用来描述晶体管的开关速度?A. 饱和电压B. 输入阻抗C. 开关时间D. 集成度7、在集成电路设计中,用于描述电路逻辑功能的硬件描述语言不包括以下哪一种?A. VerilogB. VHDLC. C++D. SystemVerilog8、下列选项中,哪一个不是ASIC(专用集成电路)设计流程中的一个阶段?A. 逻辑综合B. 布局布线C. 系统集成D. 物理验证9、以下哪种工艺技术通常用于制造高性能的集成电路?A. 混合信号工艺B. CMOS工艺C. GaN(氮化镓)工艺D. BiCMOS工艺二、多项选择题(本大题有10小题,每小题4分,共40分)1、在CMOS工艺中,关于阱(well)的概念,下列说法正确的有:A. NMOS晶体管通常位于P型阱中B. PMOS晶体管通常位于N型阱中C. N阱用于隔离不同区域的晶体管,防止电流泄露D. P阱可以与N阱共存于同一层硅片上而不会相互影响2、关于集成电路版图设计中的DRC(Design Rule Check)规则,下列哪些陈述是正确的?A. DRC规则是为了确保电路性能优化B. DRC规则定义了最小特征尺寸、最小间距等制造限制C. 违反DRC规则可能会导致制造缺陷,如短路或开路D. DRC规则在所有半导体制造工艺中都是相同的3、关于集成电路设计,以下哪些是典型的电路设计类型?()A、模拟电路设计B、数字电路设计C、混合信号电路设计D、射频电路设计E、光电子电路设计4、在集成电路设计中,以下哪些因素会影响电路的功耗?()A、晶体管的工作状态B、电源电压C、电路的复杂度D、芯片的温度E、外部负载5、在集成电路设计过程中,下列哪些技术用于提高电路的性能?A. 使用更先进的制程技术B. 优化电路布局减少信号延迟C. 增加电源电压以提升速度D. 减少电路层数降低制造成本E. 应用低功耗设计方法6、下列哪些是实现CMOS逻辑门时需要考虑的关键因素?A. 输入电平的阈值B. 输出驱动能力C. 功率消耗D. 静态电流消耗E. 电路的工作频率7、以下哪些技术或方法属于集成电路设计中的模拟设计领域?()A. 信号处理算法B. 逻辑门电路设计C. 模拟电路仿真D. 功耗分析E. 版图设计8、在集成电路设计中,以下哪些步骤是进行版图设计的必要阶段?()A. 电路原理图设计B. 布局规划C. 逻辑分割D. 布局布线E. 版图检查9、在CMOS工艺中,影响MOSFET阈值电压的因素有哪些?A. 氧化层厚度B. 衬底掺杂浓度C. 栅极材料类型D. 源漏区掺杂浓度E. 温度F. 器件尺寸三、判断题(本大题有10小题,每小题2分,共20分)1、集成电路设计岗位的工程师需要具备扎实的数学基础和电子工程知识。

华南理工大学数字电子技术试卷(含答案)

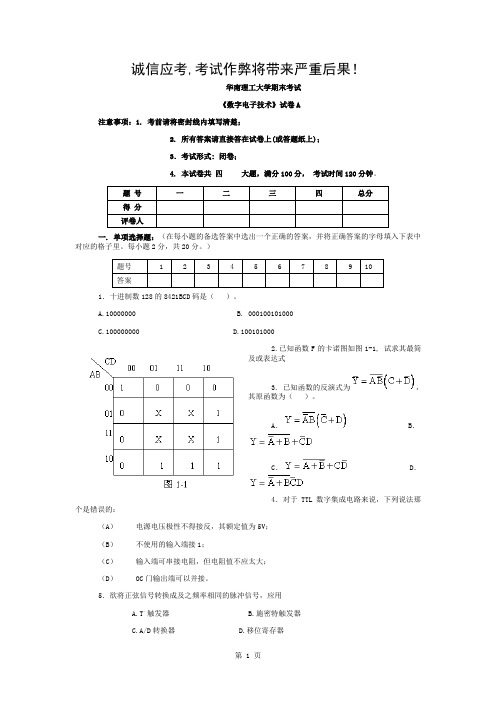

诚信应考,考试作弊将带来严重后果!华南理工大学期末考试《数字电子技术》试卷A注意事项:1. 考前请将密封线内填写清楚;2. 所有答案请直接答在试卷上(或答题纸上);3.考试形式: 闭卷;4. 本试卷共四大题,满分100分,考试时间120分钟。

题号一二三四总分得分评卷人一. 单项选择题:(在每小题的备选答案中选出一个正确的答案,并将正确答案的字母填入下表中对应的格子里。

每小题2分,共20分。

)题号12345678910答案1.十进制数128的8421BCD码是()。

A.10000000B. 000100101000C.100000000D.1001010002.已知函数F的卡诺图如图1-1, 试求其最简及或表达式3. 已知函数的反演式为,其原函数为()。

A. B.C. D.4.对于TTL数字集成电路来说,下列说法那个是错误的:(A)电源电压极性不得接反,其额定值为5V;(B)不使用的输入端接1;(C)输入端可串接电阻,但电阻值不应太大;(D) OC门输出端可以并接。

5.欲将正弦信号转换成及之频率相同的脉冲信号,应用A.T,触发器B.施密特触发器C.A/D转换器D.移位寄存器6.下列A/D转换器中转换速度最快的是()。

A.并联比较型B.双积分型C.计数型D.逐次渐近型7. 一个含有32768个存储单元的ROM,有8个数据输出端,其地址输入端有()个。

A. 10B. 11C. 12D. 88. 如图1-2,在TTL门组成的电路中,及非门的输入电流为I iL≤–1mA‚I iH≤20μA。

G1输出低电平时输出电流的最大值为I OL(max)=10mA,输出高电平时最大输出电流为I OH(max)=–0.4mA 。

门G1的扇出系数是()。

A. 1B. 4C. 5D.109.十数制数2006.375转换为二进制数是:A. 11111010110.011B.1101011111.11C. 11111010110.11D. 1101011111.01110. TTL或非门多余输入端的处理是:A. 悬空B. 接高电平C. 接低电平D.接”1”二.填空题(每小题2分,共20分)1.CMOS传输门的静态功耗非常小,当输入信号的频率增加时,其功耗将______________。

最新深圳大学数字电路试题B参考答案及评分标准

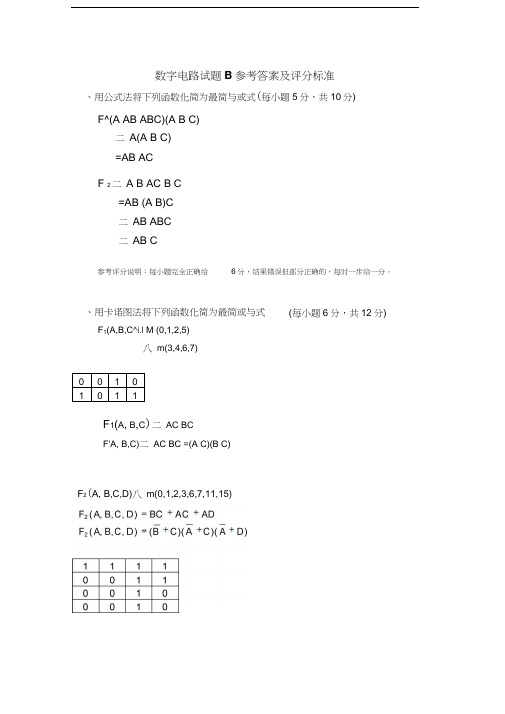

数字电路试题B参考答案及评分标准、用公式法将下列函数化简为最简与或式(每小题5分,共10分) F^(A AB ABC)(A B C)二A(A B C)=AB ACF 2 二A B AC B C=AB (A B)C二AB ABC二AB C参考评分说明:每小题完全正确给6分,结果错误但部分正确的,每对一步给一分。

(每小题6分,共12分)、用卡诺图法将下列函数化简为最简或与式F1(A,B,C^i.l M (0,1,2,5)八m(3,4,6,7)0 0 1 01 0 1 1F1(A, B,C)二AC BCF'A, B,C)二AC BC =(A C)(B C)F2(A, B,C,D)八m(0,1,2,3,6,7,11,15)参考评分说明:每小题结果完全正确给6分,每小题卡诺图正确给3分,结果错误但部分正确的,每对一步给一分。

三、利用卡诺图法将下列函数化简为最简与或式。

(每小题6分,共12分)F, (A, B, C, D) = ABC BCD AD AB CDF;(A,B,C, D)二ABC BCD AD AB CD= ABC BCD AD AB ACD画F,(A, B,C,D)的卡诺图如下:F,(代B,C,D =AC ABD A BD F,(A, B,C,D =AC ABD ABDF2(A,B,C,D)八m(3,5,6,7,10) 、d 0,1,2,4,8F2(A, B,C,D) =A BD参考评分说明:每小题结果正确给6分,每小题卡诺图正确给3分,结果错误但部分正确的,每对一步给一分。

四、用与非门设计一个四变量的多数表决电路,当输入变量有3个或3个以上为1时输出为1,输入为其它状态时输出为0。

( 15分)解:设A,B,C,D表示输入逻辑变量,丫表示投票结果输出,其真值表如下:根据真值表画出卡诺图,如下:由卡诺图,得Y = ABC + ABD + ACD + BCD二ABC ABD ACD BCD=ABC A BD ACD BCD根据逻辑表达式,画逻辑电路图如下参考评分说明:结果正确给15分,真值表正确给5分,卡诺图正确给2分,逻辑表达式正确给3分,逻辑电路图正确给5分,结果错误但部分正确的,每对一步酌情给分,但不超出各部分给定的分值。

集成电路应用工程师招聘笔试题及解答2024年

2024年招聘集成电路应用工程师笔试题及解答(答案在后面)一、单项选择题(本大题有10小题,每小题2分,共20分)1.(数字)集成电路中,逻辑门电路是构成各种逻辑功能的基本单元。

2.(数字)数字电路设计中,集成电路芯片的功耗主要由电压决定,与电流无关。

3.(数字)模拟信号与数字信号在集成电路中的转换,一般需要通过模数转换器(ADC)或数模转换器(DAC)。

4.(数字)集成电路制造工艺中,光刻技术主要用于制作电路图案。

3.集成电路中,哪种类型的晶体管具有高速、低噪声和良好的频率响应特性?A. 二极管B. 晶体管(BJT)C. 场效应晶体管(FET)D. 变压器4.在集成电路设计中,哪种封装形式最适合用于大批量生产和应用?A. 插件式B. 芯片级封装C. 陶瓷封装D. 环氧树脂封装5.在集成电路设计中,以下哪个选项是常用的数字信号处理算法?A.傅里叶变换B.卷积运算C.快速傅里叶变换D.以上都是6.集成电路的哪种封装形式主要用于高性能、高频率的芯片?A.针脚式B.表面贴装式(SMD)C.插件式D.以上都是7.在集成电路设计中,以下哪个因素对电路的性能影响最大?A. 电源电压B. 地线布局C. 热设计D. 噪声干扰8.以下哪种封装形式适用于高集成度的集成电路芯片?A. 芯片上引线封装B. 插件式封装C. 塑料封装D. 模块化封装9.在集成电路设计中,以下哪个步骤不属于常见的工艺步骤?A. 物理验证B. 逻辑综合C. 器件建模D. 芯片封装 10. 在CMOS工艺中,以下哪种器件主要用于实现电流放大?A. 晶体管B. 反相器C. 二极管D. 传输门二、多项选择题(本大题有10小题,每小题4分,共40分)1.关于集成电路的基本构成,以下哪些说法是正确的?A. 集成电路主要由晶体管构成B. 集成电路的集成度越高,电路性能越好C. 集成电路中不包括电容器和电阻器D. 集成电路由多个电子元器件集成在一起形成微型化电路2.在集成电路设计中,以下哪些因素是必须考虑的?A. 工艺制造能力B. 市场需求和趋势C. 硬件资源的成本D. 操作系统的兼容性3.在集成电路设计中,以下哪个选项是用来描述电路性能的主要参数?A. 电阻B. 电容C. 速度D. 功率E. 电流4.集成电路的制造工艺通常包括哪些步骤?A. 设计B. 制版C. 制造D. 装配E. 测试5.关于集成电路的应用,以下哪些说法是正确的?A. 集成电路主要应用在计算机硬件领域。

集成电路设计原理考核试卷

4.描述模拟集成电路与数字集成电路在设计原则和实现技术上的主要区别,并给出一个实际应用中模拟集成电路的例子。

标准答案

一、单项选择题

1. B

2. B

3. D

4. D

5. B

6. D

7. C

8. C

9. B

10. D

17.在集成电路设计中,以下哪些方法可以提高电路的抗干扰能力?( )

A.采用差分信号传输

B.使用屏蔽技术

C.增加电源滤波器

D.提高工作频率

18.以下哪些类型的触发器在数字电路中常见?( )

A. D触发器

B. JK触发器

C. T触发器

D. SR触发器

19.以下哪些技术可以用于提高集成电路的数据处理速度?( )

3.以下哪些是数字集成电路的基本组成部分?( )

A.逻辑门

B.触发器

C.寄生电容

D.晶体管

4.以下哪些技术可以用于提高集成电路的频率?( )

A.减小晶体管尺寸

B.采用高介电常数材料

C.增加电源电压

D.优化互连线设计

5.在CMOS工艺中,以下哪些结构可以用来实现反相器?( )

A. PMOS晶体管

B. NMOS晶体管

11. C

12A

16. B

17. A

18. A

19. C

20. B

二、多选题

1. ABD

2. AB

3. AD

4. AB

5. AB

6. AB

7. ABCD

8. AB

9. ABCD

10. AC

11. ABC

数字集成电路分析与设计 第三章答案

CHAPTER 3P3.1. The general approach for the first two parameters is to figure out which variables shouldremain constant, so that when you have two currents, you can divide them, and every variable but the ones you want to calculate remain. In this case, since the long-channel transistor is in saturation for all values of V GS and V DS , only one equation needs to be considered:()()2112DS N OX GS T DS W I C V V V Lμλ=-+ For the last two parameters, now that you have enough values, you can just choose oneset of numbers to compute their final values.a. The threshold voltage, V T0, can be found by choosing two sets of numbers with the same V DS ’s but with different V GS ’s. In this case, the first two values in the table can be used.()()()()()()211122222201022001121121.2 1.210000.82800.8DS N OX GS T DS DS N OX GS T DS T DS T DS T T W I C V V V L W I C V V V LV I V I V V μλμλ=-+=-+-⎛⎫-===⎪--⎝⎭ 00.35V T V ∴=b. The channel modulation parameter, λ, can be found by choosing two sets of numberswith the same V GS ’s but with different V DS ’s. In this case, the second and third values in the table can be used.()()221 1.225010.8247DS DS I I λλ+==+ -10.04V λ∴=c. The electron mobility, µn , can now be calculated by looking at any of the first three sets of numbers, but first, let’s calculate C OX .631062-31m 10μm22?.210μm1m 10 0.0351 1.610/2.210OX OX t C F cm--=⨯⨯===⨯Now calculate the mobility by using the first set of numbers.()()()()()()()()()()()()22111021262101111 1.21 1.222210002cm 348V-s 1.610(4.75)1.20.3510.04 1.21DS N OX GS T DS N OX T DS N OX GS T DS W W I C V V V C V L LA I W C V V V L μλμλμμλ-=-+=-+===⨯-+-+d. The body effect coefficient gamma, γ, can be calculated by using the last set of numbers since it is the only one that has a V SB greater than 0V.()()()()244124414411221 1.20.468VDS N OX GS T DS DS GS T N OX DS GS T T GS W I C V V V LI V V W C V LV V V V μλμλ=-+-=+-==-==12000.6VT T T T V V V V γγγ=+-====P3.2. The key to this question is to identify the transistor’s region of operation so that gatecapacitance may be assigned appropriately, and the primary capacitor that will dischargedat a rate of V It C ∂∂= by the current source may be identified. Then, because the nodes arechanging, the next region of operation must be identified. This process continues until the transistor reaches steady state behavior. Region 1:Since 0V GS V = the transistor is in the cutoff region. The gate capacitance is allocated to GB C . Since no current will flow through the transistor, all current will come from the source capacitor and the drain node remains unchanged.68-151010V V 6.67100.6671510s nsSB V I I t C C -∆⨯====⨯=∆⨯ The source capacitor will discharge until 1.1V GS T V V == when the transistor enters thesaturation region. This would require that the source node would be at 3.3 1.1 2.2V S G GS V V V =-=-=.()15961510 3.3 2.2 1.6510s 1.65ns 1010C t V I ---⨯∆=∆=-=⨯=⨯ Region 2:The transistor turns on and is in saturation. The current is provided from the capacitor atthe drain node, while the source node remains fairly constant. The capacitance at the drain node is the same as the source node so the rate of change is given by:68-151010V V 6.67100.6671510s nsSB V I I t C C -∆⨯====⨯=∆⨯ Since the transistor is now in the saturation region, GS V can be computed based on thecurrent flowing through the device.()22 1.1 1.37V 3.3 1.37 1.93VGS T GST S G GS kW I V V LV V V V V =-==+==-=-=This is where the source node settles. This means that most of the current is discharged through the transistor until the drain voltage reaches a value that puts the transistor at the edge of saturation.3.3 1.1 2.2VDS GS TD G T V V V V V V =-=-=-=If we assume that all the current comes from the transistor, and the source node remains fixed, the drain node will then discharge at a rate equal to that of the source node in the first region. Region 3:The transistor is now in the linear region the gate capacitance is distributed equally to both GS C and GD C . and both capacitors will discharge at approximately the same rate.-151510V0.28621510510nsV I A t C μ-∆===∆⨯⨯+⨯The graph is shown below.00.511.522.533.5024681012Time (ns)V o l t a g e (V )P3.3. The gate and drain are connected together so that DS GS V V = which will cause thetransistor to remain in saturation. This is a dc measurement so capacitances are not required. Connect the bulk to ground and run SPICE. P3.4. Run SPICE. P3.5. Run SPICE. P3.6. Run SPICE. P3.7. Run SPICE.P3.8. First, let’s look at the various parameters and identify how they affect V T .∙ L – Shorter lengths result in a lower threshold voltage due to DIBL. ∙ W – Narrow width can increase the threshold voltage.∙ V SB – Larger source-bulk voltages (in magnitude) result in a higher threshold voltage. ∙ V DS –Larger drain-source voltages (in magnitude) result in a lower threshold voltage due to DIBL. The transistor with the lowest threshold voltage has the shortest channel, larger width, smallest source-bulk voltage and largest drain-source voltage. This would be the first transistor listed.The transistor with the highest threshold voltage has the longest channel, smallest width,largest source-bulk voltage and smallest drain-source voltage. This would be the last transistor listed. P3.9. Run SPICE.P3.10. Run SPICE. The mobility degradation at high temperatures reduces I on and the increasemobile carriers at high temperatures increase I off . P3.11. The issues that prompted the switch from Al to Cu are resistance and electromigration.Copper wires have lower resistances and are less susceptible to electromigration problems. Copper on the other hand, reacts with the oxygen in SiO 2 and requires cladding around the wires to prevent this reaction.For low-k dielectrics, the target value future technologies is 2.High-k dielectrics are being developed as the gate-insulator material of MOSFET’s. This is because the current insulator material, SiO 2, can not be scaled any longer due to tunneling effects.P3.12. Self-aligned poly gates are fabricated by depositing oxide and poly before the source anddrain regions are implanted. Self-aligned silicides (salicides) are deposited on top of the source and drain regions using the spacers on the sides of the poly gate. P3.13. To compute the length, simply use the wire resistance equation and solve for L .LR TWRTWL ρρ==First convert the units of ρ to terms of μm. Aluminum:2.7μΩρ=cm 6Ω10μΩ⨯610μm100cm ⨯()()()0.027Ωμm1000.812963μm 2.96mm0.027RTWL ρ=====Copper:1.7μΩρ=cm 6Ω10μΩ⨯610μm100cm ⨯()()()0.017Ωμm1000.814706μm 4.71mm0.017RTWL ρ=====P3.14. Generally, the capacitance equation in terms of permittivity constants and spacing is:k C WL tε=a. 4k = ()()()()230048.8510 3.541100SiO k k C WL TL t S S Sεε-====b. 2k = ()()()()30028.8510 1.771100k k C WL TL t S SSεε-====The plots are shown below.Capacitance vs. Spacing01234567800.511.522.533.544.555.5Spacing (um)C a p a c i t a n c e (f F)。

广州中医药大学《数字电路》考试试卷A.

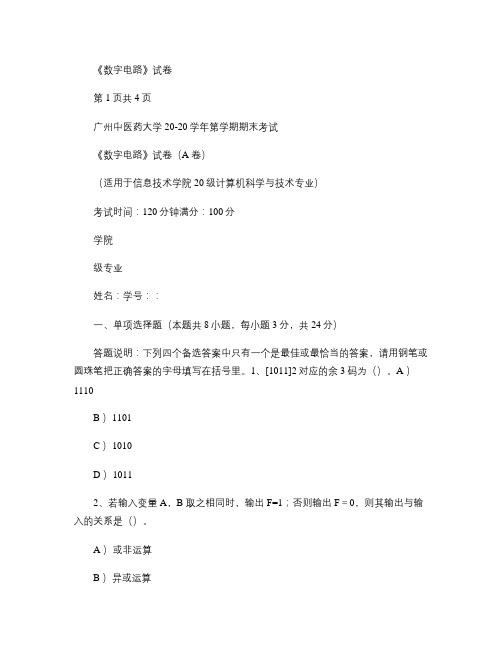

《数字电路》试卷第1页共4页广州中医药大学20-20学年第学期期末考试《数字电路》试卷(A 卷)(适用于信息技术学院20级计算机科学与技术专业)考试时间:120分钟满分:100分学院级专业姓名:学号::一、单项选择题(本题共8小题,每小题3分,共24分)答题说明:下列四个备选答案中只有一个是最佳或最恰当的答案,请用钢笔或圆珠笔把正确答案的字母填写在括号里。

1、[1011]2对应的余3码为()。

A )1110B )1101C )1010D )10112、若输入变量A,B 取之相同时,输出F=1;否则输出F=0,则其输出与输入的关系是()。

A )或非运算B )异或运算C )同或运算D )与运算3、下列各进制数中,值最小的是()。

A )[00110101]2B )[3A]16C )[56]10D )[01010111]8421BCD 4、电路如图所示,不能实现n 1n Q Q =+的电路是()。

5、能够实现线与功能的是()。

A )TTL 与非门B )三态逻辑门C )集电极开路门D )CMOS 逻辑门6、下列所示TTL 门电路输出与输入之间逻辑关系正确的是()7、[755]10对应的8421BCD 码为()。

A )(111010*********BCDB )(0111010101018421BCD题型一二三四总分得分评卷人1CPCPQ Q QAB1K1J1K1J 1.1D 1DCPCPQQ C D《数字电路》试卷第2页共4页C )(011101011018421BCD D )(0011110101018421BCD 二、填空题(本题共10题,每小题3分,共30分)1、只考虑本位两个二进制数相加,而不考虑来自低位进位数相加的运算电路称为。

2、在逻辑函数中,如果一个与项包含该逻辑函数的全部变量,且每个变量或以或以只出现一次,则该与项称为最小项。

3、组合逻辑电路功能上的特点是:在任一时刻的输出状态只取决于的输入状态,与电路的原来状态没有关系。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

广东工业大学考试2010级

<<数字集成电路分析与设计>>考试

一、计算题(16分)

在一个PMOS 硅栅晶体管中,阱掺杂为3

17cm 107.3−×=D N 。

栅掺杂为320cm 103−×=A N ,栅氧化层厚度为nm ox 2.2t =,二氧化硅表面单位面积正电荷为211cm 106−×个。

(a )计算无注入零偏置下(0=SB V )器件的阈值电压。

(10分)

(b )若希望调节PMOS 的阈值电压至-0.4V ,计算其阈值注入量。

(3分)(c )为什么PMOS 采用P+多晶硅而不采用N+多晶硅?(3分)

二、计算题(20分)

在CMOS 反相器中:

(a )与其它反相器相比,CMOS 反相器具有哪些优缺点。

(4分)

(b )画出其电压传输曲线,并且分析随着输入电压in V 改变,PMOS 和NMOS 工作区

间的转换过程,标注重要临界点。

(8分)

(c )推导IL V 的表达式。

(8分)

试根据版图画出电路原理图,并写出逻辑表达式。

四、计算题(20分)

采用0.13um工艺,用与非门设计一个SR锁存器的晶体管电路(拓扑结构图)及器件尺寸(逻辑如图2所示),使其从S到Q非和R到Q的延时为200ps,假设Q和Q非驱动的总负载为200fF.

图2

在图3中,计算其最佳路径延时和晶体管尺寸(所有器件都是标准CMOS 门且所有晶体管都有最小长度L=0.1um )。

使用0.13um 工艺参数,inv C 为最小尺寸反相器的输入电容。

图3

六、画图与读图题(14分)

根据逻辑表达式,画出CMOS 门电路的原理图,并设计其沟道宽度使其与反相器延时相匹配(假设反相器中NMOS 沟道宽度为W )

(a )F E D C B A F ⋅+⋅⋅+=)(。

(7分)

(b )根据图4,写出输入与输出之间的逻辑表达式。

(7分)

图4。