1数电新 5章 大规模数字集成电路11 (2)共84页文档

第五章数字集成电路(基础)

(基础)

上海大学 自动化系 林小玲

§5.1 数字电路的基础知识

数字信号与模拟信号 数制

码制

逻辑代收基础

§5.1.1 数字信号与模拟信号

模拟电路

电子电路

信号与时间的关系连续

数字电路

电 子 技 术

信号与时间的关系离散

电子器件

分立元件电路 电子电路 集成电路 电子系统

end

§5.1.3

二进制码

码制:用某组代码形象地表示某数的实际值或者表 示某个文字符号。

1. 二 - 十进制码 (BCD码)( Binary Coded Decimal codes) 用四位二进制代码来表示一位十进制数码,这样的代码称为二-

十进制码,或BCD码.

四位二进制有16种不同的组合,可以在这16种代码中任选10种表 示十进制数的10个不同符号,选择方法很多.选择方法不同,就能得

0 1 2 3 4 5 6 7 8 9 A B C D E F

②二进制数转换为八进制数

方法:

以小数点为基准,分别向左和向右每3位划为一组,

不足3位补0(整数部分补在前面,小数部分补 在后面),每一组用其对应的八进制数代替。

例:

(11110. 01)B = (011’110. 010)B = (3 6. 2)O 7 5 . 1)O

加,即可得到所代表的十进制数

常用BCD码

十进制数 0 8421码 0000 5421码 0000 2421码 0000 余3码 0011

1

2 3 4 5 6

0001

0010 0011 0100 0101 0110

0001

0010 0011 0100 1000 1001

数字集成电路及其应用讲稿

•# PPT文档演模板

•图1 NPN PNP三极管反相器电路 Vin无输入电位Q1截止。Vin高电 平时Q1导通,Q2基极得高电位, Q2截止。

数字集成电路及其应用讲稿

PPT文档演模板

•图2 两只NPN三极管反相器电 路 vin无输入电位Q1截止,Q2导 通。Vin接入高电平Q1导通,促 使Q2基极电位下级,Q2截止。

n 高低电平的划分:对于TTL来说高电平是 :2.4V-5.0V,低电平是:0.0V-0.8V;对于 CMOS来说高电平是:3-5.0v 低电平是:0.02v

PPT文档演模板

数字集成电路及其应用讲稿

n 在右图所示用电阻和开关 构成的电路中,开关闭合时, 开关所呈现的电阻为0,使得 开关两端的电压也就是输出 电压为0,输出低电平。反之, 若开关断开,因为电阻R上没 有电流流过,R上的电压等于 电源电压,即输出高电平。

各1只,3v(5)v电源1只,多用电表1只。 n 试验过程: 在电路试验板上按左图搭接电路,并在下列各空格处填入试

验结果。 (1)将输入端接地,用多用电表测量电阻Rc两端的电压

Ur=大”0或V者,“此很时小晶”体)三,极三管极集管电处极于的电•截流止(Ice填= “•很导小(通填”“或很“

•3 截V,属止于”)•高状(态填;“三高极”管或集“电低极”c)与电发平射。极e之间的电压Uce= (2)将输入端接3V电压,用多用电表测量电阻Rc两端的电

数字集成电路及其应用 讲稿

PPT文档演模板

2020/11/21

数字集成电路及其应用讲稿

课标内容

•1、了解晶体三极管的开关特性 •及其在数字电路中的应用

•2、知道常见的数字集成电路的类型,并能 •用数字集成电路安装简单的实用电路装置

数字集成电路设计 pdf

数字集成电路设计一、引言数字集成电路设计是一个广泛且深入的领域,它涉及到多种基本元素和复杂系统的设计。

本文将深入探讨数字集成电路设计的主要方面,包括逻辑门设计、触发器设计、寄存器设计、计数器设计、移位器设计、比较器设计、译码器设计、编码器设计、存储器设计和数字系统集成。

二、逻辑门设计逻辑门是数字电路的基本组成单元,用于实现逻辑运算。

常见的逻辑门包括与门、或门、非门、与非门和或非门等。

在设计逻辑门时,需要考虑门的输入和输出电压阈值,以确保其正常工作和避免误操作。

三、触发器设计触发器是数字电路中用于存储二进制数的元件。

它有两个稳定状态,可以存储一位二进制数。

常见的触发器包括RS触发器、D触发器和JK触发器等。

在设计触发器时,需要考虑其工作原理和特性,以确保其正常工作和实现预期的功能。

四、寄存器设计寄存器是数字电路中用于存储多位二进制数的元件。

它由多个触发器组成,可以存储一组二进制数。

常见的寄存器包括移位寄存器和同步寄存器等。

在设计寄存器时,需要考虑其结构和时序特性,以确保其正常工作和实现预期的功能。

五、计数器设计计数器是数字电路中用于对事件进行计数的元件。

它可以对输入信号的脉冲个数进行计数,并输出计数值。

常见的计数器包括二进制计数器和十进制计数器等。

在设计计数器时,需要考虑其工作原理和特性,以确保其正常工作和实现预期的功能。

六、移位器设计移位器是数字电路中用于对二进制数进行移位的元件。

它可以对输入信号进行位移操作,并输出移位后的结果。

常见的移位器包括循环移位器和算术移位器等。

在设计移位器时,需要考虑其工作原理和特性,以确保其正常工作和实现预期的功能。

七、比较器设计比较器是数字电路中用于比较两个二进制数的元件。

它可以比较两个数的值,并输出比较结果。

常见的比较器包括并行比较器和串行比较器等。

在设计比较器时,需要考虑其工作原理和特性,以确保其正常工作和实现预期的功能。

八、译码器设计译码器是数字电路中用于将二进制数转换为另一种形式的元件。

数字集成电路简介.ppt

v(t)

– 耦合电容 - 其中一条导线上电压的 变化会影响相邻导线上的信号

i(t)

– 耦合电感 - 其中一条导线上电流的 变化会影响相邻导线上的信号

VD

• 电源线和地线上的噪声

D

– 会影响该门的信号电平

说明:噪声是数字电路工程中一个主要关注的问题。如何克服所有这 些干扰是高性能数字电路设计所面临的主要挑战之一。

2019年12月31日12时10分

例题1.2 电源分布网络对系统设计的挑战

功能块A

功能块B

功能块A

功能块B

A. 布线通过功能块

引论. 26

B. 布线绕过功能块

2019年12月31日12时10分

1.3 数字设计的质量评价

• 集成电路的成本 • 功能性和稳定性 • 性能 • 功耗和能耗

• 为了保证整个设计层次中定义的一致性,我们采用了从下 而上的设计方法:从定义一个简单反相器基本的质量评定 标准开始,并逐渐将它们扩展到如逻辑门、模块和芯片这 些更为复杂的功能

数字IC(组合/时序) 模拟IC(线性/非线性)

模数混合IC 通用IC、专用IC

2019年12月31日12时10分

划分集成电路规模的标准

类型

SSI MSI LSI VLSI ULSI GSI

数字集成电路

MOS IC

双极 IC

<100

<100

100~1000

100~500

103 ~ 105

500~2000

引论. 14

2019年12月31日12时10分

集成电路的概念

• Integrated Circuit,缩写IC

• 通过一系列特定的加工工艺,将晶体管、二极管等有源 器件、电容和电阻等无源器件,按照一定的电路互连, “集成”在一块半导体单晶片(如硅或砷化镓)上,封 装在一个外壳内,执行特定电路或系统功能

数字集成电路

数字集成电路数字集成电路是将元器件和连线集成于同一半导体芯片上而制成的数字逻辑电路或系统。

依据数字集成电路中包含的门电路或元、器件数量,可将数字集成电路分为小规模集成(SSI)电路、中规模集成MSI 电路、大规模集成(LSI)电路、超大规模集成VLSI电路和特大规模集成(ULSI)电路。

目录注意事项一般特性类别说明内部设计逻辑功能型号构成基本介绍注意事项①不允许在超过极限参数的条件下工作。

电路在超过极限参数的条件下工作,就可能工作不正常,且简单引起损坏。

TTL集成电路的电源电压允许变化范围比较窄,一般在4.5~5.5V之间,因此必需使用+5V稳压电源;CM0S集成电路的工作电源电压范围比较宽,有较大的选择余地。

选择电源电压时,除首先考虑到要避开超过极限电源电压外,还要注意到,电源电压的高处与低处会影响电路的工作频率等性能。

电源电压低,电路工作频率会下降或加添传输延迟时间。

例如CM0S触发器,当电源电压由+15V下降到十3V时,其工作频率将从10MHz下降到几十千赫。

②电源电压的极性千万不能接反,电源正负极颠倒、接错,会由于过大电流而造成器件损坏。

③CM0S电路要求输人信号的幅度不能超过VDD~VSS,即充足VSS=V1=VDD。

当CM0S电路输入端施加的电压过高(大于电源电压)或过低(小于0V),或者电源电压蓦地变化时,电路电流可能会快速增大,烧坏器件,这种现象称为可控硅效应。

防备可控硅效应的措施重要有:·输入端信号幅度不能大于VDD和小于0V;·除去电源上的干扰;·在条件允许的情况下,尽可能降低电源电压,假如电路工作频率比较低,用+5V电源供电;·对使用的电源加限流措施,使电源电流被限制在30mA以内。

④对多余输人端的处理。

对于CM0S电路,多余的输人端不能悬空,否则,静电感应产生的高压简单引起器件损坏,这些多余的输人端应当接yDD或yss,或与其他正使用的输人端并联。

数字集成电路

数字集成电路(1)20世纪40年代中期,电子管几乎是各种电子设备惟一的电子器件。

那时的人们无论如何也想象不到60年后,把载重卡车大小的设备缩小到手表大小,一粒钮扣电池能供电一两年,这是人类创造的奇迹,微电子学的产物。

60年后的电子手表又会是什么样子呢?目前,电子器件经历过电子管、晶体管、小、中规模集成电路、大规模集成电路,已进入到第五代电子器件——超大规模集成电路时代。

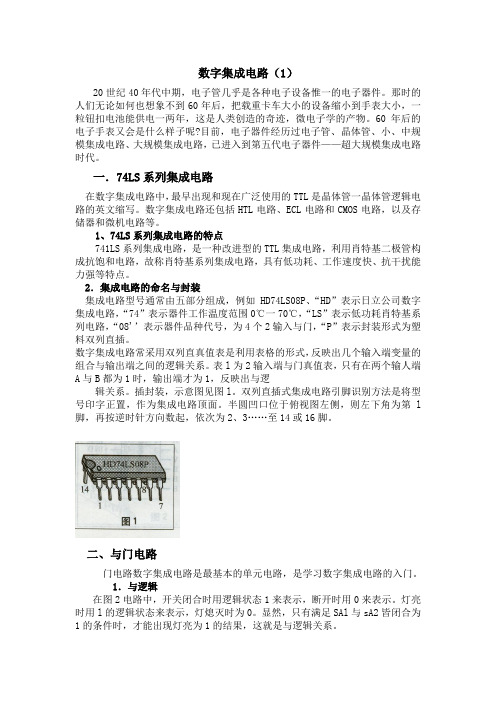

一.74LS系列集成电路在数字集成电路中,最早出现和现在广泛使用的TTL是晶体管一晶体管逻辑电路的英文缩写。

数字集成电路还包括HTL电路、ECL电路和CMOS电路,以及存储器和微机电路等。

1、74LS系列集成电路的特点741LS系列集成电路,是一种改进型的TTL集成电路,利用肖特基二极管构成抗饱和电路,故称肖特基系列集成电路,具有低功耗、工作速度快、抗干扰能力强等特点。

2.集成电路的命名与封装集成电路型号通常由五部分组成,例如HD74LS08P、“HD”表示日立公司数字集成电路,“74”表示器件工作温度范围0℃一70℃,“LS”表示低功耗肖特基系列电路,“08'’表示器件品种代号,为4个2输入与门,“P”表示封装形式为塑料双列直插。

数字集成电路常采用双列直真值表是利用表格的形式,反映出几个输入端变量的组合与输出端之间的逻辑关系。

表l为2输入端与门真值表,只有在两个输人端A与B都为1时,输出端才为1,反映出与逻辑关系。

插封装,示意图见图l。

双列直插式集成电路引脚识别方法是将型号印字正置,作为集成电路顶面。

半圆凹口位于俯视图左侧,则左下角为第l 脚,再按逆时针方向数起,依次为2、3……至14或16脚。

二、与门电路门电路数字集成电路是最基本的单元电路,是学习数字集成电路的入门。

1.与逻辑在图2电路中,开关闭合时用逻辑状态1来表示,断开时用0来表示。

灯亮时用l的逻辑状态来表示,灯熄灭时为0。

显然,只有满足SAl与sA2皆闭合为1的条件时,才能出现灯亮为1的结果,这就是与逻辑关系。

数字集成电路中的基本模块 ppt课件

35

Y0

静态CMOS逻辑门实现3-8 译码器

输入 x2 x1 0 0 0 0 1 1 1 1 0 0 1 1 0 0 1 1 输出 Y0 Y1 Y2 Y3 Y4 1 0 0 0 0 0 0 0 0 1 0 0 0 0 0 0 0 0 1 0 0 0 0 0 0 0 0 1 0 0 0 0 0 0 0 0 1 0 0 0

P VDD A A B A P A P B Ci P Ci P A P Ci Setup A P

3

VDD S Sum Generation VDD Co Carry Generation

VDD Ci Ci

ppt课件

3

TG Full Adder

Cin B

A B

A

Sum

Cout

ppt课件

4

第五章 数字集成电路中的基本模块

0 0 0 0 0 0 1 1

0

0 0 1 1 1 1 0 0

ppt课件

0

1 1 0 0 1 1 0 0

1

0 1 0 1 0 1 0 1

30

30

十进制数的BCD编码电路原理图

9 8 7 6 5 4 3 2

Y3

2

2

0

Y2 Y1

0

1

2

0

Y0

ppt课件

31

31

译码器 (Decoder)

将二进制码转换为其他类型代码。

D0

问题: 高扇入

D1 D2 D3

F

S0

S1

ppt课件

24

24

四路数据选择器

2/3

用CMOS静态组合逻辑实现:Building big from small;

数字集成电路

数字集成电路专题研究摘要:现在的电路可以分为两个方向,一个是数字,还有一个是模拟,在此更加偏重对数字方面的研究!全文一共可以分为两部分,一部分是基本的数字电路,还有一部分为较大型的集成电路。

前一部分(基本数字电路)从认识数字电路开始,其间涉及到数字电路的分析方法---函数分析方法;在数字电路中分TTL和COMS两种电路,在此报告中提到了这两种电路的电平比较关系。

因COMS电路功耗低、工作电压范围宽、扇出能力强和售价低等优点,所以着重介绍一下CMOS 电路的常用特性,以及由它构成的一些常见的数字电路!而在后半部方介绍的是集成电路,从集成电路的分类到如何做好集成电路的设计;集成电路的设计分为前端和后端设计前端是指逻辑部分,后端是指物理层的设计.前端是设计内部的逻辑.后端是指假设逻辑设计已经完成,如何做出最后的芯片,涉及到芯片内部如何分区,如何布线,模拟部分,寄生效应等等.而由于专业方向这里又着重去讨论前端设计:系统集成芯片(SoC)的IC设计。

同时收集了一些集成电路的设计工具。

关键字:数字电路函数表示COMS集成电路常见的数字电路集成电路分类IC前端设计工具系统集成芯片SOC IC设计软件VHDL/ Veriolg HDL 正文:一.数字电路简介:在电子设备中,通常把电路分为模拟电路和数字电路两类,前者涉及模拟信号,即连续变化的物理量,例如在24小时内某室内温度的变化量;后者涉及数字信号,即断续变化的物理量,开关K 快速通、断时,在电阻R 上就产生一连串的脉冲(电压),这就是数字信号。

人们把用来传输、控制或变换数字信号的电子电路称为数字电路。

数字电路工作时通常只有两种状态:高电位(又称高电平)或低电位(又称低电平)。

通常把高电位用代码“1 ”表示,称为逻辑“1 ”;低电位用代码“0 ”表示,称为逻辑“0 ”(按正逻辑定义的)。

注意:有关产品手册中常用“H ”代表“1 ”、“L ”代表“0 ”。

实际的数字电路中,到底要求多高或多低的电位才能表示“1 ”或“0 ”,这要由具体的数字电路来定。

电子技术 大规模数字集成电路

输出及控制电路

数据输出 ROM存 储 器 结 构 图

存储容量:存储单元的总数。

1k=210=1024个存储单元

1.

固定ROM

W0

1

1 0 1 0 A0

地 址 译 码

W1 W2 W3

0 1

0 1 0 1

输 出 缓 冲 器

a f e d g b c

数码管驱动表

显示数 0 1 2 3 4 5 6 7 8 9 地址码 A3 0 0 0 0 0 0 0 0 1 1 A2 0 0 0 0 1 1 1 1 0 0 A1 0 0 1 1 0 0 1 1 0 0 A0 0 1 0 1 0 1 0 0 0 1 g 0 0 1 1 1 1 1 0 1 1 f 1 0 0 0 1 1 1 0 1 1 数码 e 1 0 1 0 0 0 1 0 1 0 d 1 0 1 1 0 1 1 0 1 1 c 1 1 0 1 1 1 1 1 1 1 b 1 1 1 1 1 1 0 1 1 1 a 1 0 1 1 0 1 1 1 1 1

CS A0

A9

存储器的位扩展结构图

② 字扩展

I/O

I/O

1k× (I) 1位 R / W A0 A9 CS

R/W

√

I/O

1k× (II) 1位 R / W A0 A9 CS

√

I/O

1k× (Ⅲ ) 1位 R / W A0 A9 CS

√

I/O

1k× (Ⅳ ) 1位 A0 A9 CS R/W

√

A0 A9

Si Ai Bi Ci 1 A i Bi Ci 1 A i Bi i 1 A i BiCi1 m1 m 2 m 4 m 7 C Ci Ai Bi Ci 1 Ai Bi Ci 1 Ai Bi Ci 1 Ai Bi Ci 1 m3 m5 m6 m7

数字集成电路详解

Y AB

六反相器

1A 1 1Y 2 2A 3 2Y 4 3A 5 3Y 6 GND 7

04

14 VCC

1004 13 6A

05(OC) 12 6Y

1005 (OC) 11 5A

06 14*

10 5Y

16

9 4A

19

8 4Y

1A 1 1Y 2 2A 3 2Y 4 3A 5 3Y 6 VSS 7

14 VCC 13 2D 12 2C

21 11 NC

10 2B 9 2A 8 2Y

1Y 1 1A 2 1B 3 1C 4 1D 5 NC 6 VSS 7

4082

14 VDD 13 2Y 12 2D 11 2C 10 2B 9 2A 8 NC

Y ABCD

六2输入与门

1A 1 1B 2 1Y 3 2A 4 2B 5 2Y 6 3A 7 3B 8 3Y 9 GND 10

品种代号 00 1000 4011 37 01 03 1003 26 38 39 132 4093 7003

40107 8003 10 1010 4023 12 20 40 4012 22 13 18 1020 618

与非门和反相器 2

类别

品种代号

六2输入与非门

804

六反相器 六反相器(OC) 六施密特触发输入反相器

1Y 1 1A 2 1B 3 2Y 4 2A 5 2B 6 GND 7

39 (OC)

14 VCC

1Y 1

13 4Y

1A 2

12 4B

1B 3

11 4A

2Y 4

10 3Y

2A 5

9 3B

2B 6

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

基本逻辑单元块的 规模大小(或粒度 的粗细)对整个高 密度PLD器件的结构 有很大的影响。

ALTERA公司逻辑元素LE XILINX公司可配置逻辑块CLB

规模大,设计方便, 但器件资源利用率不 易控制,利用率通常 较低

规模小,设计灵活性 大,资源利用率高, 但设计更加复杂

集成电子技术基础教程

可编程互连资源PI

VDD

D7~D0

+5V

输出

+5V

高阻

+5V

高阻

+5V

写入

+5V

读出

+5V

高阻

集成电子技术基础教程

用EPROM2716将四位二进制码转换为格雷码

把四位二进制码作2716的低四位地址输入,同时将四位格雷码作为 对应地址的内容写入到2716中,这样便可实现二者之间的转换关系

¶þ ½ø ÖÆ Âë

B3 B2 B1 B0 0000 0001 0010 0011 0100 0101 0110 0111 1000 1001 1010 1011 1100 1101 1110 1111

B0 B1 B2 B3

3

A5

2

A6

2 31

A7 A8

22 19

AA 19 0

20 18

EO/EP

21

VP P

+5V

集成电子技术基础教程

2,设计一个能显示“日”字的字符发生 器,“日”字的8×8点阵式显示板

集成电子技术基础教程

2.5.3高密度可编程逻辑器件简介

专用集成电路ASIC

标准单元(Standard Cell)型 宏单元(Macro Cell)型 门阵列(Gate Array)型 可编程逻辑器件PLD

CS0

A10

2/4

CS1

A11

1024*4(1)

1024*4(2)

ÁÐ Ñ¡ Ïß Y

1024*4(3)

1024*4(1) CS2

1024*4(2)

ÁÐ Ñ¡ Ïß Y

CS3

1024*4(3)

集成电子技术基础教程

2.5.2只读存储器ROM

只读存储器的一般结构

半导体存储器ROM中 的信息不能轻易地更改。

集成电子技术基础教程

I/O单元

引脚数:44~560 专用输入引脚--电源,编程引脚,时钟和专用信号

输入/输出寄存器 三态门,多路选择器, 输出摆率控制电路,边界扫描电路

集成电子技术基础教程

基本逻辑单元块BLB

器件内部实现逻辑功能最小单位 LATTICE公司通用逻辑阵列块GLB

PI的功能主要是将各基本逻辑单元块描述的局 部逻辑功能相互连在一起,构成一个完整的数 字系统,并将输入/输出连接至具体的I/O单元。 从表面上看,PI只是起一个连线作用,实际上 既要保证将各种设计的不同基本逻辑单元块连 接在一起,同时又要减少连线的延迟,PI的设 计十分复杂。PI资源的设计好坏直接影响PLD器 件的设计效率和PLD器件的工作稳定性

集成电子技术基础教程

ispLSI1016在系统可编程逻辑器件的结构

集成电子技术基础教程

ispLSI1016内部的信号流

I/O引脚来的输入信号经过输入总线后进入全布线区,然 后由GRP统一调度,将信号分配给具体的通用逻辑块GLB;

输入引脚来的输入信号不GRP,直接进入各自所属宏 块的GLB之中。

译

码

A0

器

…… …… ……

…… …… I/O及读写控制

数据输入/输出 片选

I/O控制

存储体

j列 i行

存储单元

存储单元(1位) j列

i行

存储单元(多位,4位)

集成电子技术基础教程

存储体或RAM的容量

存储单元的个数*每个存储单元中数据的位数 例如,一个10位地址的RAM,共有210个存储单元,若 每个存储单元存放一位二进制信息,则该RAM的容量就 是210(字)×1(位)=1024字位,通常称1K字位。

D7 D6 D5 D4

D3 D2 D1 D0

A9~A0 /CS /WE

RAM 2114

RAM 2114

集成电子技术基础教程

SRAM容量的扩展 ---字位扩展

例,用RAM2114实现容量为4096×8字位容量 (≈ 32 k字位)的RAM

WE

D3~D0 D7~D4

A9~A0

1024*4(0)

1024*4(0)

I/O缓冲

I/O缓冲起数据锁存作用,一般采用三态输出结构。 因此,它可与外面的数据总线相连接,方便实现信息 交换和传递

集成电子技术基础教程

RAM的读写过程 (时序)

访问某地址单元的地址码有效 片选有效 读/写操作有效

集成电子技术基础教程

RAM中的存储单元

按照数据存取的方式不同,RAM存储单元分为两种: 静态存储单元— 静态 RAM(SRAM) 动态存储单元— 动态 RAM(DRAM)

集成电子技术基础教程

只读存储器ROM的种类

根据不同的半导体制造工艺,或阵列的编程方式有 多种。存储器ROM 通常按其编程工艺 划分 掩膜型只读存储器 一次编程(改写)的只读存储器PROM EPROM(紫外线擦除式可编程只读存储器UVEPROM) E2PROM(电擦除式可编程只读存储器EEPROM) 快闪存储器(FLASH Memory)

集成电子技术基础教程

随机存取存储器(Random Access Memory)

加电写入的新信息取代原信息 电路失电,信息全无 恢复供电,恢复信息是随机的

集成电子技术基础教程

随机存取存储器的基本结构

……

…… …… ……

……

Bn-1 Bn-2 …… B0

列地址译码器

An-1

行

An-2

地 址

集成电子技术基础教程

EPROM(紫外线擦除式可编程只读存储器UVEPROM)

可多次编程,编程次数达100百次 每次编程前,需先用UV擦除,时间约20分钟 编程后需防空气中UV,数据可保存20年以上

集成电子技术基础教程

E2PROM(电擦除式可编程只读存储器EEPROM)

EEPROM的擦除只需电信号(高压编程电压和高压脉冲),且 擦除速度快。 EEPROM可以单字节擦除或改写,而EPROM只能整片擦除。 有些EEPROM可5V编程 EEPROM既具有ROM器件的非易失性优点,又具备类似 RAM器件的可读写功能(只不过写入速度相对较慢)

EPROM2716

EPROM2716,有11根地址线A0~A10,8位数据输出D0~D7。因 此,其存储容量为211×8=2018×8字位,简称2K×8字位容量

工作状态

/CE

/OE

0

0

未选中

1

等待

1

编程写

50MS脉

1

冲

编程禁止

0

0

编程禁止

0

1

VPP +5V +5V +5V +25V +25V +25V

Êý ¾Ý

D7~D0 00H 01H 03H 02H 06H 07H 05H 04H 0CH 0DH 0FH 0EH 0AH 0BH 09H 08H

8

A0

7

A1

6

A2

5

A3

D0 D1 D2 D3 D4 D5 D6 D7

19 0 11 13 14 15 16 17

4

A4

G0 G1G2G3 EPROM2716

4×4字位ROM器件的简化逻辑图表示

ROM的结构和可编程 “与阵列”和可编程“或 阵列”的结构相类似。

与阵列由译码器构成,N 位地址ROM的与阵列共有2N 个与项(在这里称为 “字”),每个与项对应地 址输入的一个最小项,且不 可编程。 存储矩阵部分构成了可编程 或阵列,每个或门的输出在此 称为“位”。ROM的或阵列在 器件制造时就进行了固定的编 程

集成电子技术基础教程

高密度可编程逻辑器件的分类

高PROM工艺 E2PROM或Fresh Memory工艺 SRAM编程工艺

编程方式分

ISP方式,ICR方式 硬件编程器编程方式

器件结构分 常见名称

CPLD器件

FPGA器件 EPLD,HDPLD,ispPLD,CPLD ,FPGA

集成电子技术基础教程

SRAM 2114

RAM2114 (a)

1 08

CS

WE

µØ Ö· ÓРЧ ÓРЧ ÓРЧ

CS WE

1

0

1

0

0

(b)

I/O3~I/O0

¸ß × è ̬ Êä ³ö Êä Èë

集成电子技术基础教程

SRAM容量的扩展 ---位数扩展

例,用RAM2114实现容量为1024×8字位容量 (≈8K字位)的RAM

一经写入,只能读出。 即使掉电,原存储内容 仍然不变。

一旦恢复供电,信息 能完全复原

集成电子技术基础教程

例,4×4字位容量的只读存储器

A1 A0 W D3 D2 D1 D0

0

0 W0 0 1 1 1

0

1 W1 1 0 1 1

1

0 W2 1 1 0 0

1

1 W3 0 0 1 1

3

集成电子技术基础教程

集成电子技术基础教程

快闪存储器(FLASH Memory)

每个存储单元只需单个MOS管,因此其结构比EEPROM 更加简单,存储容量可以做得更大 不能象EEPROM那样实现单字节擦除或改写,一般只能分页 擦除或改写 根据器件容量大小,一页大小为128、256、512、64K字节不等