并行接口电路

简单的并行接口电路PPT课件

12

74LS373是十分常用的锁存器电路,主要用来在总线 传输电路中锁存地址信息或数据信息,并实现总线信 号的缓冲与驱动。

与 74LS373 锁 存 器 功 能 类 似 的 芯 片 还 有 Intel 8282/8283等 。

.

13

14.2.2 缓冲器74LS244

74LS244 是一种三态输出的 8 位缓冲器/驱动器电路, 其逻辑电路图和引脚图如图14.2所示。

(b)引脚图

7

由图14.1可见,该电路由8个D锁存器构成(图中仅画一 个,其余与此相同),有8个输入端1D~8D,8个输出 端1Q~8Q,两个控制端:

选通端G和输出允许端OE。

当选通端G为高电平时,则D锁存器的输出跟随相应输 入数据端的逻辑电平;

当G变为低电平时,则D锁存器中的当前内容被锁存。

只有当输出允许信号OE有效(为低电平) 时,锁存器中 的信息才出现在输出端1Q~8Q上;如果OE为高电平,

则输出处于高阻态。

.

8

74LS373的真值表如表14-1所示。

该表中H为高电平,L为低电平,Q0为原状态, Z为高阻态,X表示任意值(为H或L均可)。

.

9

表14.1 74LS373真值表

当选通端G为高电平,同时输出允许端OE为低电平时, 则输出Q=输入D(输出Q跟随输入D);

当选通端G为低电平,而输出允许端OE也为低电平时, 则输出Q=Q0(Q0为原状态,即选通端G由高电平变为低 电平时输出端Q的状态);

当输出允许端OE为高电平时,无论选通端G为何值,输 出端Q总为高阻态。

.

锁存器74LS373; 缓冲器74LS244; 数据总线收发器74LS245。

.

5

实验三、8255A并行接口实验

实验结论

通过本次实验,我们验证了8255A并行接口芯片的基本功能和工作原理。

实验结果证明了8255A芯片可以实现并行数据传输,并且可以通过设置不 同的端口模式来实现不同的输入输出功能。

在实际应用中,8255A芯片可以作为并行数据传输的重要接口之一,广泛 应用于各种数字电路和微机控制系统中。

05

实验总结与展望

等。

学习如何设置8255a并行接口芯 片的控制字,掌握其工作模式和

特点。

理解8255a并行接口芯片在计算 机中的重要性和作用,以及与其

他接口芯片的区别和联系。

掌握8255a并行接口芯片的工作原理

了解8255a并行接口芯片的基本 结构和工作原理,包括输入/输 出端口、控制寄存器和数据总线

等。

学习如何设置8255a并行接口芯 片的控制字,掌握其工作模式和

缺乏实验指导

实验过程中,我们遇到了一些难 以解决的问题,如果能有更多的 实验指导资料或教师指导,将有 助于我们更好地有限,我们未能充 分探索8255a并行接口的更多功 能和应用场景,建议增加实验时 间,以便我们有更多的机会深入 了解该芯片。

实验不足与改进建议

实验难度不够

学习如何使用8255a并行接口芯片进行硬件控制

学习如何使用8255a并行接口 芯片进行输入/输出操作,包括 读取和写入数据。

掌握如何通过8255a并行接口 芯片控制外部硬件设备,如 LED灯、继电器等。

了解如何将8255a并行接口芯 片与其他芯片连接,实现硬件 的扩展和控制。

了解并行接口在计算机中的作用和重要性

实验三

将端口B和端口C设置为输入,端口A设置为输出。 当在端口B和端口C上施加不同的电平时,端口A 的输出与端口C的输入相同。

第9章_并行接口电路

3) 可编程功能

有些接口具有可编程特性,可以通过指令设定接口的工作 方式,工作参数,以满足不同外设的要求。

4) 数据转换功能

当外设提供的数据形式不是CPU能直接接受的形式时,则 通过接口转换成CPU可接受的形式。如A/D,串/并转换等, 反之也一样。

5) 联络功能

当CPU要访问外设时,首先要查询外设状态,能否接受访 问,接口应将外设状态准备好,供CPU查询;或向CPU发特 定的信号通知外设已准备好。

1 0

0 0 1 1

0 1 0 1

A口 B口 C口 控制口

说明: 1) A口有3种工作方式 方式0:基本I/O方式; 方式1:单向选通I/O方式,输入或输出只能选一种; 方式2:双向选通I/O方式,一次设置后通道既可以做输入 又可以做输出。 2) 端口B有两种工作方式 即方式0与方式1 3) A口和B口工作在方式0时,C口也可同时工作在方式0, 且C口高半字节和低半字节可以分别独立工作。

1 00 方式0 1输入 01 方式1 0输出 1x方式2 1 输入 0 输出 0 方式0 1 输入 1 方式1 0 输出 1 输入 0 输出

一系统采用8255A作I/O接口,其控制口的地址为8BH,将 端口A设置为方式0输入,端口B设置为方式1输出,则A口 88H 89H 94H 的地址为_____ ,B口地址为_____,控制字为_____。

译 Y1 C码 B器 Y0 A

G

CS

D7~D0

A1 A0J1 D7 D0

CS

J1,J2地址

A9 A8 A7 A6 A5 A4 A3 A2 A1 A0 J1 0 1 × × 0 0 1 0 0 0 J2 0 1 × × 0 0 0 0 0 0

A1 A0J1 D7 D0

并行接口P0~P3

K

30P

XTAL2 GND

第5章 并行接口P0~P3和单片机的中断系统

编程如下:

CLR P1.0 AGA:SETB P1.1 JB P1.1,LIG SETB P1.0 SJMP AGA LIG: CLR P1.0 SJMP AGA

;使发光二极管灭 ;先对P1口写入“1” ;开关开,转LIG ;开关合上,二极管亮

LED数码管的g~a七个发光二极管因加正电压而发亮, 因加零电压而不能发亮,不同亮暗的组合就能形成不同的字 形,这种组合称之为字形码,显然共阳极和共阴极的字形码 是不同的 ,其字形码见下表。LED数码管每段需10~20ma 的驱动电流,可用TTL或CMOS器件驱动。 字形码的控制输出可采用硬件译码方式,如采用BCD 7段译码/驱动器74LS48、74LS49、CD4511(共阴极)或 74LS46、74LS47、CD4513

P1.7

SCቤተ መጻሕፍቲ ባይዱ引脚,在系统编程时钟输入

第5章 并行接口P0~P3和单片机的中断系统

3.P2口 内部上拉电阻的8位准双向并行I/O口,P2口的位结构比P1 多了一个转换控制部分,当P2口作通用I/O口时,多路开关 MUX倒向左; 读锁存器

1 内部总线 写锁存器 P2.x 锁存器 CL 2 读引脚 D Q

/数据复用总线(用于口扩展) 两个输入缓冲器(BUF1和BUF2) 读锁存器

P0R1

地址/数据

BUF1

AD0

控制 Vcc

b c

内部总线

D0

D C

a

T1

写锁存器

P0W

锁存器

Q

Q

P00

3、P0W为端口输出写信号,用于 推拉式I/O驱动器 锁存输出状态 多路开关 4、P0R1为读锁存器信号,执行 功能:用于控制选通I/O方式 “ANL P0,#0FH”时该信号有效 A 还是地址/数据输出方式 5、P0R2为读引脚信号,执行 2) “MOV A,P0”时该信号有效 方式控制:由内部控制信号

第5章 并行接口P0~P3

大多数口线都有双重功能,具体介绍如下:

PO口—1.作为输入/输出口。

2.作为地址/数据总线 ,接外围芯片时PO口分时输出低 8 位地址与数据信号。

P1口—作为输入/输出口。

P1.0 T2引脚,定时/计数器2外部计数脉冲输入 P1.1 T2EX引脚,定时/计数器2触发和方向控制 P1.5 MOSI引脚,在系统编程数据输入 P1.6 MISO引脚,在系统编程数据输出 P1.7 SCK引脚,在系统编程时钟输入

这是为了避免错读引脚的电平信号,例如用一根口线去 驱动一个晶体管基极,当向口线写“1”,晶体管导通,导通 的PN结会把引脚的电平拉低,如读引脚数据,则会读为0 , 而实际上原口线的数据为1。因而采用读锁存器Q的值而避免 了错读。究竟是读引脚还是读 锁存器,CPU内部会自行判断 是发读引脚脉冲还是读锁存器脉冲,读者不必在意。

归纳四个并行口使用的注意事项如下:

1.如果单片机内部有程序存贮器,不需要扩展外部存贮器和 I/O接口,单片机的四个口均可作I/O口使用。

2.四个口在作输入口使用时,均应先对其写“1”,以避免误 读。

3.P0口作I/O口使用时应外接10K的上拉电阻,其它口则可不必。 4.P2可某几根线作地址使用时,剩下的线不能作I/O口线使用。 5.P3口的某些口线作第二功能时,剩下的口线可以单独作I/O

内容提要

★单片机的并行接口P0~P3

★ PO~P3端口的功能和内部结构 ★ PO~P3端口的编程 ★ 用并行口设计LED数码显示和键盘电路 ★ 并行接口小结

★MCS-51单片机的中断系统

★ 中断的基本概念 ★ 中断的系统结构 ★ 中断的响应过程 ★ 中断的的应用编程

★小结

I/0接口

计算机的并行接口大全

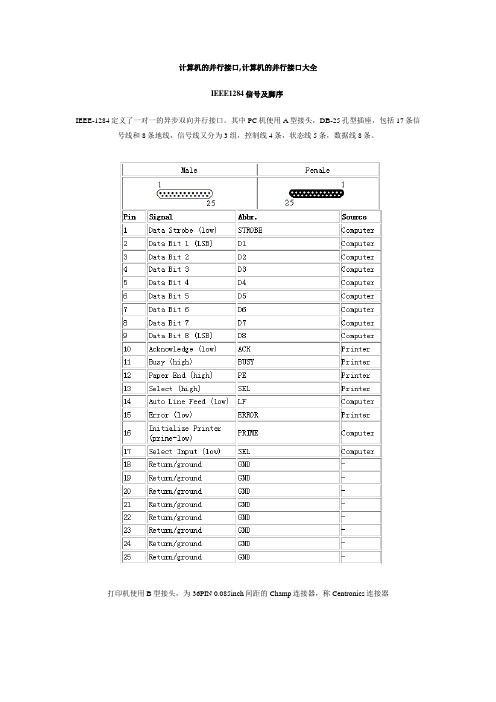

计算机的并行接口,计算机的并行接口大全IEEE1284信号及脚序IEEE-1284定义了一对一的异步双向并行接口。

其中PC机使用A型接头,DB-25孔型插座,包括17条信号线和8条地线,信号线又分为3组,控制线4条,状态线5条,数据线8条。

打印机使用B型接头,为36PIN 0.085inch间距的Champ连接器,称Centronics连接器36PIN Centronics连接器的各脚信号的含义C型:新的Mini-Centronics 36PIN连接器,0.050inch间距,既可用于主机,也可用于外设D型25针和36针Centronics的针脚定义对照:A型、B型、C型连接器的针脚定义对照:4. IEEE1284接口的对接:PC机DB-25与打印机Centronics 36PIN连接器的信号对应关系:PC机边A型(DB-25)与打印机边B 型(Centronics 36PIN)连接器的对接:PC机边A型(DB-25)与打印机边C 型(Mini-Centronics 36PIN)连接器的对接:PC机边C型(Mini-Centronics 36PIN)与打印机边B 型(Centronics 36PIN)连接器的对接:5. IEEE1284硬件接口IEEE-1284定义了2种级别的接口兼容性,Level I 用于产品不需要高速模式,但需要利用反向通道能力的场合;Level II用于长电缆和高速传输率场合。

并行接口输出的是TTL标准的逻辑电平,输入信号也要符合TTL标准。

这种特性可以使接口容易应用在电子设计中。

大部分的PC并行接口能吸收和输出12mA左右的电流,如应用时小于或大于这个值,应使用缓冲电路。

为了保持与早期的Centronics 接口兼容,使用OC(open collector)驱动器,使用上拉电阻(pull-up resisto r)标准电阻值为2.2k欧或4.7k欧。

控制线与状态线仅要求上拉电阻Rp,数据线和Strobe线还要求串联电阻Rs来匹配线路阻抗,调整串联电阻值使其与驱动器的输出阻抗之和等于45欧到55欧的线路阻抗。

实验二、1简单并行接口

int 21h

mov ah,06 mov dl,0ffh int 21h jnz exit je start exit: mov ah,4ch int 21h code ends end 244程序流程图 ;若无,则转start ;返回DOS ;是否有键按下

八、实验结果

并行输出接口实验结果 并行输入接口实验结果

保存时输入自命名的源程序“XXX.ASM ”

为扩展名)

(“.ASM”

在“Alt+F”中,选择“EXIT ”退出文本编辑环境

3

图1

图2

使用汇编程序MASM.EXE (微软工具),对 源程序进行汇编,生成OBJ文件。 C:\> MASM (进入汇编环境) Source filename [.ASM]: xxx.asm

;返回DOS

code segment assume cs:code

start:

mov dx,2a0h

in al,dx mov dl,al mov ah,02

;从2A0输入一数据

;将所读数据保存在DL中 ;显示ASCII为DL的数据

int 21h

mov dl,0dh int 21h mov dl,0ah ;显示换行符 ;显示回车符

3

使用连接程序LINK.EXE (微软工具),对 OBJ文件进行连接。只有正确的OBJ文件,才能进 行连接操作。将OBJ文件与库函数或其他目标程序

进行连接成可执行的目标程序-EXE文件。

C:\> LINK (进入连接环境) Object Modules [.OBJ]: xxx.obj Run File [XXX.EXE]: List File [NUL.MAP]: Libraries [.LIB]: Warning: No STACK segment (忽略) There was 1 error detected. C:\> XXX.EXE (执行程序)

常用ADDA芯片的使用:并行ADC0809、串行ADC0832、串行PCF8591

⑶ 延时等待方式

工作在延时等待方式时,0809 EOC端可不必与80C51相连 端可不必与80C51相连, 工作在延时等待方式时,0809 EOC端可不必与80C51相连,是根 据时钟频率计算出A/D转换时间,略微延长后直接读A/D转换值。 A/D转换时间 A/D转换值 据时钟频率计算出A/D转换时间,略微延长后直接读A/D转换值。 14】 20中 EOC端开路 fosc=6MHz, 端开路, 【例9-14】 图9-20中,0809 EOC端开路,fosc=6MHz,试用延 时等待方式编制程序, 路模拟信号依次A/D转换一次, A/D转换一次 时等待方式编制程序,对8路模拟信号依次A/D转换一次,并把 结果存入以50H为首址的内RAM 50H为首址的内RAM中 结果存入以50H为首址的内RAM中。 编程如下: 解:编程如下:

ORG LJMP ORG LJMP ORG STAT: MOV MOV SETB SETB SETB MOV MOVX LJMP 0000H STAT 0013H PINT1 0100H R1,#30H R7,#8 IT1 EX1 EA DPTR,#0FEF8H @DPTR,A MAIN ;复位地址 ;转初始化程序 ;中断服务子程序入口地址 中断,转中断服务子程序; ;中断,转中断服务子程序; ;初始化程序首地址 ;置数据区首址 ;置通道数 ;置边沿触发方式 ;开中 ;CPU开中 ;CPU开中 0809通道 通道0 ;置0809通道0地址 启动0通道A/D ;启动0通道A/D 转主程序,并等待A/D A/D中断 ;转主程序,并等待A/D中断

⑵ 查询方式

工作在查询方式时,0809 EOC端可不必通过反相器与或相连 端可不必通过反相器与或相连, 工作在查询方式时,0809 EOC端可不必通过反相器与或相连, 直接与80C51 P1口或P3口中任一端线相连 口或P3口中任一端线相连。 直接与80C51 P1口或P3口中任一端线相连。 13】 20中 P1.0直接与 直接与0809 EOC端相连 端相连, 【例9-13】 图9-20中,用P1.0直接与0809 EOC端相连,试用查 询方式编制程序, 路模拟信号依次A/D转换一次, A/D转换一次 询方式编制程序,对8路模拟信号依次A/D转换一次,并把结果 存入以40H为首址的内RAM 40H为首址的内RAM中 存入以40H为首址的内RAM中。 解:

IO接口电路及其扩展

;写控制字

LD:

;最左边灯亮 ;指向B口 ;取显示数据

;查数据编码 ;写B口 ;延时

39

MB DB DB DB DB DB DB DB MOV MOV DJNZ DJNZ

A, R3

A R3, A LD 3FH 06H 5BH 4FH 66H 6DH 7DH 07H 7FH R7, #02H R6, #FFH R6, LOOP R7, DELAY

6

+5V

P0.0 P0.1 P0.2 P0.3 P0.4 P0.5 P0.6 P0.7

1Y1 1Y2 1Y3 1Y4 1Y5 1Y6 1Y7 1Y8 1G 2G 7 4 L S 2 4 4 1A1 1A2 1A3 1A4 1A5 1A6 1A7 1A8

MCS-51

P2.0 P2.1 P2.2 P2.3 P2.4 P2.5 P2.6 P2.7 RD WR

MOV DPTR, #0FEFFH MOVX A,@DPTR ;确定扩展芯片地址 ;将扩展输入口内容读入累加器A

当与74LS244相连的按键都没有按下时,输入全为 8 1,若按下某键,则所在线输入为0。

典型芯片—74LS245

9

图13-3 74LS244构成的简单输入端口(b)

10

13.1.3 简单的并行口输出

CS:片选信号线,低电平有效。

RD:读信号,控制8255A将数据或状 态信息送给CPU。 WR:写信号,控制CPU将数据或控制 信息到8255A。

A1,A2:地址线,这两个引脚上的信 号组合绝对对8255A内部的哪一个口或 寄存器进行操作。

22

8255的操作表

表13-1 8255的操作

/CS 0 0 0 0 A1 A0 00 01 10 11 WR 0 0 0 0 RD 1 1 1 1 操作 总线=>端口A 总线=>端口B 总线=>端口C 总线=>命令控制字

大学课程《微型计算机接口技术及其应用》课件PPT 第10章 并行接口

乙机:查询接收

receive: mov dx,302h in al,dx ;查询PC4(OBF*)=0? and al,10h jnz receive mov dx,300h ;接收数据 in al,dx mov ah,al

例10.3

乙机:接收响应

mov dx,303h mov al,00h ;使PC0(ACK*)=0

置位允许中断,复位禁止中断

对INTE的操作通过写入端口C的对应位实 现,INTE触发器对应端口C的位是作应答 联络信号的输入信号的哪一位,只要对那 一位置位/复位就可以控制INTE触发器

选通输入方式下

端口A的INTEA对应PC4 端口B的INTEB对应PC2

方式1输出引脚:A端口

PA7~PA0 INTEA PC6

C端口上半部:输出,C口下半部:输入

B端口:方式0输出

方式控制字:10110001B或B1H

初始化的程序段:

mov dx,0fffeh ;假设控制端口为FFFEH

mov al,0b1h

;方式控制字

out dx,al

;送到控制端口

2. 读写数据端口

初始化编程后:

当数据端口作为输入接口时,执行输入IN指 令将从输入设备得到外设数据

表示A口已经接收数据

PC0

INTRB

中断允许触发器

中断请求信号 请求CPU接收数据

方式1输入联络信号

STB*——选通信号,低电平有效

由外设提供的输入信号,当其有效时,将输入设备送 来的数据锁存至8255A的输入锁存器

IBF——输入缓冲器满信号,高电平有效

8255A输出的联络信号。当其有效时,表示数据已 锁存在输入锁存器

输出缓冲器满信号 表示CPU已经输出了数据

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

5

8255A芯片的控制字及其工作方式

8255A中各端口可有3种基本工作方式:

方式0:基本输入输出方式

12

8255A芯片应用举例 8255A的A口和B口工作在方式0下,A 口为输入端口,接有4个开关,B口为输出

端,接有一个七段发光二极管,连接电路

如图所示。编写一个程序,要求发光二极 管显示开关所拨通的数字。

13

14

源程序如下:

A_PORT B_PORT C_PORT CTRL_PORT EQU EQU EQU EQU 8020H 8022H 8024H 8026H

MOV DX, CTRL_PORT

OUT DX, AL

16

源程序如下: ADD1: MOV DX, A_PORT

IN AL, DX;读A口开关状态

AND AL, 0FH;屏蔽高4位 MOV BX, OFFSET TAB1;取段码表首地址 XLAT ;查表得段码

17

源程序如下:

MOV DX, B_PORT ;输出显示 OUT DX, AL

2

外部引脚

3

8255A芯片内部结构及其功能

A组 控制 A组 端口A A组 端口C 上部 B组 端口B B组 端口C 下部

4

PA0~PA7

D0~D7

数据 总线 缓冲器

内部数据线

PC4~PC7

RD WR A0 A1 CS RESET

B组 控制 读写 控制 逻辑

PB0~PB7

内部控制线

PC0~PC3

与处理器接口

(1) 定义工作方式控制字:

7

方式控制字:示例

要求: A端口:方式1输入 C端口上半部:输出,C口下半部:输入

B端口:方式0输出

方式控制字:10110001B或0B1H 初始化的程序段: MOV DX,0FFFEH ;假设控制端口为0FFFEH MOV AL,0B1H ;方式控制字 OUT DX,AL ;送到控制端口

DATA SEGMENT TAB1 DB 30H, 06H, 5BH, 4FH, … 31H

DATA ENDS

15

源程序如下:

CODE SEGMENT

ASSUME DS:DATA, CS:CODE

START: MOV AX, DATA

MOV DS, AX

MOV AL, 90H ;设置8255A方式字

MOV CX, 0600H

ADD2: LOOP ADD2;循环延时

JMP ADD1

CODE ENDS

END START

18

8

(2) 置位/复位控制字: 只对端口C有效,其使用格式如下图 所示

9

应用举例

设有某8255A的端口地址为60~63H,PC5平时 为低电平,要求该引脚输出一个正脉冲。 分析:可用程序先将PC5置1,输出一个高电 平,再将其清0,输出一个低电平,则该引脚上便 输出一个正脉冲。

MOV AL, 00001011B

《微机原理与接口技术》 第9章并行接口电路

2016/6/15

1

9.1 8255A的工作原理

教学目的: 通过并行接口8255A的学习和实践,接触具 体的接口形式,从而进一步加深对接口知识的理 解。 学习要求: 掌握可编程并行接口芯片8255A的结构,其三种 工作方式及特点;8255A的使用; 教学重点: 8255A的端口地址分配,方式0的功能及端口命令 字的设置。

OUT 63H, AL ;置PC5为高电平

MOV AL, 00001010B

OUT 63H, AL

;置PC5为低电平

10

应用举例

设有某8255A的端口地址为60~63H,PC5平时 为低电平,要求该引脚输出一个正脉冲。 分析:可用程序先将PC5置1,输出一个高电 平,再将其清0,输出一个低电平,则该引脚上便 输出一个正脉冲。

适用于无条件传送和查询方式的接口电路

适用于查询和中断方式的接口电路 适用于与双向传送数据的外设 适用于查询和中断方式的接口电路

方式1:选通输入输出方式

方式2:双向选通传送方式

用户可用软件来分别定义3个端口的工作方式,可使用 的控制字有定义工作方式控制字和置位/复位控制字。

6

控制字

MOV AL, 00001011B

OUT 63H, AL ;置PC5为高电平

MOV AL, 00001010B

OUT 63H, AL

;置PC5为低电平Biblioteka 11工作方式0

这是8255A中各端口的基本输入/输出方式。它只完成 简单的并行输入/输出操作,CPU可从指定端口输入信 息,也可向指定端口输出信息。 如果3个端口均处于工作方式0,则可由工作方式控制 字定义16种工作方式的组合。