加减交替阵列除法器的设计与仿真实现

实验一四位加法器和减法器设计

实验一四位加法器和减法器设计一、实验背景在数字电路设计中,常常需要使用加法器和减法器来实现数字的加法和减法运算。

本实验的目的是设计一个四位加法器和一个四位减法器,将数字电路理论知识应用到实际电路设计中。

二、实验目的1.理解加法器和减法器的基本原理;2.掌握数字电路的设计方法;3.通过实验验证设计的正确性和可行性。

三、实验原理1.加法器原理加法器是一种能对两个二进制数进行相加运算的数字电路。

常用的加法器有半加法器、全加法器等。

其中,半加法器能够对两个1位二进制数进行相加运算,全加法器能对两个1位二进制数及一个进位进行相加运算。

2.减法器原理减法器是一种能对两个二进制数进行相减运算的数字电路。

减法器可以通过使用补码的方式进行实现。

四、实验设备和材料1.实验平台:数字电路实验箱;2.实验元件:逻辑门IC芯片、电路连接线等。

1.设计四位加法器电路:a.首先,设计并连接四个1位全加法器。

将输入端A、B和上一个全加法器的进位连线,将输出端S和进位连线,其中S为本全加法器的输出,进位作为下一个全加法器的输入。

b.最后一个全加法器的输出即为四位加法器的输出结果。

2.设计四位减法器电路:a.首先,将被减数输入端A和减数输入端B分别与减法器的输入端连接。

b.接下来,使用非门将减数B的每一位取反。

c.然后,将取反后的减数与被减数相加,得到相加结果。

d.最后,将相加结果输入到四位加法器电路中,即可得到减法结果。

六、实验验证2.搭建四位减法器电路,并输入A=1100、B=1010进行验证。

验证结果应为A-B=010。

七、误差分析及改进方法1.设计电路时要注意连接线的长度和接触的质量,以保证电路的正常运行。

2.如果电路不能正常工作,可以仔细检查电路连接是否正确,逐个排查错误并改正。

通过设计、搭建和验证的四位加法器和减法器电路,可以实现对二进制数的加法和减法运算。

九、实验心得通过本次实验,我深入了解了加法器和减法器的原理和实现方法。

阵列除法器

沈阳航空工业学院课程设计报告课程设计名称:计算机组成原理课程设计课程设计题目:阵列除法器的设计院(系):计算机学院专业:计算机科学与技术班级:7401101学号:*****************指导教师:***完成日期:2010年1月15日沈阳航空工业学院课程设计报告目录第1章总体设计方案 (1)1.1设计原理 (1)1.2设计思路 (2)1.3设计环境 (3)第2章详细设计方案 (6)2.1顶层方案图的设计与实现 (6)2.1.1创建顶层图形设计文件 (6)2.1.2器件的选择与引脚锁定 (7)2.1.3编译、综合、适配 (8)2.2功能模块的设计与实现 (8)2.3仿真调试 (10)第3章编程下载与硬件测试 (12)3.1编程下载 (12)3.2硬件测试及结果分析 (12)参考文献 (14)附录(电路原理图) (15)第1章总体设计方案1.1 设计原理阵列除法器的功能是利用一个可控加法/减法(CAS)单元所组成的流水阵列来实现的。

它有四个输出端和四个输入端。

当输入线P=0时,CAS作加法运算;当P=1时,CAS作减法运算。

可控加法/减法(CAS)单元的逻辑电路图如图1.1所示。

图1.1可控加法/减法(CAS)单元的逻辑图CAS单元的输入与输出关系可用如下一组逻辑方程来表示:S i=A i ⊕(B i ⊕P) ⨁CC i+1=(A i+C i) ∙(B i ⊕P)+A i C i当P=0时,就得到我们熟悉的一位全加器(FA)的公式:S i=A i ⊕B i ⊕C iC i+1=A i B i+B i C i+A i C i当P=1时,则得求差公式:S i=A i ⨁B i '⨁C iC i+1=A i B i '+B i 'C i+A i C i其中B i '=B i⨁1。

在减法情况下,输入C i称为借位输入,而C i+1称为借位输出。

不恢复余数的除法也称加减交替法。

计算机组成原理实验报告-八位补码加减法器的设计与实现

计算机科学与技术学院计算机组成原理实验报告书实验名称八位补码加/减法器的设计与实现班级学号姓名指导教师日期成绩实验1八位补码加/减法器的设计与实现一、实验目的1.掌握算术逻辑运算单元(ALU)的工作原理。

2.熟悉简单运算器的数据传送通路。

3.掌握8位补码加/减法运算器的设计方法。

4.掌握运算器电路的仿真测试方法二、实验任务1.设计一个8位补码加/减法运算器(1)参考图1,在QUARTUS II里输入原理图,设计一个8位补码加/减法运算器。

(2)创建波形文件,对该8位补码加/减法运算器进行功能仿真测试。

(3)测试通过后,封装成一个芯片。

2.设计8位运算器通路电路参考下图,利用实验任务1设计的8位补码加/减法运算器芯片建立运算器通路。

3.利用仿真波形,测试数据通路的正确性。

设定各控制信号的状态,完成下列操作,要求记录各控制信号的值及时序关系。

(1)在输入数据IN7~IN0上输入数据后,开启输入缓冲三态门,检查总线BUS7~BUS0上的值与IN0~IN7端输入的数据是否一致。

(2)给DR1存入55H,检查数据是否存入,请说明检查方法。

(3)给DR2存入AAH,检查数据是否存入,请说明检查方法。

(4)完成加法运算,求55H+AAH,检查运算结果是否正确,请说明检查方法。

(5)完成减法运算,分别求55H-AAH和AAH-55H,检查运算结果是否正确,请说明检查方法。

(6)求12H+34H-56H,将结果存入寄存器R0,检查运算结果是否正确,同时检查数据是否存入,请说明检查方法。

三、实验要求(1)做好实验预习,掌握运算器的数据传送通路和ALU的功能特性。

(2)实验完毕,写出实验报告,内容如下:①实验目的。

②实验电路图。

③按实验任务3的要求,填写下表,以记录各控制信号的值及时序关系。

表中的序号表示各控制信号之间的时序关系。

要求一个控制任务填一张表,并可用文字对有关内容进行说明。

序号nsw-busnR0-BUSLDR0LDR1LDR2mnalu-busIN7~INBUS7~BUS0 ⑤实验体会与小结。

汇编语言课程设计报告实现加减乘除四则运算的计算器

汇编语言课程设计报告实现加减乘除四则运算的计算器实现加减乘除四则运算的计算器目录1 概述 (1)1.1 课程设计目的 (1)1.2 课程设计内容 (1)2 系统需求分析 (1)2.1 系统目标 (1)2.2 主体功能 (2)3 系统概要设计 (2)3.1 系统的功能模块划分 (2)3.2 系统流程图 (3)4系统详细设计 (4)5 测试 (5)5.1 正确输出 (5)5.2 实际输出 (6)6 小结 (7)参考文献 (8)附录 (9)附录1 源程序清单 (9)汇编语言课程设计报告(2011)实现加减乘除四则运算计算器的设计1 概述1.1 课程设计目的运用汇编语言,实现简单计算器的一般功能.通过该程序设计,让我们熟悉并掌握DOS系统功能调方法用及BIOS系统功能调用方法,同时在程序设计过程中熟悉并掌握各种指令的应用,知道编程的具体流程,以及掌握DEBUG的一系列的功能执行命令,及用它进行调试,运行功能。

汇编语言是计算机能够提供给用户使用的最快而又最有效的语言,也是能够利用计算机所有硬件特性并能直接控制硬件的唯一语言。

由于汇编语言如此的接近计算机硬件,因此,它可以最大限度地发挥计算机硬件的性能。

由此可见汇编语言的重要性,学好这门课程,同样可为相关的专业打下基础。

汇编语言程序设计课程设计是在教学实践基础上进行的一次试验,也是对该课程所学理论知识的深化和提高。

因此,要求学生能综合应用所学知识,设计和制造出具有具有一定功能的应用系统,并且在实验的基本技能方面进行了一次全面的训练。

此外,它还可以培养学生综合运用所学知识独立完成汇编程序课题的能力,使学生能够较全面的巩固和应用课堂上所学的基本理论和程序设计方法,能够较熟练地完成汇编语言程序的设计和调试。

它同样可以提高学生运用理论去处理实际问题的能力和独立思考的能力,使学生的编程思想和编程能力有所提高,最终达到熟练地掌握编写汇编源程序的基本方法的目的。

1.2 课程设计内容设计一个能实现加减乘除取余计算的程序。

加减法运算器的设计与实现

加减法运算器的设计与实现计算机组成原理实验实验二加减法运算器的设计与实现专业班级:计算机科学与技术学号:0936008 姓名:冯帆学号:0936036 姓名:张琪实验地点:理工楼901实验二加减法运算器的设计与实现一、实验目的1、掌握加减法运算器的原理图设计方法2、掌握加减法运算器的V erilog HDL语言描述方法3、理解超前进位算法的基本原理4、掌握基于模块的多位加减运算器的层次化设计方法5、掌握溢出检测方法和标志线的生成技术6、掌握加减运算器的宏模块设计方法二、实验内容1、完成一个4位行波进位的加减法运算器,要求有溢出和进位标志(参阅P75-82 ,P86),并封装成模块。

2、修改上述加减运算器改为超前进位加法运算器,并封装成模块。

(参阅P72-75)3、在上述超前进位加法运算器的基础上,用基于模块的层次化设计方法,完成一个16位行波进位的加法运算器。

//组内超前进位,组间行波进位4、用宏模块的方法实现一个8位加减运算器。

三、实验仪器及设备:PC机+ QuartusⅡ9.0 + DE2-70四、实验步骤1、新建工程。

2、新建verilog文件。

3、分析寄存器程序代码并编译。

附代码如下:/*四位行波进位加减法器*/`define WEISHU 4module hbjw(a,b,cin,sub,cout,s,overflow); input [`WEISHU-1:0]a;input [`WEISHU-1:0]b;input cin;input sub;output cout;output [`WEISHU:0]s;output overflow;wire w_0;wire w_1;wire w_2;wire w_3;wire [`WEISHU:0]w;assign w=sub?(~b+1'b1):b;assign {w_0,s[0]}=a[0]+w[0]+cin;assign {w_1,s[1]}=a[1]+w[1]+w_0;assign {w_2,s[2]}=a[2]+w[2]+w_1;assign {w_3,s[3]}=a[3]+w[3]+w_2;assign {cout,s[4]}=a[3]+w[4]+w_3;assign overflow=s[4]^s[3];endmodule/*超前进位加减法运算器*/module lab2_LookaheadCarry // 4位超前进位无符号(input [3:0] a,input [3:0] b,input c0, //carry_ininput clk,input cclr,output reg carry_out,output reg [3:0]sum);//内部变量wire c1,c2,c3,c4;wire p0,p1,p2,p3; //进位产生信号wire g0,g1,g2,g3; //进位传递信号wire sum0,sum1,sum2,sum3;assign g0=a[0]&b[0];assign g1=a[1]&b[1];assign g2=a[2]&b[0];assign g3=a[3]&b[0];assign p0=a[0]^b[0];assign p1=a[1]^b[1];assign p2=a[2]^b[2];assign p3=a[3]^b[3];assign c1=g0|c0&p0assign c2=g1|(g0&p1)|(c0&p0&p1);// g1 + p1g0 + p1p0c0 assign c3=g2|(g1&p2)|(g0&p1&p2)|(c0&p0&p1&p2);//g2 + p2g1 + p2p1g0 + p2p1p0c0 assign c4=g3|(g2&p3)|(g1&p2&p3)|(g0&p0&p1&p2)|(c0&p0&p1&p2 &p3);//g3 + p3g2 + p3p2g1 + p3p2p1g0 + p3p2p1p0c0 assign sum0=p0^c0;assign sum1=p1^c1;assign sum2=p2^c2;assign sum3=p3^c3;always @ (posedge clk or negedge cclr)beginif (!cclr )beginsum<= 0;carry_out<=0;endelsebeginsum<={sum3,sum2,sum1,sum0};carry_out<=c4;endendendmodule/*宏模块加减法器*/`define WEISHU 8module hmk(add,cin,a,b,cout,overflow,s); //加法:cin cout overflow都是1有效减法:cin cout overflow都是0有效Add信号为高电平时做加法,低电平时做减法input add;input cin;input [`WEISHU-1:0]a;input [`WEISHU-1:0]b;output cout;output overflow;output [`WEISHU-1:0]s;lpm_add_sub0 h (.add_sub (add),.cin (cin ),.dataa (a ),.datab (b ),.cout ( cout ),.overflow (overflow ), .result ( s ));Endmodule4、仿真。

阵列除法器设计与实现

课程设计报告课程设计名称:计算机组成原理课程设计课程设计题目:阵列除法器设计与实现院(系):计算机学院专业:班级:学号:姓名:指导教师:完成日期:2016年1月12日目录第1章总体设计方案 01。

1设计原理 01.2设计思路 (2)1.3设计环境 (2)第2章详细设计方案 (4)2.1功能模块的设计与实现 (4)2。

1。

1细胞模块的设计与实现 (4)2.1.2除法器模块的设计与实现 (6)2.2仿真调试 (8)参考文献 (10)附录(电路原理图).11第1章总体设计方案1.1 设计原理在原码除法中,原码除法符号位是单独处理的,商符由两数符号位进行异或运算求得,商值由两数绝对值相除求得.原码除法中由于对余数的处理不同,又可分为恢复余数法和不恢复余数法(加减交替法)。

在机器操作中通常采用加减交替法,因为加减交替法机器除法时间短,操作规则。

加减交替法的运算规则如下:(1)当余数为正时,上商1,余数左移一位后减去除数得下一位余数.(2)当余数为负时,上商0,余数左移一位后加上除数得下一位余数.阵列除法器是一种并行运算部件,采用大规模集成电路制造,与早期的串行除法器相比,阵列除法器不仅所需的控制线路少,而且能提供令人满意的高速运算速度。

阵列除法器有多种形式,如不恢复余数阵列除法器、补码阵列除法器等等。

本实验设计的是加减交替阵列除法器。

本实验利用的细胞单元是一个可控加法/减法CAS单元,利用它组成的流水阵列来实现四位小数的除法.CAS单元有四个输入端、四个输出端。

其中有一个控制输入端P,当P=0时,CAS作加法运算;当P=1时,CAS作减法运算。

逻辑结构图如图1。

1所示。

图1。

1 可控加法/减法(CAS)单元逻辑结构图CAS单元的输入与输出的关系可用如下逻辑方程来表示:Si=Ai⊕(Bi⊕P)⊕CiCi+1=(Ai+Ci)(Bi⊕P)+AiCi当P=0时,CAS单元就是一个全加器,如下:Si=Ai⊕B⊕iCiCi+1=AiBi+BiCi+AiCi当P=1时,则得求差公式:Si=Ai⊕B⊕iCiCi+1=AiBi+BiCi+AiCi其中有Bi=Bi⊕1在减法中,输入称为借位输入,而称为借位输出。

组成原理,除法器

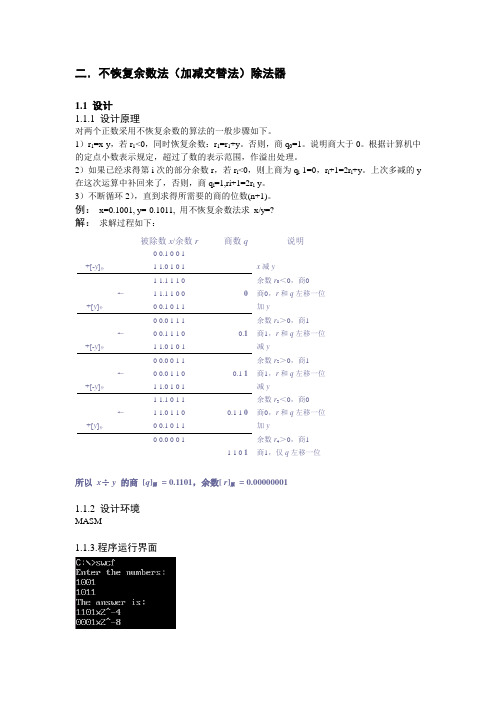

二.不恢复余数法(加减交替法)除法器1.1 设计1.1.1 设计原理对两个正数采用不恢复余数的算法的一般步骤如下。

1)r 1=x-y ,若r 1<0,同时恢复余数:r 1=r 1+y 。

否则,商q 0=1。

说明商大于0。

根据计算机中的定点小数表示规定,超过了数的表示范围,作溢出处理。

2)如果已经求得第i 次的部分余数r ,若r i <0,则上商为q i -1=0,r i +1=2r i +y 。

上次多减的y 在这次运算中补回来了,否则,商q i =1,ri+1=2r i -y 。

3)不断循环2),直到求得所需要的商的位数(n+1)。

例: x=0.1001, y=-0.1011, 用不恢复余数法求 x/y=? 解: 求解过程如下:所以 x ÷ y 的商 [q ]原 = 0.1101,余数[ r ]原 = 0.000000011.1.2 设计环境MASM1.1.3.程序运行界面被除数x /余数r商数q说明0 0.1 0 0 1 +[-y ]补1 1.0 1 0 1 x 减y1 1.1 1 1 0 余数r 0<0,商0←1 1.1 1 0 0 0 商0,r 和q 左移一位 +[y ]补0 0.1 0 1 1 加y0 0.0 1 1 1 余数r 1>0,商1←0 0.1 1 1 0 0.1 商1,r 和q 左移一位 +[-y ]补1 1.0 1 0 1 减y0 0.0 0 1 1 余数r 2>0,商1←0 0.0 1 1 0 0.1 1 商1,r 和q 左移一位+[-y ]补1 1.0 1 0 1 减y1 1.1 0 1 1 余数r 3<0,商0←1 1.0 1 1 0 0.1 1 0 商0,r 和q 左移一位+[y ]补0 0.1 0 1 1 加y 0 0.0 0 0 1余数r 4>0,商11 1 0 1 商1,仅q 左移一位运行程序,显示“Enter the numbers :”依次输入2个四位小数作为被除数和除数,如0.1001就输入1001(被除数必须小于除数) 显示结果“The answer is : 商 余数” 尚存除尽时余数显示有问题的bug ,待改进1.2 程序流程图程序开始,建立DA TA 段调用IN_DL 过程,读取被除数与除数分别存放在BL 、BH ,将除数的补码存至BHBBL=BL+BHB , CX=4BL<0SHANG+=0 SHANG*=2SHANGBL*=2BL BL=BL+BHSHANG+=1 SHANG*=2SHANG BL*=2BL BL=BL+BHBCX-=1调用Out_DL_oAX 过程,输出SHANG 和BL ,利用PS 确定正负程序结束,中断返回CX=0?YNYN1.3 程序分析1.3.1 输入模块IN_DLIN_DL PROC NEARPUSH AXPUSH CXXOR DL, DLMOV CX, 4INPUT: MOV AH, 1 //调用中断,读取一位输入的ASCII码INT 21HCMP AL, '0' //输入0JE Num01CMP AL, '1' //输入1JE Num01CMP AL, 32 //输入空格JE EOICMP AL, 45 //输入负号JE XPSCALL ERROR_I //其他输入,视为错误,调用ERROR_I XPS: NOT PS //符号位取反INC CX //由于输入了负号,需多输入一位数字Num01: SHL DL, 1SUB AL, '0' //将数字的ASCII码转为数字ADD DL, AL //存放一位LOOP INPUTEOI: P OP CX //输入完毕,结束POP AXRETIN_DL ENDP1.3.2 错误信息模块ERROR_I作用:输入错误时调用,中断程序,并在屏幕上输出:“Error Input!!”的信息1.3.3 输出模块Out_DL_oAXOut_DL_oAX PROC NEARPUSHFPUSH DXPUSH CXPUSH AXMOV DH, DLMOV CL, 8SUB CL, ALSHL DH, CLMOV CL, ALDIS: SHL DH, 1JC DIS1MOV DL, '0'JMP EODDIS1: MOV DL, '1'EOD: MOV AH, 2INT 21HLOOP DIS;LEA DX, LINE;MOV AH, 9;INT 21HPOP AXPOP CXPOP DXPOPFRETOut_DL_oAX ENDP1.3.4 程序主体BEG: ADD BL, BHBAND BL, 3FH XUNHUAN: MOV F, 30HAND F, BLCMP F, 30HJE FUADD SHANG, 1SHL SHANG, 1SHL BL, 1ADD BL, BHBAND BL, 3FHJMP HUIQUXUNHUAN FU: ADD SHANG, 0SHL SHANG, 1SHL BL, 1ADD BL, BHAND BL, 3FH HUIQUXUNHUAN: LOOP XUNHUANMOV F, 30HAND F, BLCMP F, 30HJE LASTFUADD SHANG, 1JMP RESULTLASTFU: ADD SHANG, 01.4.心得体会:在这次的课程设计增进了我很多对汇编语言的理解,也学会了与同学们合理合作,共同成功。

加减法器的设计

本文运用数字电路知识来设计加减法器,在PROTEUS中仿真出电路原理图,通过控制开关的闭合来模拟数据的输入以及控制控制开关来选择加法器或者减法器。

通过数码管的显示可以看到所输入的数据以及输入数据的运算结果。

通过加减法器的课程设计,可以从中学习和巩固数字电路的相关知识。

比如,减法器电路的设计,全加器芯片以及各种逻辑门器件的使用等等。

关键字:加减法器;数码管;逻辑门;全加器;PROTEUS。

1概述 (1)2方案设计 (2)2.1设计要求 (2)2.2方案设计 (2)2.3设计原理 (3)3电路设计 (4)3.1置数电路的设计 (4)3.2加减法器电路的设计 (5)3.3数码管显示电路的设计 (5)3.4完整电路图的设计 (6)4仿真与调试 (7)4.1系统仿真步骤 (7)4.2系统仿真结果分析 (7)5总结 (10)参考文献 (11)致谢 (12)第1章概述目前,随着社会经济的发展,运算是人们生活中必不可少的,因此设计性能可靠的计算器是很有必要的。

信息技术代表着当今先进生产力的发展方向,信息技术的广泛应用使信息的重要生产要素战略资源的作用得以发挥,使人们能更高效地进行资源优化配置,从而推动传统产业不断升级,提高社会劳动生产率和社会运行效率。

21世纪初,人类将全面迈向一个信息时代,信息技术革命是经济全球化的重要推动力量和桥梁,是促进全球经济和社会发展的主导力最,以信息技术为中心的新技术革命将成为世界经济发展史上的新亮点。

信息技术将使人类能够进一步把潜藏在物质运动中的巨大信息资源挖掘出来,把世界变成一个没有边界的信息空间,以微处理机进入亿万办公室和家庭、超级计算机问世、卫星通信与光导通信的发展,特别是网络化的迅速发展为标志的,信息技术革命不仅以最为便捷的方式沟通了各国、各地区、各企业、各团体以及个人之间的联系,而且在一定程度上打破了种种地域乃至国家的限制,把核个世界空前地联系在一起,推动了全球化的迅速发展。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

加减交替阵列除法器的设计与仿真实现

一、引言

随着数字电路的发展,除法器在计算机和通信系统中的应用越来越广泛。

加减交替阵列除法器是一种高效的除法器,具有运算速度快、面

积小等优点。

本文将详细介绍加减交替阵列除法器的设计与仿真实现。

二、加减交替阵列除法器原理

加减交替阵列除法器是一种基于移位和加减运算的快速除法器。

其主

要原理如下:

1. 将被除数左移n位,得到一个n+1位的数(其中最高位为0)。

2. 对于每个n+1位的数,采用加减交替的方式进行运算。

3. 在第n步时,判断商是否已经求出。

4. 如果商未求出,则返回第1步。

三、加减交替阵列除法器设计

1. 系统框图

加减交替阵列除法器由以下模块组成:被除数寄存器、商寄存器、余

数寄存器、控制单元、计算单元和状态机。

系统框图如下所示:

2. 系统模块设计

(1)被除数寄存器

被除数寄存器用于存储待处理的被除数。

它由一个n位的寄存器和一

个移位器组成,可以将被除数左移n位。

(2)商寄存器

商寄存器用于存储计算得到的商。

它由一个n位的寄存器和一个移位

器组成,可以将商左移1位。

(3)余数寄存器

余数寄存器用于存储计算得到的余数。

它由一个n+1位的寄存器和一个移位器组成,可以将余数左移1位。

(4)控制单元

控制单元用于控制整个系统的运行。

它根据状态机的输出信号来控制

各个模块之间的数据传输和运算。

(5)计算单元

计算单元是加减交替阵列除法器最核心的部分,用于进行加减运算。

它由若干个加法器和减法器组成,每个加法器或减法器都能够进行一

次加或减运算。

(6)状态机

状态机用于控制控制单元的工作状态,并输出相应的信号。

它有以下

三种状态:

a. 初始化状态:在这个状态下,被除数、商、余数等变量都被初始化。

b. 运行状态:在这个状态下,加减交替阵列除法器按照原理进行运算。

c. 结束状态:在这个状态下,商已经求出,整个系统停止工作。

四、加减交替阵列除法器仿真实现

1. 系统仿真

为了验证加减交替阵列除法器的正确性,需要对其进行仿真。

采用Verilog HDL语言对系统进行建模,并使用ModelSim软件进行仿真。

2. 仿真结果分析

在ModelSim软件中运行仿真程序,可以得到如下波形图:

从波形图可以看出,加减交替阵列除法器的运行过程符合设计原理,并且最终得到了正确的商和余数。

五、总结

本文详细介绍了加减交替阵列除法器的设计原理和仿真实现。

通过对系统进行建模和仿真,证明了该除法器具有高效、快速、面积小等优点。

同时,本文还介绍了系统框图和各个模块的设计方法。