ADC过采样

实验8 adc采样和信号滤波实验

实验8 adc采样和信号滤波实验1.实验目的熟悉adc模块的各个寄存器,学会如何通过程序语言配置adc的各种属性并采集模拟信号,并使用过采样和数字滤波算法减小噪声。

2.实验主要内容(1)在CCS软件中,用C语言编写程序配置adc的各种属性并采集到模拟信号。

(2)编写程序配置epwm的各种属性,使其以100kHZ的频率触发adc进行采样。

(3)编写程序进行过采样,以及数字滤波。

3.实验基本原理(1)adc模块模数转换模块ADC有16个通道,可配置为2个独立的8通道模块,服务于ePWM模块。

两个独立的8通道模块也可以级联构成一个16通道模块。

尽管在模数转换模块中有多个输入通道和两个排序器,但仅有一个转换器。

ADC模块的功能框图如图所示。

(2)数字滤波器原理一阶低通滤波器的公式为:()c 11y G s s x ω==+将其离散化后,可得到:()()()s c s c s c1111T y k y k x k T T ωωω=-+++可通过程序的编写来实现此低通滤波器。

4. 实验过程和关键程序解读(1) 打开AD 实验的工程(2) 阅读adc 配置的代码,本工程内对adc 配置的主要代码如下:配置的主要属性有,adc采样时间窗ACQ_PS、内核时钟分频ADCCLKPS,级联操作选择SEQ_CASC,SEQ中断使能,SOCA触发允许等。

(3)修改主程序,使得能够完成实验要求i.首先,配置epwm,使其产生出发adc的SOC信号,SOCASEL设定为4,代表达到CMPA触发。

ii.修改EPWM时钟频率,EPWM时钟频率= SYSCLK / (HSPCLKDIV * CLKDIV ),及150M/2 = 75MHZ。

iii.设定技术周期和比较周期:计数周期设为749,则触发adc的周期为75M/(749+1) = 100KHZA通道比较值的设定即可比较随意,每周期只会达到一次。

iv.编写过采样的代码简单来说就是同时采集多次取平均。

过采样插值ADC

MT-017指南过采样插值DAC作者:Walt Kester简介过采样和数字滤波有助于降低对ADC 前置的抗混叠滤波器的要求。

重构DAC 可以通过类似的方式运用过采样和插值原理。

例如,数字音频CD 播放器常常采用过采样,其中来自CD 的基本数据更新速率为44.1 kSPS 。

早期CD 播放器使用传统的二进制DAC ,并将“0”插入并行数据中,从而将有效更新速率提高到基本吞吐速率的4倍、8倍或16倍。

4×、8×或16×数据流通过一个数字插值滤波器,产生额外的数据点。

高过采样速率将镜像频率移动到更高位置,从而可以使用较为简单、成本更低、过渡带更宽的滤波器。

此外,由于存在处理增益,信号带宽内的SNR 也会提高。

Σ-Δ型DAC 架构使用高得多的过采样速率,将这一原理扩展到极致,因而在现代CD 播放器中颇受欢迎。

同样的过采样和插值原理也可用于通信领域的高速DAC ,以便降低对输出滤波器的要求,并利用处理增益提高SNR 。

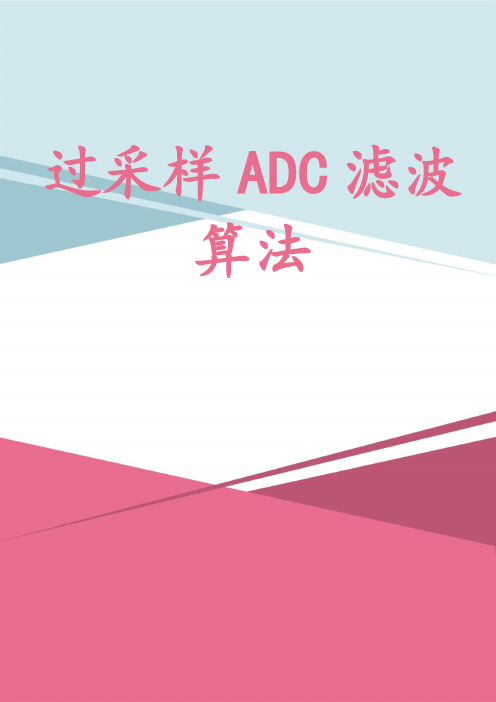

重构DAC 的输出频谱重构DAC 的输出可以表示为一系列矩形脉冲,其宽度等于时钟速率的倒数,如图1所示。

0.5f c f c 1.5f c 2f c 2.5f c 3f c1A 0图1:显示镜像和sin (x)/x 滚降的无滤波DAC 输出请注意,在奈奎斯特频率f c/2,重构信号幅度降低3.92 dB。

如果需要,可以使用一个反sin(x)/x滤波器来补偿此效应。

基波信号的镜像作为采样函数的结果出现,并且也通过sin(x)/x函数衰减。

过采样插值DAC过采样/插值DAC的基本原理如图2所示。

N位输入数据字以速率f c接收。

数字插值滤波器以等于过采样频率Kf c的时钟速率工作,并插入额外的数据点。

对输出频谱的影响如图2所示。

在奈奎斯特采样频率下(A),对模拟抗镜像滤波器的要求可能相当高。

通过过采样和插值,可以大大降低对该滤波器的要求,如(B)所示。

此外,量化噪声分布在比原始信号带宽更宽的区域内,因而信噪比也会有所提高。

过采样ADC滤波算法

过采样ADC滤波算法过采样ADC滤波算法过采样ADC(Analog-to-Digital Converter)是一种常用的模拟信号转换为数字信号的技术。

它通过在模拟信号采样过程中进行多次采样,然后通过数字滤波算法对这些采样值进行处理,以提高精度和抗干扰能力。

下面我们来逐步介绍过采样ADC滤波算法的实现步骤:第一步:采样首先,我们需要对模拟信号进行采样。

过采样ADC通常会以更高的采样率进行采样,从而提高系统的抗干扰能力和准确度。

在这一步骤中,我们会得到一系列模拟信号的采样值。

第二步:建立滤波器接下来,我们需要建立一个数字滤波器来对采样值进行处理。

这个滤波器通常是一个数字滤波算法,如FIR(Finite Impulse Response)滤波器或IIR (Infinite Impulse Response)滤波器。

滤波器的功能是去除采样值中的噪声和不必要的频率成分。

第三步:插值在这一步骤中,我们会对采样值进行插值处理。

插值是一种通过已知数据点,估计其他位置上数值的方法。

常用的插值方法有线性插值、多项式插值等。

插值的目的是增加采样点,使得滤波器的输出更加平滑。

第四步:滤波现在,我们可以将插值后的采样值输入到滤波器中进行滤波。

滤波器会根据采样值的频域特性进行处理,去除不需要的频率成分,并将滤波后的结果输出。

第五步:降采样最后,我们需要对滤波器的输出进行降采样。

降采样是将高采样率的数据转换为低采样率的数据。

这可以通过简单地选择输出数据中的每第n个样本来实现,其中n是降采样的因子。

通过以上步骤,我们成功地实现了过采样ADC滤波算法。

这个算法能够有效地提高系统的精度和抗干扰能力,适用于很多需要高质量信号转换的应用领域,如音频处理、无线通信等。

总结起来,过采样ADC滤波算法的步骤包括采样、建立滤波器、插值、滤波和降采样。

通过这些步骤的处理,我们可以获得更准确、更稳定的数字信号。

利用过采样技术提高ADC测量微弱信号时的分辨率

利用过采样技术提高ADC 测量微弱信号时的分辨率 1. 引言 随着科学技术的发展,人们对宏观和微观世界逐步了解,越来越多领域(物理学、化学、天文学、军事雷达、地震学、生物医学等)的微弱信号需要被检测,例如:弱磁、弱光、微震动、小位移、心电、脑电等[1~3]。

测控技术发展到现在,微弱信号检测技术已经相对成熟,基本上采用以下两种方法来实现:一种是先将信号放大滤波,再用低或中分辨率的ADC 进行采样,转化为数字信号后,再做信号处理,另一种是使用高分辨率ADC ,对微弱信号直接采样,再进行数字信号处理。

两种方法各有千秋,也都有自己的缺点。

前一种方法,ADC 要求不高,特别是现在大部分微处理器都集成有低或中分辨率的ADC ,大大节省了开支,但是增加了繁琐的模拟电路。

后一种方法省去了模拟电路,但是对ADC 性能要求高,虽然∑-△ADC 发展很快,已经可以做到24位分辨率,价格也相对低廉,但是它是用速度和芯片面积换取的高精度[4],导致采样率做不高,特别是用于多通道采样时,由于建立时间长,采样率还会显著降低,因此,它一般用于低频信号的单通道测量,满足大多数的应用场合。

而本文提出的方案,可以绕过上述两种方法的缺点,利用两者的优点实现微弱信号的高精度测量。

过采样技术是提高测控系统分辨率的常用方法,已经被广泛应用于各个领域。

例如,过采样成功抑制了多用户CDMA 系统中相互正交用户码接收机(A Mutually Orthogonal Usercode-Receiver ,AMOUR )的噪声[5~6],提高了光流估计(optical flow estimation ,OFE )的精度[7],改善了正交频分复用(OFDM )信号的峰-均比[8]等。

但是,这些过采样技术应用的前提是采样前的信号幅值能与ADC 的输入范围相当。

而用ADC 采集微弱信号时,直接使用过采样技术提高不了精度,而且由于信号幅值远小于ADC 的输入范围,它的有效位数还会减小,使精度随之下降。

ADC的分类及关键指标

浅析ADC的六种分类以及六大关键性能指标过采样频率:增加一位分辨率或每减小6dB 的噪声,需要以4 倍的采样频率fs 进行过采样.假设一个系统使用12 位的ADC,每秒输出一个温度值(1Hz),为了将测量分辨率增加到16 位,按下式计算过采样频率:fos=4^4*1(Hz)=256(Hz)。

1. AD转换器的分类下面简要介绍常用的几种类型的基本原理及特点:积分型、逐次逼近型、并行比较型/串并行型、Σ-Δ调制型、电容阵列逐次比较型及压频变换型。

1)积分型积分型AD工作原理是将输入电压转换成时间(脉冲宽度信号)或频率(脉冲频率),然后由定时器/计数器获得数字值。

其优点是用简单电路就能获得高分辨率,抗干扰能力强(为何抗干扰性强?原因假设一个对于零点正负的白噪声干扰,显然一积分,则会滤掉该噪声),但缺点是由于转换精度依赖于积分时间,因此转换速率极低。

初期的单片AD转换器大多采用积分型,现在逐次比较型已逐步成为主流。

2)逐次比较型SAR逐次比较型AD由一个比较器和DA转换器通过逐次比较逻辑构成,从MSB开始,顺序地对每一位将输入电压与内置DA转换器输出进行比较,经n次比较而输出数字值。

其电路规模属于中等。

其优点是速度较高、功耗低,在低分辩率(<12位)时价格便宜,但高精度(>12位)时价格很高。

3)并行比较型/串并行比较型并行比较型AD采用多个比较器,仅作一次比较而实行转换,又称FLash(快速)型。

由于转换速率极高,n位的转换需要2n-1个比较器,因此电路规模也极大,价格也高,只适用于视频AD转换器等速度特别高的领域。

串并行比较型AD结构上介于并行型和逐次比较型之间,最典型的是由2个n/2位的并行型AD转换器配合DA转换器组成,用两次比较实行转换,所以称为Half flash(半快速)型。

还有分成三步或多步实现AD转换的叫做分级(Multistep/Subrangling)型AD,而从转换时序角度又可称为流水线(Pipelined)型AD,现代的分级型AD中还加入了对多次转换结果作数字运算而修正特性等功能。

基于stm32微控制器的过采样技术研究与实现

基于stm32微控制器的过采样技术研究与实现过采样(Oversampling)技术是指通过提高采样率,对输入信号进行多次采样,以提高较低采样率下的信号精度和动态范围。

在基于STM32微控制器的过采样技术研究与实现上,通常会使用STM32的内置模数转换器(ADC)模块来进行过采样。

以下是一种可能的实现方法:1. 初始化ADC模块:首先,需要初始化ADC模块的相关参数,包括采样率、精度、通道等。

可以通过寄存器配置或者使用CubeMX等开发工具进行初始化。

2. 设置过采样参数:设置过采样率和过采样模式。

过采样率一般选择为4倍或8倍,可以根据实际需求进行调整。

过采样模式有两种:线性过采样和峰值过采样。

线性过采样模式将多次采样的结果相加取平均值,峰值过采样模式则选择多次采样中的最大值作为结果。

3. 进行过采样采样:按照设置的过采样率进行多次采样,可以使用ADC的DMA 模式进行连续采样,也可以使用定时器中断触发采样。

每次采样完成后,将采样结果保存到缓冲区中。

4. 处理过采样结果:根据选择的过采样模式,对采样结果进行处理。

线性过采样模式下,将多次采样结果相加,然后除以过采样率得到平均值;峰值过采样模式下,选择多次采样中的最大值作为结果。

处理后的结果可以直接使用,也可以进一步进行滤波等处理。

需要注意的是,在进行过采样时,需要考虑处理器的处理能力和存储空间。

过高的过采样率会占用较多的处理能力和存储空间,可能导致系统性能下降。

因此,需要根据实际需求进行权衡和优化。

此外,还可以使用STM32的其他功能模块,如滤波器模块和定时器模块,对过采样结果进行进一步处理和控制。

总之,基于STM32微控制器的过采样技术研究与实现可以通过配置ADC模块、设置过采样率和过采样模式、进行多次采样、处理采样结果等步骤来实现。

具体的实现方法可以根据实际应用需求和硬件资源进行调整和优化。

单片机内置ADC实现高分辨率采样

什么是过采样?在信号处理中,过采样是指以明显高于奈奎斯特速率的采样频率对信号进行采样。

从理论上讲,如果以奈奎斯特速率或更高的速率进行采样,则可以完美地重建带宽受限的信号。

奈奎斯特频率定义为信号带宽的两倍。

过采样能够提高分辨率和信噪比SNR,并且通过放宽抗混叠滤波器的性能要求,有助于避免混叠和相位失真。

在很多项U应用中,需要测量信号的动态范W较大,且需要参数的微小变化。

例如,ADC需要测量很大的温度范囤(比如工业中其至要求从- 2o(rc~5o (rc),但仍要求系统对小于i度的变化做出响应。

常见的单片机片上ADC位数为12位,如要实现高于12位分辨率要怎么做呢?我们知道奈奎斯特・香农采样定理可知:/» = 2 X /m其中:条:为输入待采样信号最高频率九•为奈奎斯特频率。

如果实际采样频率高于奈奎斯特频率仏即为过采样。

那么低于奈奎斯特采样高的分辨率呢?要知道所采用的ADC®件核分辨率是固定的,难道还会变不成?过采样提高分辨率_____________________________________________________ 如果对一模拟信号,采用过采样,然后再进行一定的软件后处理,理论上是可以得到更高分辨率的:为增加有效位数effective number of bits),对信号进行过采样,所需(ENOB :的过采样率可以曲下面公式确定(省略理论推导,过于枯燥):九=4* X去其中:/加为过采样频率人产品所需实际采样频率W为额外所需增加的分辨率位数假设系统使用12位ADC每100 ms输出一次采样值也即(lOHz)。

为了将测量的分辨率提高到16位,我们按上述公式计算过采样频率:仏=4用X /, = 4^ X 10 = 2560Hz因此,如果我们以fs=2560Hz对信号进行过采样,然后在所需的采样周期内收集足够的样本以对它们进行平均,现在可以将16位输出数据用于16位测量。

学习笔记-过采样原理与应用

学习笔记

过采样原理与应用

1、为什么使用过采样技术?

12 位ADC 并采用过采样和求均值技术即可达到以16位分辨率测量某个参数的目的,而不必使用昂贵的片外16位ADC。

2、优缺点?

优点:过采样和求均值对SNR和测量分辨率的改善。

缺点:增加CPU时间和降低数据吞吐率。

3、应用限制

ADC 噪声近似为白噪声的情况。

如果输入信号在样本之间随机变化,变化幅度与代码规模(1 LSB)接近,并且在两个个相邻代码之间有相等的概率,则噪声可以被当作白噪声处理,白噪声的特点是在整个有用频带内具有一致的功率谱密度,在噪声可以被近似为白噪声的情况下,过采样和求均值可以改善SNR 和提高数据的有效分辨率。

可以用过采样和求均值技术提高性能的例子如下:

不适合的例子如下:

4、应用方程

例如12位ADC希望通过过采样达到16位效果,则采样频率需要提升2(16-12)=256倍,256次采样结果加和然后除以16,即可得到16位的输出结果。

5、参考资料

1.《AN018-用过采样和求均值提高ADC 分辨率》

2.《AN2834-如何在STM32微控制器中获得最佳ADC精度》

STM32采样精度提高.pdf AN018_用过采样和求均值提高ADC分。

ADC的过采样技术

ADC 的过采样技术其实原理很简单, 很容易明白, 怎样实现提高分辨率?假定环境条件: 10位ADC最小分辨电压1LSB 为1mv假定没有噪声引入的时候, ADC采样上的电压真实反映输入的电压, 那么小于1mv的话,如ADC在0.5mv是数据输出为0我们现在用4倍过采样来, 提高1位的分辨率,当我们引入较大幅值的白噪声: 1.2mv振幅(大于1LSB), 并在白噪声的不断变化的情况下, 多次采样, 那么我们得到的结果有真实被测电压白噪声叠加电压叠加后电压ADC输出ADC代表电压0.5mv 1.2mv 1.7mv 1 1mv0.5mv 0.6mv 1.1mv 1 1mv0.5mv -0.6mv -0.1mv 0 0mv0.5mv -1.2mv -0.7mv 0 0mvADC的和为2mv, 那么平均值为: 2mv/4=0.5mv!!! 0.5mv就是我们想要得到的这里请留意, 我们平时做滤波的时候, 也是一样的操作喔! 那么为什么没有提高分辨率?????是因为, 我们做滑动滤波的时候, 把有用的小数部分扔掉了, 因为超出了字长啊, 那么0.5取整后就是0 了, 结果和没有过采样的时候一样是0 ,而过采样的方法时候是需要保留小数部分的, 所以用4个样本的值, 但最后除的不是4, 而是2! 那么就保留了部分小数部分, 而提高了分辨率!从另一角度来说, 变相把ADC的结果放大了2倍(0.5*2=1mv), 并用更长的字长表示新的ADC 值,这时候, 1LSB(ADC输出的位0)就不是表示1mv了, 而是表示0.5mv, 而(ADC输出的位1)才是原来表示1mv的数据位,下面来看看一下数据的变化:ADC值相应位9 8 7 6 5 4 3 2 1 00.5mv测量值0 0 0 0 0 0 0 0 0 0 0mv(10位ADC的分辨率1mv,小于1mv无法分辨,所以输出值为0)叠加白噪声的4次过采样值的和0 0 0 0 0 0 0 0 1 0 2mv滑动平均滤波2mv/4次0 0 0 0 0 0 0 0 0 0 0mv(平均数, 对改善分辨率没作用)过采样插值2mv/2 0 0 0 0 0 0 0 0 0 0 1 2mv/2=0.5mv, 将这个数作为11位ADC值, 那么代表就是0.5mv这里我们提高了1位的ADC分辨率这样说应该就很简单明白了吧, 其实多出来的位上的数据, 是通过统计输入量的分布, 计算出来的,而不是硬件真正分辨率出来的, 引入噪声并大于1LSB, 目的就是要使微小的输入信号叠加到ADC能识别的程度(原ADC最小分辨率).理论来说, 如果ADC速度够快, 可以无限提高ADC的分辨率, 这是概率和统计的结果但是ADC的采样速度限制, 过采样令到最后能被采样的信号频率越来越低,就拿stm32的ADC来说, 12ADC, 过采样带来的提高和局限分辨率采样次数每秒采样次数12ADC 1 1M13ADC 4 250K14ADC 16 62.5K15ADC 64 15.6K16ADC 256 3.9K17DC 1024 97618ADC 4096 24419ADC 16384 6120ADC 65536 15要记住, 这些采样次数, 还未包括我们要做的滑动滤波,看到这些文档, 啰啰嗦嗦说一大堆公式什么的, 忍不住就随便写了些,如果我是做IC的, 我一定要求把文档写到白话文一样, 小学生都能看明白的, 自然小学生都会用, 人多用了, 才有钱赚嘛,都不知道这些芯片厂是怎么推广的, 写一大堆公式有什么用, 这么复杂的芯片都设计了, 写个文档却马马虎虎,其实不管多复杂的公式, 实现起来还不是加减乘除, 废话少说, 有时间再写了......。

过采样技术——精选推荐

过采样技术⽬录1 过采样技术的简介2 过采样技术的作⽤3 过采样技术的应⽤4 过采样技术的软件实现1过采样技术的简介 过采样技术⼀般分三步: 1、⾼速(相对于输⼊信号频谱)采样模拟信号 2、数字过采样低通滤波 3、抽取数字序列。

采⽤这项技术,既保留了输⼊信号的较完整信息,降低了对输⼊信号频谱的要求,⼜可以提⾼采样⼦系统的精度。

2过采样技术的作⽤ 1、过采样降低对模拟抗混叠滤波器的限制 在采样过程中⾸要的问题是采样频率的选择,Nyquist采样定理指出:若连续信号x(t)是有限带宽的,其频谱的最⾼频率为fc,对x(t)采样时,若保证采样频率fs≥2fc,那么,就可由采样信号恢复出x(t)。

在实际对x(t)作采样时,⾸先要了解x(t)的最⾼截⽌频率fc,以确定应选取的采样频率fs。

若x(t)不是有限带宽的,在采样前应使⽤抗混叠(anti-aliasing)滤波器对x(t)作模拟滤波,以去掉f>fc的⾼频成分。

因此,在AD转换前就需要模拟低通滤波器具有尖锐的滚降特性,来限制模拟信号的频谱。

⼀个理想的滤波器应能让所有低于fs/2的频率通过,⽽完全阻隔掉所有⼤于fs/2的频率。

通常,滤波器和采样频率的选择是将我们感兴趣的频带限制在DC和fs/2之间。

2、过采样提⾼信噪⽐ 经模拟滤波后,模拟信号被采样并转换成数字值,因为数字域仅包含有限的字长,若要⽤它来表⽰连续信号,就要引⼊量化误差,最⼤量化误差为±0.5LSB。

因为⼀个N位的ADC的输⼊范围被分成2N个离散的数值,每⼀个数值由⼀个N位的⼆进制数表⽰,所以,ADC的输⼊范围和字长N是最⼤量化误差的⼀个直接表⽰,也是分辨率的⼀个直接表⽰。

代表数字值的字长决定了信噪⽐,因此通过增加信噪⽐可以增加转换的分辨率。

加⼊三⾓波信号可提⾼信噪⽐(详见TI公司的资料:Oversampling Techniques Using theTMS320C24x Family,June 1998)。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

什么叫过采样首先,考虑一个传统ADC的频域传输特性。

输入一个正弦信号,然后以频率fs采样--按照 Nyquist 定理,采样频率至少两倍于输入信号。

从FFT分析结果可以看到,一个单音和一系列频率分布于DC到fs /2间的随机噪声。

这就是所谓的量化噪声,主要是由于有限的ADC分辨率而造成的。

单音信号的幅度和所有频率噪声的RMS幅度之和的比值就是信号噪声比(SNR)。

对于一个Nbit ADC,SNR可由公式:SNR=+得到。

为了改善SNR和更为精确地再现输入信号,对于传统ADC来讲,必须增加位数。

如果将采样频率提高一个过采样系数k,即采样频率为kfs,再来讨论同样的问题。

FFT分析显示噪声基线降低了,SNR值未变,但噪声能量分散到一个更宽的频率范围。

Σ-Δ转换器正是利用了这一原理,具体方法是紧接着1bit ADC之后进行数字滤波。

大部分噪声被数字滤波器滤掉,这样,RMS噪声就降低了,从而一个低分辨率ADC,Σ-Δ转换器也可获得宽动态范围。

那么,简单的过采样和滤波是如何改善SNR的呢一个1bit ADC的SNR为+,每4倍过采样将使SNR增加6dB,SNR每增加6dB等效于分辨率增加1bit。

这样,采用1bit ADC进行64倍过采样就能获得4bit分辨率;而要获得16bit分辨率就必须进行415倍过采样,这是不切实际的。

Σ-Δ转换器采用噪声成形技术消除了这种局限,每4倍过采样系数可增加高于6dB的信噪比。

增加采样频率可以改善系统的SNR,其原因是,当采样频率增加时,量化噪声功率仍保持不变(量化噪声只与字长有关),量化误差可以建模为样本与样本之间不相关,这就将产生平坦的频率响应,从而具有单边功率谱密度:PSD等于两倍的量化噪声功率与采样频率之比。

因此,尽管总的量化噪声功率保持不变,量化噪声的PSD随着采样频率的增加而减低,即,采样频率每增加一倍,信噪比大约增加3分贝。

揭开Σ-ΔADC的神秘面纱技术分类:模拟设计 | 2010-08-06嵌入式公社越来越多的应用,例如过程控制、称重等,都需要高分辨率、高集成度和低价格的ADC。

新型Σ-Δ转换技术恰好可以满足这些要求。

然而,很多设计者对于这种转换技术并不十分了解,因而更愿意选用传统的逐次比较ADC。

Σ-Δ转换器中的模拟部分非常简单(类似于一个1bit ADC),而数字部分要复杂得多,按照功能可划分为数字滤波和抽取单元。

由于更接近于一个数字器件,Σ-ΔADC的制造成本非常低廉。

一、Σ-ΔADC工作原理要理解Σ-ΔADC的工作原理,首先应对以下概念有所了解:过采样、噪声成形、数字滤波和抽取。

1. 过采样首先,考虑一个传统ADC的频域传输特性。

输入一个正弦信号,然后以频率fs采样--按照 Nyquist定理,采样频率至少两倍于输入信号。

从FFT分析结果可以看到,一个单音和一系列频率分布于DC到fs /2间的随机噪声。

这就是所谓的量化噪声,主要是由于有限的ADC分辨率而造成的。

单音信号的幅度和所有频率噪声的RMS幅度之和的比值就是信号噪声比(SNR)。

对于一个Nbit ADC,SNR可由公式:SNR=+得到。

为了改善SNR和更为精确地再现输入信号,对于传统ADC来讲,必须增加位数。

如果将采样频率提高一个过采样系数k,即采样频率为kfs,再来讨论同样的问题。

FFT 分析显示噪声基线降低了,SNR值未变,但噪声能量分散到一个更宽的频率范围。

Σ-Δ转换器正是利用了这一原理,具体方法是紧接着1bit ADC之后进行数字滤波。

大部分噪声被数字滤波器滤掉,这样,RMS噪声就降低了,从而一个低分辨率ADC,Σ-Δ转换器也可获得宽动态范围。

那么,简单的过采样和滤波是如何改善SNR的呢一个1bit ADC的SNR为(+),每4倍过采样将使SNR增加6dB,SNR每增加6dB等效于分辨率增加1bit。

这样,采用1bit ADC 进行64倍过采样就能获得4bit分辨率;而要获得16bit分辨率就必须进行415倍过采样,这是不切实际的。

Σ-Δ转换器采用噪声成形技术消除了这种局限,每4倍过采样系数可增加高于6dB的信噪比。

2. 噪声成形通过图1所示的一阶Σ-Δ调制器的工作原理,可以理解噪声成形的工作机制。

图1 Σ-Δ调制器Σ-Δ调制器包含1个差分放大器、1个积分器、1个比较器以及1个由1bit DAC(1个简单的开关,可以将差分放大器的反相输入接到正或负参考电压)构成的反馈环。

反馈DAC的作用是使积分器的平均输出电压接近于比较器的参考电平。

调制器输出中"1"的密度将正比于输入信号,如果输入电压上升,比较器必须产生更多数量的"1",反之亦然。

积分器用来对误差电压求和,对于输入信号表现为一个低通滤波器,而对于量化噪声则表现为高通滤波。

这样,大部分量化噪声就被推向更高的频段。

和前面的简单过采样相比,总的噪声功率没有改变,但噪声的分布发生了变化。

现在,如果对噪声成形后的Σ-Δ调制器输出进行数字滤波,将有可能移走比简单过采样中更多的噪声。

这种调制器(一阶)在每两倍的过采样率下可提供9dB的SNR改善。

在Σ-Δ调制器中采用更多的积分与求和环节,可以提供更高阶数的量化噪声成形。

例如,一个二阶Σ-Δ调制器在每两倍的过采样率下可改善SNR 15dB。

图2显示了Σ-Δ调制器的阶数、过采样率和能够获得的SNR三者之间的关系。

图2 SNR与过采样率的关系3. 数字滤波和抽取Σ-Δ调制器以采样速率输出1bit数据流,频率可高达MHz量级。

数字滤波和抽取的目的是从该数据流中提取出有用的信息,并将数据速率降低到可用的水平。

Σ-ΔADC中的数字滤波器对1bit数据流求平均,移去带外量化噪声并改善ADC的分辨率。

数字滤波器决定了信号带宽、建立时间和阻带抑制。

Σ-Δ转换器中广泛采用的滤波器拓扑是SINC3,一种具有低通特性的滤波器。

这种滤波器的一个主要优点是具有陷波特性,可以将陷波点设在和电力线相同的频率,抑制其干扰。

陷波点直接相关于输出数据速率(转换时间的倒数)。

SINC3滤波器的建立时间三倍于转换时间。

例如,陷波点设在60Hz时(60Hz数据速率),建立时间为3/60Hz=50ms。

有些应用要求更快的建立时间,而对分辨率的要求较低。

对于这些应用,新型ADC诸如MAX1400系列允许用户选择滤波器类型SINC1或SINC3。

SINC1滤波器的建立时间只有一个数据周期,对于前面的举例则为1/60Hz=。

由于带宽被输出数字滤波器降低,输出数据速率可低于原始采样速率,但仍满足Nyquist定律。

这可通过保留某些采样而丢弃其余采样来实现,这个过程就是所谓的按M因子"抽取"。

M因子为抽取比例,可以是任何整数值。

在选择抽取因子时应该使输出数据速率高于两倍的信号带宽。

这样,如果以fs的频率对输入信号采样,滤波后的输出数据速率可降低至fs /M,而不会丢失任何信息。

二、MAXIM的新型Σ-ΔADC新型高集成度Σ-ΔADC正在得到越来越广泛的应用,这种ADC只需极少外接元件就可直接处理微弱信号。

MAX1402便是这种新一代ADC的一个范例,大多数信号处理功能已被集成于芯片内部,可视为一个片上系统,如图3所示。

该器件在480sps工作速率下可提供16bit 精度,4800sps时精度达12bit,工作模式下仅消耗250μA的电流,掉电模式仅消耗2μA。

信号通道包含一个灵活的输入多路复用器,可被设置为3路全差分信号或5路伪差分信号、2个斩波放大器,1个可编程PGA(增益从1"128)、1个用于消除系统偏移的粗调DAC和1个二阶Σ-Δ调制器。

调制器产生的1bit数据流被送往一个集成的数字滤波器进行精处理(配置为SINC1或SINC3)。

转换结果可通过SPITM/QSPITM兼容的三线串行接口读取。

另外,该芯片还包含有2个全差分输入通道,用于系统校准(失调和增益);2个匹配的200μA电流源,用于传感器激励(例如可用于3线/4线RTD);2个"泵出"电流,用于检测选定传感器的完整性。

通过串行接口访问器件内部的8个片内寄存器,可对器件的工作模式进行编程。

输入通道可以在外部命令的控制下进行采样或者连续采样,通过SCAN控制位设定,转换结果中附加有3bit"通道标识"位,用来确定输入通道。

图3 MAX1402原理框图两个附加的校准通道CALOFF和CALGAIN可用来校准测量系统。

此时可将CALOFF输入连接到地,将CALGAIN输入连接到参考电压。

对上述通道的测量结果求取平均后可用来对测量结果进行校准。

三、Σ-ΔADC的应用1. 热电偶测量及冷端补偿如图4所示,在本应用中,MAX1402工作在缓冲方式,以便允许在前端采用比较大的去耦电容(用来消除热电偶引线拾取的噪声)。

为适应输入缓冲器的共模范围,采用参考电压对AIN2输入加以偏置。

在使用热电偶测温时,要获得精确的测量结果,必须进行冷端补偿。

热电偶输出电压可表示为V=α(t1-tref)其中α是与热电偶材料有关的Seebeck常数,t1是待测温度,tref是接线盒处的温度。

为了对tref造成的误差进行补偿,可以在热电偶输出端采用二极管补偿;也可以测出接线盒处的温度,然后用软件进行补偿。

在本例中,差分输入通道AIN3、AIN4被用来测量P-N 结的温度(用内部200μA电流源加以偏置)。

图4 热电偶测量及冷端补偿线和4线RTD测量铂电阻温度传感器(RTD)被许多需要测量温度的应用所优选,因为它们具有优异的精度和互换性。

一个在0℃时具有100Ω电阻的RTD,到+266℃时电阻会达到200Ω,灵敏度非常低,约为ΔR/Δt=100Ω/266℃。

200μA的激励电流在0℃时可产生20mV输出,+266℃时输出40mV。

MAX1402可直接处理这种低电平的信号。

根据不同应用,引线电阻对于测量精度会产生不同程度的影响。

一般来讲,如果RTD靠近转换器,采用最简单的两线结构即可;而当RTD比较远时,引线电阻会叠加入RTD阻抗,并给测量结果引入显著误差。

这种情况通常采用3线或4线RTD配置,如图5所示。

图5 3线和4线RTD测量MAX1402内部两个匹配的200μA电流源可用来补偿3线或4线RTD配置中引线电阻造成的误差。

在3线配置中,两个匹配的200μA电流源分别流过RL1和RL2,这样,AIN1和AIN2端的差分电压将不受引线电阻的影响。

这种补偿方法成立的前提是两条引线材质相同,并具有相同的长度,还要求两个电流源的温度系数精确匹配(MAX1402为5×10-6/℃)。

4线配置中引线电阻将不会引入任何误差,因为在连接到AIN1和AIN2的测量引线中基本上没有电流流过。