2006031459黄德荣5位逐级进位和超前进位加法器设计剖析

超前进位加法器

超前进位加法器超前进位加法器是一种数字电路设备,用于进行二进制数的加法运算。

它通过将多个加法器级联,实现对多位二进制数的加法计算,并且能够在加法过程中实现超前进位,提高计算速度。

超前进位加法器的原理是基于二进制加法的原理。

在二进制加法中,每一位的运算结果可以表示为:两个位的和与进位。

其中,和即为输入位的异或运算结果,进位则是输入位的与运算结果再经过左移一位。

超前进位加法器利用这一原理,通过预测进位产生的结果,以提前得到进位并作用于下一级的运算。

超前进位加法器可以分为两个部分:生成进位部分和传递进位部分。

生成进位部分用于预测进位的产生情况,传递进位部分则是将进位传递给下一级的加法器。

生成进位部分的输入为两个相邻位的和,输出为进位。

传递进位部分的输入为前一级的进位以及生成进位部分的进位,输出为当前位的进位。

为了方便理解,以下以一个四位超前进位加法器为例进行介绍。

这个四位加法器由四个单独的全加器组成,每个全加器负责一个位的运算。

生成进位部分和传递进位部分在全加器中都有相应的电路实现。

首先,生成进位部分。

对于第一位的全加器来说,由于没有前一位的进位,因此直接将两个输入位的和作为输出位的进位。

对于其他位的全加器,需要预测进位的产生。

这个预测的规则是,如果前一位的和为1,则有可能会产生进位。

因此,预测进位部分将前一位输入位的和与该位输入位的和进行与运算,得到预测的进位结果。

接下来,传递进位部分。

对于第一个全加器来说,由于没有前一位的进位,因此直接将生成进位部分的进位作为输出位的进位。

对于其他位的全加器,传递进位部分将前一位的进位与生成进位部分的进位进行或运算,得到当前位的进位。

将多个全加器级联后,就构成了一个超前进位加法器。

通过这种方式,每一位的运算可以并行进行,从而提高了计算速度。

同时,由于提前预测了进位的结果,可以减少了进位的传播延迟,进一步提高了计算效率。

超前进位加法器在数字电路的设计中具有重要的应用价值。

数字逻辑 第三章 加法器.ppt

四位二进制并行加法器

三、四位二进制并加法器的外部特性和逻辑符号 1.外部特性

图中,A4、A3、A2、A1 ------- 二进制被加数; B4、B3、 B2、B1 ------- 二进制加数; F4、 F3、 F2、 F1 ------相加产生的和数; C0 --------------------来自低位的进位输入; FC4 -------------------向高位的进位输出。

a3b1

+) 乘积 Z5 a3b2 Z4 a2b2 Z3

a2b1

a1b2 Z2

a1b1

Z1

因为: ☆1位二进制数乘法 法则和逻辑“与”运算法 则相同,“积”项aibj(i =1,2,3;j=1,2)可用 两输入与门实现。 ☆对部分积求和可用 并行加法器实现。 所以:该乘法运算电 路可由6个两输入与门和1 b2 个4位二进制并行加法器构 成。逻辑电路图如右图所 示。

四位二进制并行加法器

实现给定功能的逻辑电路图如下图所示。 1) 输入端A4、A3、A2、 A1输入8421码;

2) 而从另一输入端B4、 B3、B2、B1输入二进 制数0011; 3) 进位输入端C0接上“0”;

4) 可从输出端F4、F3、F2、 F1得到与输入8421码对

应的余3码。

四位二进制并行加法器

Z5 Z4 Z3 Z 2 Z1

F4 F3 F2 F 1 FC4 T 693 C0

0

A4 A3 A2 A1

B4 B 3 B2 B1

&

&

&

&

&

&

b1

a3

a2

a1 0 a 3

a2

a1

FA4

F3 C3

FA3

F2

超前进位加法器的设计

沈阳航空工业学院课程设计报告课程设计名称:计算机组成原理课程设计课程设计题目:超前进位加法器的设计院(系):计算机学院专业:计算机科学与技术班级:4401102学号:200403011046姓名:郭丰瑞指导教师:刘泽显完成日期:2006年12月31日沈阳航空工业学院课程设计报告目录第1章总体设计方案 (1)1.1设计原理 (1)1.2设计思路 (2)1.3设计环境 (3)第2章详细设计方案 (4)2.1顶层方案图的设计与实现 (4)2.1.1创建顶层图形设计文件 (4)2.1.2器件的选择与引脚锁定 (4)2.2功能模块的设计与实现 (6)2.2十六位超前进位加法器的设计 (6)2.3仿真调试 (8)第3章编程下载与硬件测试 (12)3.1编程下载 (12)3.2硬件测试及结果分析 (12)参考文献 (15)附录(程序清单或电路原理图) (16)第1章总体设计方案1.1设计原理十六位超前进位加法器,可以由4个四位超前进位加法器构成。

由第一个四位超前进位加法器的进位输出加进为第二个超前进位加法器的进位输入,依次类推。

超前进位加法器的实现是建立在各位进位的形成条件来实现的。

所以第一位的进位c1=a0*b0+(a0+b0)*c0;第二位的进位c2=a1*b1+(a1+b1)*a0*b0+(a1+b1)(a0+b0)c0第三位的进位c3=a2*b2+(a2+b2)a1*b1+(a1+b1)*(a2+b2)*a0*b0+(a0+b0)(a1+b1)(a2+b2)*c0第四位的进位c4=a3*b3+(a3+b3)*a2*b2+(a3+b3)*(a2+b2)a1*b1+(a3+b3)(a2+b2)(a1+b1)*a0*b0+(a0+b0)(a1+b1)(a2+b2)(a3+b3)*c0 下面我们可以引进传递函数Pi和进位产生函数Gi的概念。

他们定义为:Pi=Ai+BiGi=Ai*BiP1的意义是:当A0和B0中有一个为1时,若有进位输入,则本位向高位传递进位。

超前进位加法器原理

F=A 加 B 加 1

F=(A+B )加 AB

F=(AB+ )加 AB 加 1

F=AB 减 1

F=AB

F=A 加 A

F=A 加 A 加 1

F=(A+B)加 A

F=(A+B)加 A 加 1

F=(A+B )加 A

F=(AB+ )加 A 加 1

F=A 减 1

F=A

P

1

1

&

G

&&

Cnz

1 & &&

Cn y

1 &&

自学

Cnx

1 &

P3 G3

P2 G2

P1 G1

图2.28 74182型超前进位扩展器逻辑图

P0 G0 Cn

C1 Cn PG

Cn PG

Cn PG

74181

Cn Cn4 PG

Cn PG

Cn PG

Cn PG

Cn Cn4 PG

P0 G0 Cn x P1 G1 Cn y P2 G2 Cn z P3G3

自学

累加器

数据输入 AB

组合电路

累加寄存器

求和命令 (时钟)

数据输入 AB

ALU(74181)

控制变量 (S3,S2,S1,S0,M)

累加寄存器

求和命令 (时钟)

数据输出

图2.30累加器结构图

数据输出

图2.31用ALU构成的累加器

Cn

74182

PG

P0 G0 Cn x P1 G1 Cn y P2 G2 Cn z P3G3

Cn

74182

PG

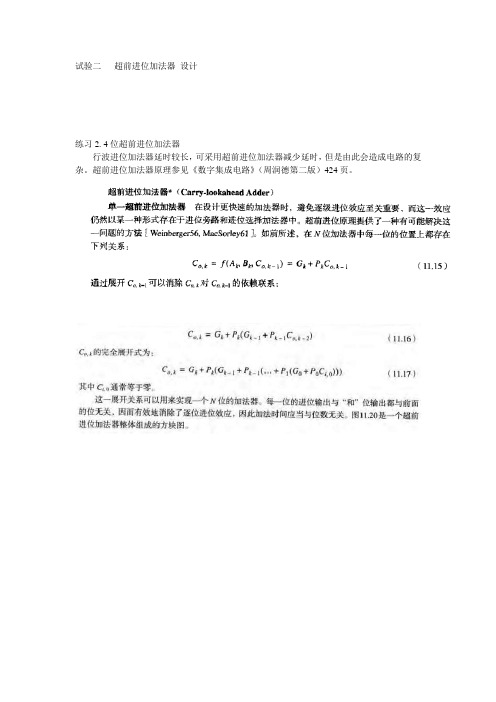

试验二 超前进位加法器 设计

试验二超前进位加法器设计练习2. 4位超前进位加法器行波进位加法器延时较长,可采用超前进位加法器减少延时,但是由此会造成电路的复杂。

超前进位加法器原理参见《数字集成电路》(周润德第二版)424页。

对以上公式的注解:公式中的C O,K 表示第K 为的进位输出,G K 为第K 位的进位产生,P K 为第K 为的进位传播。

且:K K KK K KG A B P A B ==⊕ A K ,B K 为输入加数的第K 位。

将Co 和S 用G,P 重写为: O ii C G PC S P C =+=⊕由于低位的输出进位是高位的输入进位,所以有上面的(11.15)式源程序://this is a carry lookahead of 4bitmodule clad(ina,inb,ci,co,sum);input[3:0] ina,inb;input ci;output co;output[3:0]sum;wire co0,co1,co2,G0,G1,G2,G3,P0,P1,P2,P3;assignG0=ina[0]&inb[0],P0=ina[0]^inb[0],G1=ina[1]&inb[1],P1=ina[1]^inb[1],G2=ina[2]&inb[2],P2=ina[2]^inb[2],G3=ina[3]&inb[3],P3=ina[3]^inb[3],co0=G0|(P0&ci),co1=G1|(P1&co0),co2=G2|(P2&co1),co=G3|(P3&co2),sum[0]=P0^ci,sum[1]=P1^co0,sum[2]=P2^co1,sum[3]=P3^co2;endmodule测试程序:module clad_test;reg[3:0] ina,inb;reg ci;wire co;wire[3:0]sum;clad CI(.ina(ina),.inb(inb),.ci(ci),.co(co),.sum(sum)); initialbeginina=0;inb=0;ci=0;endalways #5 ina=ina+1'b1;always #80 inb=inb+1'b1;always #1280 ci=~ci;endmodule仿真结果:注:该结果为10进制显示练练手:参考《数字集成电路》(周润德第二版)420-421,设计一个16位的超前进位加法器,基本单元使用4位的加法器,结构自选。

先行进位加法器

先⾏进位加法器实验四32位先⾏进位加法器⼀、功能概述串⾏进位加法器延时很⼤,每级的输出结果都要等上⼀级的进位到来才可以求和算出结果,这次实验对普通全加器进⾏改良,改良为先⾏进位加法器。

先⾏进位加法器,各级的进位彼此是独⽴产⽣,只与输⼊数据A,B和C_in有关,将各级间的进位级联传播给去掉了,这样就可以减⼩进位产⽣的延时。

每个等式与只有三级延迟的电路对应,第⼀级延迟对应进位产⽣信号和进位传递信号,后两级延迟对应上⾯的积之和。

通过这种进位⽅式实现的加法器称为超前进位加法器。

因为各个进位是并⾏产⽣的,所以是⼀种并⾏进位加法器。

⼆、实验原理1、设⼆进制加法器第i位为A i,B i,输出为S i,进位输⼊为C i,进位输出为C i+1,则有:S i=A i⊕B i⊕C i(1-1)C i+1 =A i * B i+ A i *C i+ B i*C i =A i * B i+(A i+B i)* C i(1-2)令G i = A i * B i , P i = A i+B i,则C i+1= G i+ P i *C i当A i和B i都为1时,G i = 1,产⽣进位C i+1 = 1当A i和B i有⼀个为1时,P i = 1,传递进位C i+1= C i因此G i定义为进位产⽣信号,P i定义为进位传递信号。

G i的优先级⽐P i⾼,也就是说:当G i = 1时(当然此时也有P i = 1),⽆条件产⽣进位,⽽不管C i是多少;当G i=0⽽P i=1时,进位输出为C i,跟C i之前的逻辑有关。

下⾯推导4位超前进位加法器。

设4位加数和被加数为A 和B,进位输⼊为C in,进位输出为C out,对于第i位的进位产⽣G i = A i·B i ,进位传递P i=A i+B i , i=0,1,2,3。

于是这各级进位输出,递归的展开Ci,有:C0 = C inC1=G0 + P0·C0C2=G1 + P1·C1 = G1 + P1·G0 + P1·P0?C0C3=G2+ P2·C2= G2+ P2·G1+ P2·P1·G0+P2·P1·P0·C0C4=G3+ P3·C3= G3+ P3·G2+ P3·P2·G1+P3·P2·P1·G0 + P3·P2·P1·P0·C0 (1-3)C out=C4由此可以看出,各级的进位彼此独⽴产⽣,只与输⼊数据Ai、Bi和Cin有关。

超前进位加法器的设计分解

超前进位加法器的设计分解沈阳航空航天大学课程设计报告课程设计名称:计算机组成原理课程设计课程设计题目:超前进位加法器的设计院(系):计算机学院专业:计算机科学与技术班级:学号:姓名:指导教师:完成日期:2014年01月10日第2章详细设计方案2.1 顶层方案图的设计与实现顶层方案图主要实现一位全加器的逻辑功能,采用原理图设计输入方式完成,超前进位加法器电路的是实现基于XCV200可编程逻辑芯片。

在完成原理图的功能设计后,经过检测调试,把输入/输出信号通过引脚编号安排到XCV200指定的引脚上去,最终实现芯片的引脚锁定。

2.1.1顶层方案的整体设计顶层图形文件主要由2个四位超前进位加法器构成,总共17位输入,9位输出。

顶层图形文件由Xilinx Foundation F3.1软件编辑得到相应的模块,顶层图形的整体设计如下图2.1所示:图 2.1八位超前进位加法器整体设计图2.1.2元器件选择和引脚锁定(1)元器件的选择由于在设计的过程中,硬件设计环境是基于伟福COP2000型计算机组成原理实验仪和XCV200实验板,故采用的目标芯片为Xilinx XCV200可编程逻辑芯片。

(2)引脚锁定在Xilinx Foundation F3.1上面完成软件的设计之后,把顶层图形文件中的输入/输出信号用引脚编号安排到Xilinx XCV200芯片指定的引脚上去,从而实现芯片的设计电路的引脚锁定,各信号及Xilinx XCV200芯片引脚对应关系如下表2.1所示:表 2.1 信号和芯片引脚对应关2.2 功能模块的设计与实现在八位超前进位加法器和四位超前进位加法器的设计中均是采用Schematic 设计输入方式,而在四位超前进位加法器的设计中是由一列的门电路构成,最后在由2个四位超前进位加法器模块构成8位超前进位加法器。

可以扩展开来,16位,32位超前进位加法器原理类似8位的设计原理。

2.2.1 八位超前进位加法器的设计与实现(1)设计描述根据上面在1.1中讲述的四位超前进位加法器的设计原理那样,四位超前进位加法器的实现是建立在进位C1,C2,C3,C4的基础之上的。

数字集成电路课程设计报告-4bits超前进位加法器

数字集成电路课程设计报告-4bits超前进位加法器福州⼤学⾄诚学院数字集成电路课程设计报告设计题⽬:4bits 超前进位加法器班级:专业:姓名:学号:组名:指导⽼师:教师评分:⽇期:4bits超前进位加法器⽬录第1章概述.................................................................... - 3 -1.1课程设计⽬的 (3)1.2课程设计的主要内容 (3)1.2.1设计题⽬ (3)1.2.2设计内容 (3)第2章功能分析及逻辑分析...................................................... - 3 -2.1功能分析 (3)2.2推荐⼯作条件 (4)2.3电性能 (4)2.4交流(开关)特性 (5)2.5真值表 (6)2.6表达式 (6)2.7电路图 (7)第3章电路设计及器件参数设计.................................................. - 7 -3.1性能指标: (7)3.2模块划分 (7)3.2.1输出级电路设计 (7)3.2.2内部反相器 (8)3.2.3内部电路等效 (8)3.2.4输⼊级电路 (9)3.2.5中间缓冲级电路 (9)3.2.6输出缓冲级电路 (9)3.2.7输⼊、输出保护电路 (10)3.3本章⼩结 (10)第4章功耗估算与延时......................................................... - 10 -4.1电容估算 (10)4.2功耗估算 (11)4.3延时估算 (11)4.4本章⼩结 (12)第5章电路模拟与仿真......................................................... - 12 -5.1电路搭建 (12)5.1.1建⽴新库 (12)5.1.2建⽴SCHEMATIC VIEW (13)5.1.3建⽴SYMBOL (13)5.1.4建⽴总体电路SCHEMATIC VIEW (13)数字集成电路课程设计5.1.5建⽴总体SYMBOL (14)5.1.6测试电路 (14)5.2功能仿真 (15)5.3功耗仿真 (15)5.4仿真结果分析 (16)5.5本章⼩结 (16)第6章版图设计............................................................... - 16 -6.1原理 (16)6.2反相器版图 (17)6.2.1 LAYOUT VIEW的建⽴ (17)6.2.2添加器件 (18)6.2.3互连,实现反相器功能 (18)6.3输⼊级 (19)6.4输出级 (19)6.5输出缓冲 (19)6.6异或门 (20)6.7或⾮门 (20)6.8与门 (20)6.9整体版图 (21)6.10本章⼩结 (21)总体⼼得....................................................................... - 22 -对课程内容的建议................................................... 错误!未定义书签。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

s: out std_logic_vector(4 downto 0); cout:out std_logic); end adder; architecture Behavioral of adder is signal c:std_logic_vector(4 downto 0); begin c(0)<=cin; s(0)<=a(0) xor b(0) xor c(0); c(1)<=(a(0)and b(0))or (a(0)and c(0))or (b(0)and c(0)); s(1)<=a(1) xor b(1) xor c(1); c(2)<=(a(1)and b(1))or (a(1)and c(1))or (b(1)and c(1)); s(2)<=a(2) xor b(2) xor c(2); c(3)<=(a(2)and b(2))or (a(2)and c(2))or (b(2)and c(2)); s(3)<=a(3) xor b(3) xor c(3); c(4)<=(a(3)and b(3))or (a(3)and c(3))or (b(3)and c(3)); s(4)<=a(4) xor b(4) xor c(4); cout<=(a(4)and b(4))or (a(4)and c(4))or (b(4)and c(4));

VHDL 代码

--------------------------------------------------------------------------------- Company: -- Engineer: --- Create Date: 02:59:18 10/22/08 -- Design Name: -- Module Name: adder - Behavioral -- Project Name: -- Target Device: -- Tool versions: -- Description: --- Dependencies: --- Revision: -- Revision 0.01 - File Created -- Additional Comments: --------------------------------------------------------------------------------library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; ---- Uncomment the following library declaration if instantiating ---- any Xilinx primitives in this code. --library UNISIM; --use UNISIM.VComponents.all; entity adder is port(a,b:in std_logic_vector(4 downto 0); cin:in std_logic;

深 圳 大 学 实 验 报 告

课程名称:

VHDL 数字电路设计教程

实验项目名称:

5 位逐级进位和超前进位加法器设计

学院:

信息工程学院

专业:

电子信息工程

指导教师:

梁松海

报告人:黄德荣

学号:20006031459 班级:

1班ቤተ መጻሕፍቲ ባይዱ

实验时间:

2008.10.22

实验报告提交时间:

2008.11.5

教务处制

实验目的与要求:

用 XILINX ISE 7.1i 实现逐级进位和超前进位加法器

方法、步骤: 1,逐级进位加法器

对每一位都使用了全加器 FAU,图中 a 和 b 是输入位,cin 是进位输入位。S 是求和 的结果,cout 是进位输出位。C 是进位矢量。图中每个全加器的输出结果都依赖于前一 级产生的进位。由全加器的特性,可以写出如下的逻辑表达式: S=a XOR b XOR cin cout=(a ANDb)OR(aAND cin)OR(b AND cin) 2,超前进位加法器

电路实现是需要两个非常重要的中间信号:generate 和 propagate,分别由 g 和 p 表 示。加法器两个输入位是 a 和 b,则 generate 和 propagate 信号定义如下: g=a AND b p=a XOR b 这两个信号与进位无关,只根据当前的输入计算。 现在两个输入矢量是: a=a(4)a(3)a(2)a(1)a(0) 和 b=b(4)b(3)b(2)b(1)b(0), 那么相应的 generate 矢量为 g=g(4)g(3)g(2)g(1)g(0),相应的 propagate 矢量为 p=p(4)p(3)p(2)p(1)p(0)。 其中: g(j)=a (j) AND b(j) p(j)=a (j)XOR b(j) 同时,进位矢量用 c=c(4)c(3)c(2)c(1)c(0)。进位可由 g 和 p 按照下面的方法计算得 到: c(0) = cin; c(1) = c(0)p(0))+g(0);

c(2) = c(0)p(0)p(1))+g(0)p(1)+g(1); c(3) = c(0)p(0)p(1) p(2)+g(0)p(1)p(2)+(g(1) p(2)+g(2); c(4) = c(0)p(0) p(1) p(2) p(3)+g(0) p(1) p(2) p(3)+g(1) p(2) p(3)+g(2) p(3)+g(3); c(5) =c(0)p(0) p(1) p(2) p(3) p(4)+g(0) p(1) p(2)p(3) p(4)+g(1) p(2) p(3) p(4)+g(2) p(3) p(4)+g(4); 可见超前进位加法器的每个全加器不依赖与前一级进位输出的计算结果,有利于 提高电路执行速度。 实验过程及内容: 1, 逐级进位加法器