四位超前进位加法器

超前进位加法器

超前进位加法器超前进位加法器是一种数字电路设备,用于进行二进制数的加法运算。

它通过将多个加法器级联,实现对多位二进制数的加法计算,并且能够在加法过程中实现超前进位,提高计算速度。

超前进位加法器的原理是基于二进制加法的原理。

在二进制加法中,每一位的运算结果可以表示为:两个位的和与进位。

其中,和即为输入位的异或运算结果,进位则是输入位的与运算结果再经过左移一位。

超前进位加法器利用这一原理,通过预测进位产生的结果,以提前得到进位并作用于下一级的运算。

超前进位加法器可以分为两个部分:生成进位部分和传递进位部分。

生成进位部分用于预测进位的产生情况,传递进位部分则是将进位传递给下一级的加法器。

生成进位部分的输入为两个相邻位的和,输出为进位。

传递进位部分的输入为前一级的进位以及生成进位部分的进位,输出为当前位的进位。

为了方便理解,以下以一个四位超前进位加法器为例进行介绍。

这个四位加法器由四个单独的全加器组成,每个全加器负责一个位的运算。

生成进位部分和传递进位部分在全加器中都有相应的电路实现。

首先,生成进位部分。

对于第一位的全加器来说,由于没有前一位的进位,因此直接将两个输入位的和作为输出位的进位。

对于其他位的全加器,需要预测进位的产生。

这个预测的规则是,如果前一位的和为1,则有可能会产生进位。

因此,预测进位部分将前一位输入位的和与该位输入位的和进行与运算,得到预测的进位结果。

接下来,传递进位部分。

对于第一个全加器来说,由于没有前一位的进位,因此直接将生成进位部分的进位作为输出位的进位。

对于其他位的全加器,传递进位部分将前一位的进位与生成进位部分的进位进行或运算,得到当前位的进位。

将多个全加器级联后,就构成了一个超前进位加法器。

通过这种方式,每一位的运算可以并行进行,从而提高了计算速度。

同时,由于提前预测了进位的结果,可以减少了进位的传播延迟,进一步提高了计算效率。

超前进位加法器在数字电路的设计中具有重要的应用价值。

4bits超前加法进位器的全定制设计_微电子卓越班数字集成电路课程设计报告

数字集成电路课程设计题目:4 bits超前加法进位器地全定制设计姓名:席高照学号: 111000833学院:物理与信息工程学院专业:微电子(卓越班)年级: 2010级指导教师:陈群超(签名)2013 年 6 月 3 日目录第1章概述 01.1课程设计目地.......................................... 错误!未定义书签。

1.2课程设计地主要内容.................................... 错误!未定义书签。

1.2.1设计题目.......................................... 错误!未定义书签。

1.2.2设计内容.......................................... 错误!未定义书签。

第2章功能分析及逻辑分析 (2)2.1功能分析 (2)2.2推荐工作条件 (3)2.3电性能 (7)2.4真值表 ................................................ 错误!未定义书签。

2.5表达式 (6)2.6电路图...................................................................... 错误!未定义书签。

第3章电路设计与器件参数设计83.1性能指标: ............................................ 错误!未定义书签。

3.2模块划分 (7)3.2.1输出级电路设计 (7)3.2.2内部反相器 (9)3.2.3内部电路等效 (8)3.2.4输入级电路 (10)3.2.5输出缓冲级电路 (10)3.2.6输入、输出保护电路 (10)3.3本章小结 (10)第4章电路模拟与仿真................................................................................................... 错误!未定义书签。

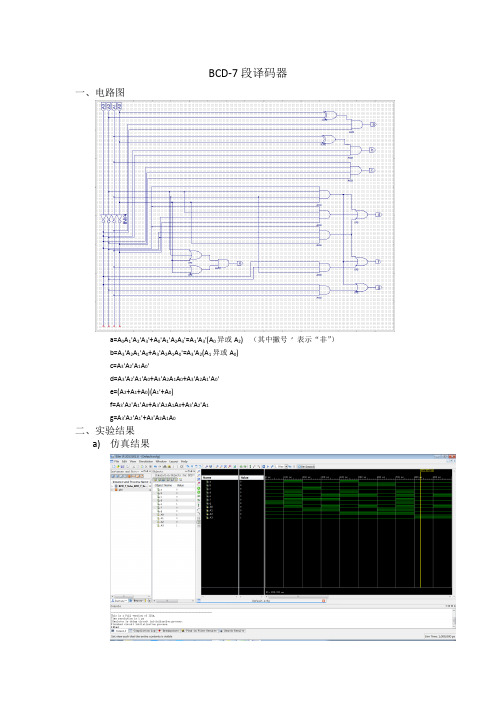

BCD-7段译码器、四位超前进位加法器、四位数值比较器

BCD-7段译码器一、电路图a=A0A1'A2'A3'+A0'A1'A2A3'=A1'A3'(A0异或A2) (其中撇号’表示“非”)b=A3'A2A1'A0+A3'A2A1A0'=A3'A2(A1异或A0)c=A3'A2'A1A0'd=A3'A2'A1'A0+A3'A2A1A0+A3'A2A1'A0'e=(A2+A1+A0)(A1'+A0)f=A3'A2'A1'A0+A3'A2A1A0+A3'A2'A1g=A3'A2'A1'+A3'A2A1A0二、实验结果a)仿真结果{A3,A2,A1,A0}取遍0000,0001,0010,0011,0100,0101,0110,0111,1000,1001,结果均符合要求。

b)在实际FPGA中实验结果:符合要求。

三、结果分析a)输入值范围在0000-1001之间时,可以实现BCD码转7段显示码功能。

但在输入值超出范围时将显示乱码。

若不允许乱码出现,可将卡诺图中的不确定性项d全部改为需要的值,以提示输入错误或不显示任何内容。

但这将使电路规模大幅增加。

b)关键路径含3级门。

其中a,b使用了异或门,但异或门的输入均为原变量。

通过异或门的路径最多只需通过2级逻辑门。

若全部改用与门、或门,则必须有反变量输入,使a,b的关键路径仍然含有3级门,因此不能提升速度,但每个函数必需的带宽都将从4增加为8。

如果与门、或门过剩,异或门不足,且带宽不是制造过程中的制约因素,则更适宜使用与门、或门。

由以上可知,使用异或门可以避免反变量输入,节约1级非门的相应时间,节约带宽。

d函数在卡诺图的分布导致其无法很好化简,因此将占用较多带宽。

用Verilog HDL语言编写的四位超前进位加法器

——Verilog HDL语言

四位超前进位加法器的进位是并 行同时产生的,能够极大的减 少加法器由进位引起的延时。 增加了逻辑器件,但有效的减 少的延迟。进位是由ALU部件超 前算出,本位是由四个不含进 位的加法器算出。

Verilog HDL代码如下: module jiafaqi_4(x,y,c0,c4,f); //四位超前进位加法器 input [4:1]x; //四位x值 input [4:1]y; //四位y值 output [4:1]f; //四位加和f input c0; //上一的级进位 output c4; //向下一级的进位 wire [3:1]c; //超前进位 wire [4:1]p; wire [4:1]g; wire [4:1]cd; assign p=x|y; assign g=x&y;

module jiafaqi_1(x,y,c0,f); //一位加法器模块 input x; input y; input c0; output f; assign f=(x^y)^c0; endmodule //该一位加法器只有本位输出,不含向下一级 的进位输出,进位输出是由顶层模块的并 行超前进位提供

// 在BASYS2开发板上的管脚配置 NET "c4" LOC = N5; NET "c0" LOC = A7; NET "x[1]" LOC = P11; NET "x[2]" LOC = L3; NET "x[3]" LOC = K3; NET "x[4]" LOC = B4; NET "y[1]" LOC = G3; NET "y[2]" LOC = F3; NET "y[3]" LOC = E2; NET "y[4]" LOC = N3; NET "f[1]" LOC = M5; NET "f[2]" LOC = M11; NET "f[3]" LOC = P7; NET "f[4]" LOC = P6;

设计一个 4 位超前进位加法器(数字逻辑课设)

c[2]=(p[2]&p[1]&p[0]&ci)|(p[2]&p[1]&g[0])|(p[2]&g[1])|g[2],

c[3]=(p[3]&p[2]&p[1]&p[0]&ci)|(p[3]&p[2]&p[1]&g[0])|(p[3]&p[2]&g[1])|(p[3]&g[2])|g[3];

代码如下: add.v

`timescale 1ns/1ps

module add(input [3:0]a,input [3:0]b,input ci,output [3:0]s,output co); //定义所需变量

wire [3:0] p, g; //进位传递函数p,进位产生函数g

wire [3:0] c; //进位函数

设计要求:在这个设计中,你需要使用 Verilog 代码设计一个 4 位的超前进位加法器。这个 4 位超前进位加法器可以完成对两个 4 位二进制数的相加。完成设计后,你还需要设计测试程序(test bench)来验证你的设计。你的测试程序需要考虑到所有可能的输入情况。

设计思路:

因为各进位的产生依赖于低位的进位,所以运算速度较慢。为了提高速度,必须设法使较低位的进位信号越过中间各级直接决定较高位的进位输出,设计Ai和Bi分别表示第i位的被加数和加 数,Ci-1为来自第i-1位全加器的进位,令Pi=Ai^Bi,Gi=Ai&Bi函数表达式为:

Co=PoCo+Go

C1=P1Co+G1

C2=p2C1+G2

4bits超前加法进位器的全定制设计微电子卓越班数字集成电路课程设计报告

数字集成电路课程设计题目:4 bits超前加法进位器的全定制设计姓名:席高照学号:111000833学院:物理与信息工程学院专业:微电子(卓越班)年级:2010级指导教师:群超(签名)2013 年 6 月 3 日目录第1章概述 (1)1.1课程设计目的 (1)1.2课程设计的主要容 (1)1.2.1设计题目 (1)1.2.2设计容 (1)第2章功能分析及逻辑分析 (2)2.1功能分析 (2)2.2推荐工作条件 (3)2.3电性能 (3)2.4真值表 (6)2.5表达式 (6)2.6电路图 (7)第3章电路设计与器件参数设计 (8)3.1性能指标: (8)3.2模块划分 (8)3.2.1输出级电路设计 (8)3.2.2部反相器 (9)3.2.3部电路等效 (9)3.2.4输入级电路 (10)3.2.5输出缓冲级电路 (10)3.2.6输入、输出保护电路 (10)3.3本章小结 (11)第4章电路模拟与仿真 (12)4.1电路搭建 (12)4.1.1建立新库 (12)4.1.2建立SCHEMATIC VIEW (13)4.1.3建立SYMBOL (14)4.1.4建立总体电路SCHEMATIC VIEW (14)4.1.5建立总体SYMBOL (15)4.1.6测试电路 (16)4.2功能仿真 (16)4.3功耗仿真 (18)4.4仿真结果分析 (18)4.5本章小结 (18)5.2反相器版图 (19)5.3输入级 (20)5.4输出级 (20)5.5输出缓冲 (20)5.6异或门 (21)5.7或非门 (23)5.8与非门 (24)5.9整体版图 (25)5.10本章小结 (25)心得 (26)参考文献 (27)附录 (28)附录174LS283中文资料 (28)第1章概述1.1 课程设计目的•综合应用已掌握的知识•熟悉集成电路设计流程•熟悉集成电路设计主流工具•强化学生的实际动手能力•培养学生的工程意识和系统观念•培养学生的团队协作能力1.2 课程设计的主要容1.2.1 设计题目4bits超前进位加法器全定制设计1.2.2 设计要求Vdd=1.8V,VoH=4.6V,Vol=0.4V可驱动10个LSTTL电路(相对于15pf电容负载)1.2.3 设计容•功能分析及逻辑分析•电路设计及器件参数设计•估算功耗与延时•电路模拟与仿真•版图设计•版图数据提交及考核,课程设计总结第2章功能分析及逻辑分析2.1功能分析74283为4为超前进位加法器,不同于普通串行进位加法器由低到高逐级进位,超前进位加法器所有位数的进位大多数情况下同时产生,运算速度快,电路结构复杂。

4bits超前进位加法器全定制设计实验报告

TPLH

Propagation Delay Time

A1~A4,B1~B4到C4

3

ns

TPHL

3

tT

2.5

tP

2.5

Av Power

4

Layout Area

150*180

2.5真值表

2.6逻辑图

工艺的主要参数(smic18工艺)

参数

参数定义

PMOS数值

NMOS数值

U0

迁移率

8.661m

34m

Vth

-0.4

mA

IOL

Low Level OutputVoltage

8

mA

2.3直流特性

Symbol

Parameter

Test Condition

Value

Units

TA=25°C

Min

Typ

Max

VOH

High Level OutputVoltage

VCC=Min,IOH=Max

VIL=Max,VIH=Min

mA

C0

-0.4

II

InputCurrent @ Max Input Voltage

VCC=Max

VI=7.2V

A,B

0.2

mA

C0

0.1

ICC

Supply Current

VCC=Maxl

Parameter

From (Input )to (Ouput)

Test Condition

(2)点选LM视窗上面的工具列File→New→Library;

(3)会产生New Library画面;

(4)在框内填入库名;

4位超前进位加法器

4位超前进位加法器详细设计姓名:魏可望(23)班级:微电子1102指导老师:杜慧敏日期:2014年4月29日1设计目标 (3)1.1功能定义 (3)1.2引脚描述 (3)1.2.1 4位超前进位加法器系统级信号 (3)1.2.2 4位超前进位加法器输入接口定义 (3)1.2.3 4位超前进位加法器的器输出接口定义 (3)2 模块设计 (3)3测试 (4)4设计开发环境 (4)5设计开发计划 (4)1设计目标1.1功能定义本文描述4位超前进位加法器的详细设计方案。

其功能是求出4位超前进位加法器功能,并在FPGA开发板上验证设计的正确性。

1.2引脚描述1.2.1 4位超前进位加法器单元系统级信号1.2.2 4位超前进位加法器输入接口定义1.2.3 4位超前进位加法器输出接口定义2 模块设计本设计按要求,用assign语句设计4位超前进位加法器。

3测试本单元电路控制逻辑采用systemverilog断言描述状态信息测试,数据通路部分用采用sysetemverilog随机验证的方法,并结合覆盖率检测,做到100%验证。

将本设计下载到Sparten 3E开发板上,将计数器的输出连接到LED灯上,以验证设计的正确性。

4设计开发环境语言级设计:Verilog综合工具:xilinx 14.7rFPGA设计和仿真工具:ISE13.2,synopsys VCS布局和布线工具:appllo ,模拟设计和仿真工具: modelsim寄生参数提取和仿真工具: star_sim RC5设计开发计划附录:4位超前进位加法器源代码:module add_ahead4(sum,cout,a,b,cin);input[3:0] a,b;input cin;output[3:0] sum;output cout;wire[3:0] G,P;wire[3:0] C,sum;assign G[0]=a[0]&b[0];assign P[0]=a[0]|b[o];assign C[0]=cin;assign sum[0]=G[0]^P[0]^C[0];assign G[1]=a[1]&b[1];assign P[1]=a[1]|b[1];assign C[1]=G[0]|(P[0]&cin); assign sum[1]=G[1]^P[1]^C[1]; assign G[2]=a[2]&b[2]; assign P[2]=a[2]|b[2];assign C[2]=G[1]|(P[1]&C[1]); ssign sum[2]=G[2]^P[2]^C[2]; assign G[3]=a[3]&b[3]; assign P[3]=a[3]|b[3];assign C[3]=G[2]|(P[2]&C[2]); assign sum[3]=G[3]^P[3]^C[3]; assign cout=G[3]|(P[3]&C[3]); endmodule。

数字电路课程设计之超前进位加法器

reg

Cin;

wire[3:0] S;

wire

Cout;

carry_look_add CAL (.A(A),.B(B),.Cin(Cin),.Cout(Cout),.S(S)); initial begin

#10 A=4'd0;B=4'd0;Cin=0; #10 A=4'd11;B=4'd1;Cin=0; #10 A=4'd10;B=4'd12;Cin=0; #10 A=4'd11;B=4'd4;Cin=0; #100 $stop; end endmodule

Pi=Ai○+ Bi;

可以得到输出与进位表达

Gi=AiBi;

Si=Pi○+ Ci;

Ci+1=Gi+PiCi; Gi 为进位产生,不管输入进位 Ci 为什么,只要 Ai 与 Bi 为 1 时,它将产生进位。Pi 称为进位传输,因为它 与从 Ci 到 Ci+1 的进位传输有关

C0 = 输入进位

C1 = G0 + P0C0

Half_Add H3(.a(A[2]),.b(B[2]),.s(v6),.c(v5));

Half_Add H4(.a(A[3]),.b(B[3]),.s(v8),.c(v7));

carry_look

CL1(.C0(Cin),.P0(v2),.G0(v1),.P1(v4),.G1(v3),.P2(v6),.G2(v5),.P3(v8),.G3(v7),.C1(o1),.C2(o2),.C3(o3),.C4(Cout));

注意 C4 并不需要等待 C3,实际上 C4,C3,C2,C1 同时传输 超前进位产生的电路逻辑图

数字电路课程设计之超前进位加法器

# MACRO ./mul_run_msim_rtl_verilog.do PAUSED at line 14

通过查阅资料将 Verilog 测试文件

Timsbench 文件没有实例化,修改为

修改后仿真 OK 参考文献: 1.数字设计与 Verilog 实现 M.Morris Mano 著 第五版

Pi=Ai○+ Bi;

可以得到输出与进位表达

Gi=AiBi;

Si=Pi○+ Ci;

Ci+1=Gi+PiCi; Gi 为进位产生,不管输入进位 Ci 为什么,只要 Ai 与 Bi 为 1 时,它将产生进位。Pi 称为进位传输,因为它 与从 Ci 到 Ci+1 的进位传输有关

C0 = 输入进位

C1 = G0 + P0C0

instance name in instantiation of 'carry_look_add'.

#

#

Region: /carry_look_add_tb

# Error loading design

# Error: Error loading design

#

Pausing macro execution

基于 Verilog 的四位超前进位加法器设计

使用 Verilog 语言实现四位超前进位加法器设计,并使用 Quartes 编写程序,使用 modelsin 进行仿真

验证设计

二、原理介绍

超前进位加法器(图为全加器)

Ai

1

3

Pi

Bi

2

1

3

Si

2

1 3 Gi

2

Ci

1

3

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

1.课程设计名称四位超前进位加法器2.课程设计内容设计一个四位加法器,要求要有超前进位,减小输出的延迟,采用0.13um工艺设计。

3.课程设计目的训练学生综合运用学过的数字集成电路的基本知识,独立设计相对复杂的数字集成电路的能力。

4.课程设计要求4.1、按设计指导书中要求的格式书写,所有的内容一律打印;4.2、报告内容包括设计过程、仿真的HSPICE网表,软件仿真的结果及分析、延时的手工计算;4.3、要有整体电路原理图,仿真的波形图;4.4、软件仿真必须要有必要的说明;要给出各个输入信号的具体波形和输出信号的测试结果。

4.5、写出对应的HSPICE设计网表,网表仿真结果符合设计要求。

把仿真图形附在报告上。

4.6、设输入端的电容为C,输出端的负载电容为5000C inv,从输入到输出任意找一通inv路,优化通路延时,手工计算确定通路中每个门对应的晶体管的尺寸。

每组三个同学选择不能为同一通路。

此部分的计算参数可采用书中第六章的参数。

4.7、各种器件的具体结构可参考阎石的《数字电子技术基础》一书。

不允许有完全一样的报告,对于报告完全相同者,记为不及格。

5.使用软件软件为HSPICE和COSMOS-SCOPE。

6.课程设计原理由全加器的真值表可得S i和C i的逻辑表达式:定义两个中间变量G i和P i:当A i=B i=1时,G i=1,由C i的表达式可得C i=1,即产生进位,所以G i 称为产生量变。

若P i=1,则A i·B i=0,C i=C i-1,即P i=1时,低位的进位能传送到高位的进位输出端,故P i称为传输变量,这两个变量都与进位信号无关。

将G i和P i代入S i和C i得:进而可得各位进位信号的逻辑表达如下:根据逻辑表达式做出电路图(如图):逻辑功能图中有2输入异或门,2输入与门,3输入与门,4输入与门,2输入或门,3输入或门,4输入或门,其转化成CMOS晶体管图如下:7.课程设计网表*xor 2.subckt xor2 a b c d fmxorpa 1 a vdd vdd pmos l=2 w=8 mxorpb f d 1 vdd pmos l=2 w=8 mxorpc 2 b vdd vdd pmos l=2 w=8 mxorpd f c 2 vdd pmos l=2 w=8 mxorna f a 3 0 nmos l=2 w=4 mxornb 3 b 0 0 nmos l=2 w=4 mxornc f c 4 0 nmos l=2 w=4 mxornd 4 d 0 0 nmos l=2 w=4.ends xor2*and2.subckt and2 a b fmandpa f a vdd vdd pmos l=2 w=4 mandpb f b vdd vdd pmos l=2 w=4mandna f a 1 0 nmos l=2 w=4 mandnb 1 b 0 0 nmos l=2 w=4.ends and2*and3.subckt and3 a b c fmandpa f a vdd vdd pmos l=2 w=4 mandpb f b vdd vdd pmos l=2 w=4 mandpc f c vdd vdd pmos l=2 w=4 mandna f a 1 0 nmos l=2 w=6 mandnb 1 b 2 0 nmos l=2 w=6 mandnc 2 c 0 0 nmos l=2 w=6.ends and3*and4.subckt and4 a b c d fmandpa f a vdd vdd pmos l=2 w=4 mandpb f b vdd vdd pmos l=2 w=4 mandpc f c vdd vdd pmos l=2 w=4 mandpd f d vdd vdd pmos l=2 w=4 mandna f a 1 0 nmos l=2 w=8 mandnb 1 b 2 0 nmos l=2 w=8 mandnc 2 c 3 0 nmos l=2 w=8 mandnd 3 d 0 0 nmos l=2 w=8.ends and4*or2.subckt or2 a b fmorpa 1 a vdd vdd pmos l=2 w=8 morpb f b 1 vdd pmos l=2 w=8 mna f a 0 0 nmos l=2 w=4mnb f b 0 0 nmos l=2 w=4.ends or2*or3.subckt or3 a b c fmorpa 1 a vdd vdd pmos l=2 w=12 morpb 2 b 1 vdd pmos l=2 w=12 morpc f c 2 vdd pmos l=2 w=12 mna f a 0 0 nmos l=2 w=4mnb f b 0 0 nmos l=2 w=4mnc f c 0 0 nmos l=2 w=4.ends or3*or4.subckt or4 a b c d fmorpa 1 a vdd vdd pmos l=2 w=16morpb 2 b 1 vdd pmos l=2 w=16morpc 3 c 2 vdd pmos l=2 w=16morpd f d 3 vdd pmos l=2 w=16mna f a 0 0 nmos l=2 w=4mnb f b 0 0 nmos l=2 w=4mnc f c 0 0 nmos l=2 w=4mnd f d 0 0 nmos l=2 w=4.ends or4*not.subckt not a fmnotpa f a vdd vdd pmos l=2 w=4 mnotna f a 0 0 nmos l=2 w=2.ends not *反相器*or21.subckt or21 a b fxor2 a b 1 or2xnot 1 f not.ends or21 *2输入或门*or31.subckt or31 a b c fxor3 a b c 1 or3xnot 1 f not.ends or31 *3输入或门*or41.subckt or41 a b c d fxor4 a b c d 1 or4xnot 1 f not.ends or41 *4输入或门*xor21.subckt xor21 a b fxm a A5 notxn b B5 notxxor a b A5 B5 f xor2.ends xor21 * 2输入异或门*and21.subckt and21 a b fxand2 a b 1 and2xnot 1 f not.ends and21 *2输入与门*and31.subckt and31 a b c fxand3 a b c 1 and3xnot 1 f not.ends and31 *3输入与门*and41.subckt and41 a b c d fxand4 a b c d 1 and4xnot 1 f not.ends and41 *4输入与门xxor211 a1 b1 p1 xor21xxor212 a2 b2 p2 xor21xxor213 a3 b3 p3 xor21xxor214 a4 b4 p4 xor21xand211 a1 b1 g1 and21xand212 a2 b2 g2 and21xand213 a3 b3 g3 and21xand214 p1 c0 m0 and21xor211 m0 g1 c1 or21 *进位C1xand311 p2 p1 c0 m1 and31xand215 p2 g1 m2 and21xor312 g2 m1 m2 c2 or31 *进位C2 xand411 p3 p2 p1 c0 m3 and41xand313 p3 p2 g1 m4 and31xand216 p3 g2 m5 and21xor412 m3 m4 m5 g3 c3 or41 *进位C3 xxor215 p1 c0 s1 xor21 *输出s1xxor216 p2 c1 s2 xor21 *输出s2xxor217 p3 c2 s3 xor21 *输出s3xxor218 p4 c3 s4 xor21 *输出s4.include "c:\lib\130nm_bulk.l"tt.opt scale=0.05u.global vdd gndvdd vdd 0 1.2va1 a1 0 pulse 1.2 1.2 20n 1f 1f 30n 100nva2 a2 0 pulse 0 0 20n 1f 1f 30n 100nva3 a3 0 pulse 0 0 20n 1f 1f 30n 100nva4 a4 0 pulse 0 0 20n 1f 1f 30n 100nvb1 b1 0 pulse 1.2 1.2 20n 1f 1f 30n 100n vb2 b2 0 pulse 1.2 1.2 20 1f 1f 30n 100nvb3 b3 0 pulse 0 0 20n 1f 1f 30n 100nvb4 b4 0 pulse 1.2 1.2 20n 1f 1f 30n 100nvc0 c0 0 pulse 0 0 4n 1f 1f 0n 100n.tran 1n 100n.plot tran v(s1).plot tran v(s2).plot tran v(s3).plot tran v(s4).end8.结果及分析由波形可知:当输入a1=1,b1=1,前一级进位c0=0时,s1=a1+b1+c0=0,下一级进位c1=1.由波形可知:当输入a2=0,b2=1,前一级进位c1=1时,s2=a2+b2+c1=0,下一级进位c2=1.由波形可知:当输入a3=0,b3=0,前一级进位c2=1时,s3=a3+b3+c2=1,下一级进位c3=0.由波形可知:当输入a4=0,b4=1,前一级进位c3=0时,s4=a4+b4+c2=1。

根据四幅图片可知:两个加数A(a4a3a2a1)=0001和B(b4b3b2b1)=1011,和S(s4s3s2s1)=1100 进位C(c3c2c1c0)=0110.故S(s4s3s2s1)=A(a4a3a2a1)+B(b4b3b2b1)9.延时手工计算选择路劲是A3(B3)到S4,则按顺序依次经过一个2输入异或门,一个3输入与非门,一个反相器,一个4输入的或非门,一个反相器,一个反相器,一个2输入异或门。

门的类型个数逻辑强度LE 寄生参数P2输入异或门 2 2 23输入与非门 1 5/3 3/24输入或非门 1 9/3 3反相器 3 1 1/2逻辑强度:LE=2*2*5/3*9/3*1*1*1=20电学强度:FO=Cout/Cin=5000分支强度:BE=4路径强度:PE=LE*FO*BE=400000级强度:SE=6.3归一化延迟:D=N*SE+P=7*6.3+(2*2+3/2+3+1/2*3)=54延迟:T=Tinv*D=7.5*54=405(ps)10.总结本次课程设计我选择了四位超前进位加法器。