四位二进制超前进位全加器

四位二进制加法器的设计[1]

![四位二进制加法器的设计[1]](https://img.taocdn.com/s3/m/713fdc13866fb84ae45c8d4b.png)

长安大学电子技术课程设计四位二进制加法器专业班级姓名指导教师日期四位二进制加法器一、技术要求(1)四位二进制加数与被加数输入(2)二位数码管显示二、摘要理论上,由二进制数算法的运算可知,加、减、乘、除运算都可分解成加法进行运算,而实际上,为了减少硬件复杂性,这些运算基本上也是通过加法来实现的。

此次设计的是简单的四位二进制加法器。

设计中通过不断改变脉冲信号,来控制数码管的显示。

本次设计选择一个超前进位的4位全加器74LS283。

译码器选择五输入八输出的译码器,用二位数码管显示,采用七段显示译码器。

本次设计采用的是共阴极数码管,所以选择74ls48译码器三、总体设计方案论证与选择设计四位二进制加法器,可以选择串行二进制并行加法器,但为了提高加法器的运算速度,所以应尽量减少或除去由于进位信号逐级传递所花费的时间,使各位的进位直接由加数和被加数来决定,而无须依赖低位进位,因而我们选择超前进位的4位全加器74LS283。

设一个n位的加法器的第i位输入为a i、b i、c i,输出s i和c i+1,其中c i是低位来的进位,c i+1(i=n-1,n-2,…,1,0)是向高位的进位,c0是整个加法器的进位输入,而c n是整个加法器的进位输出。

则和s i=a i + b i + c i+a i b i c i (1)进位c i+1=a i b i+a i c i+b i c i (2)令g i=a i b i,(3)p i=a i+b i, (4)则c i+1= g i+p i c i (5)只要a i b i=1,就会产生向i+1位的进位,称g为进位产生函数;同样,只要a i+b i=1,就会把c i传递到i+1位,所以称p为进位传递函数。

把(5)式展开,得到c i+1= g i+ p i g i-1+p i p i-1g i-2+…+ p i p i-1…p1g0+ p i p i-1…p0c0 (6)随着位数的增加(6)式会加长,但总保持三个逻辑级的深度,因此形成进位的延迟是与位数无关的常数。

组合逻辑课程设计4位二进制全加器全减器原创

关键字 74LS283 全加器、四位二进制、迭代电路、并行进位、串行进位、VHDL

摘要

加法器是数字系统中产生数的和的装置。加数和被加数为输入,和数与进 位为输出的装置为半加器。若加数、被加数与低位的进位数为输入,而和数与进

...

.

..

..

位为输出则为全加器。例如:为了节省资源,减法器和硬件乘法器都可以用加法 器来构成。但宽位加法器的设计是很耗资源的,因此在实际的设计和相关饿得设 计与开发中需要注意资源的利用率和进位速度两方面的问题,多位加法器的构成 主要有两种:并行进位和串行进位。并行进位加法器设有并行进位产生逻辑,运 行速度比串行进位快;串行进位是将全加器采取并行级联或菊花链式级联构成多 位加法器。加法器也是常用作计算机算术逻辑部件,执行逻辑操作、移位与指令 调用。此外还可以用来表示各种数值,如:BCD、加三码,主要的加法器是以二 进制作运算。

1 0 0100 11011000

1 0 0101 00011010

1 0 0001 10011100

1 0 0001 10111110

1 0 1010 01000111

1 0 1010 01101001

1 0 0010 01000011

1 0 0010 01100101

... ... ... ... ... ... ... ... ... ... ... ... ... ...

4位加法器的设计原理

4位加法器的设计原理四位加法器是一种数字电路,用于实现四位二进制数的加法运算。

它由多个逻辑门组成,主要包括四个全加器、一个四路二选一选择器和一个四位二进制数输出。

在四位加法器中,每个全加器都负责计算两个输入位和上一位的进位的和。

全加器的原理是采用异或门(XOR)、与门(AND)和或门(OR)的组合。

具体来说,全加器有三个输入端,分别是两个输入位(A和B)和上一位的进位(Cin),两个输出端,分别是当前位的和(S)和当前位的进位(Cout)。

全加器的计算公式如下:S = (A XOR B) XOR CinCout = AB + (A XOR B)Cin其中,“XOR”代表异或操作,“AND”代表与操作,“OR”代表或操作。

全加器的设计原理是基于四位二进制数的加法运算规则。

在四位加法过程中,每一位的和由该位的两个输入位和上一位的进位确定。

进位则与上一位的输入位和上一位的进位有关。

因此,通过级联四个全加器,就可以实现四位加法运算。

除了四个全加器以外,四位加法器还包括一个四路二选一选择器。

这个选择器根据一个控制信号选择输出。

四位加法器的输出是一个四位二进制数,可以选择以原码、反码或补码的形式输出。

通过选择器的控制信号,可以选择输出形式。

四位加法器的工作原理是:首先,将四个输入数两两相加,得到每一位的和,以及进位。

然后,将每一位的和通过四个全加器计算得到最终的和,同时将进位以及控制信号传递给选择器。

最后,选择器选择要输出的结果。

总结来说,四位加法器是基于全加器的构建的数字电路,可以实现四位二进制数的加法运算。

它的设计原理是根据四位二进制数加法的规则和全加器的计算公式,通过级联四个全加器,并通过选择器控制输出形式,实现四位二进制数的加法运算。

四位二进制串行加法器

四位二进制串行加法器是一种实现二进制加法的电路,它每次处理一个四位二进制数的加法运算。

这种加法器通常由多个全加器组成,每个全加器都能执行两个一位二进制数的加法运算,同时还能计算来自低位的进位。

在四位二进制串行加法器中,每个全加器都接收两个输入位(来自两个二进制数)和一个进位输入(来自低位全加器的进位输出)。

全加器的输出包括两个位(和与进位)和一个进位输出,该输出将作为下一个全加器的进位输入。

例如,对于两个四位的二进制数(1101 和0110),第一个全加器将执行1+0 的加法运算,产生一个和(1)和一个进位(1)。

这个进位将作为下一个全加器的进位输入,第二个全加器将执行1+1 的加法运算,产生一个和(0)和一个进位(0),这个进位将作为下一个全加器的进位输入,依此类推。

总的来说,四位二进制串行加法器是一种有效的实现长二进制数加法的电路,它通过使用多个全加器来逐位处理输入的二进制数并计算进位,从而实现了高效的二进制加法运算。

四位超前进位加法器原理

四位超前进位加法器原理1. 输入部分:四位超前进位加法器有两个四位输入数和一个进位输入。

输入数A和B分别代表被加数和加数,每位由低位到高位分别为A0,A1,A2,A3和B0,B1,B2,B3、进位输入Cin表示上一位的进位情况。

2. 输出部分:四位超前进位加法器有一个四位输出数和一个进位输出。

输出数S代表和,每位由低位到高位分别为S0,S1,S2,S3、进位输出Cout表示本位的进位情况。

3. 逻辑运算:每位的和采用异或门(XOR)实现:Si = A ⊕ B ⊕ Cin。

每位的进位采用与门(AND)实现:Ci+1 = (A ⊕ B) ∧ Cin + A∧ B。

4. 进位传递:如果上一位的进位Cin为1,则本位需要传递进位,即Ci+1 = 1、如果上一位的进位Cin为0,则本位不需要传递进位,即Ci+1 = (A ⊕ B) ∧ Cin。

这样可以确保进位在高位传递,实现加法运算的正确性。

5. 进位溢出:最高位的进位输出Cout表示四位相加是否产生进位溢出,即Cout = A3 ∧ B3 ∧ Cin。

如果Cout为1,则表示加法运算的结果超过了四位二进制数的表示范围,发生了进位溢出。

(1)将输入的两个四位二进制数A和B依次与进位输入Cin相异或,得到每位的和Si。

(2)将输入的两个四位二进制数A和B依次与进位输入Cin相与,得到进位传递结果Di。

(3)将邻位的进位传递结果Di与当前位的和Si再次相与,得到进位输出结果Ci+1(4)将当前位的和Si输出为结果的相应位,将进位输出结果Ci+1作为下一位的进位输入。

(5)最高位的进位输出结果Cout表示加法运算是否产生进位溢出。

四位超前进位加法器的优点是速度快,可以实现高速的加法运算。

其核心原理是采用异或门进行和的计算,采用与门进行进位的计算,通过逐位运算,实现了四位二进制数的加法运算,同时处理了进位情况,确保了运算的正确性。

4位二进制加法器解析

《电工与电子技术基础》课程设计报告题目四位二进制加法计数器学院(部)汽车学院专业汽车运用工程班级22020903学生姓名郭金宝学号220209031006 月12 日至06 月22 日共 1.5 周指导教师(签字)评语评审人:四位二进制加法器一.技术要求1.四位二进制加数与被加数输入2.二位显示二.摘要本设计通过逻辑开关将A3,A2,A1,A0和B3,B2,B1,B0信号作为加数和被加数输入到超前进位加法器74LS283中进行四位二进制相加,将输出信号S4,S3,S2,S1和向高位的进位C1输入一个译码器译码。

再将输出信号X4,X3,X2,X1和Y4,Y3,Y2,Y1分别输入一个74LS247型的七段显示译码器译码,最后分别接一个BS204数码管进行二位显示。

关键字:74LS283 74LS247 BS204三.总体设计方案的论证及选择1.加法器的选取加法器有两种,分别是串行进位加法器和超前进位加法器。

串行进位加法器由全加器级联构成,高位的运算必须等到低位加法完成送来进位时才能进行。

它虽然电路简单,但运算速度较慢,而且位数越多,速度就越慢。

T692型集成全加器就是这种四位串行加法器。

超前进位加法器由逻辑电路根据输入信号同时形成各位向高位的进位。

使各位的进位直接由加数和被加数来决定,而不需依赖低位进位,这就省去了进位信号逐级传送所用的时间,所以这种加法器能够快速进位。

因为它的这个优点我们选取超前进位加法器。

超前进位加法器的型号有多种,由于我们是非电专业,对电子器件的选取要求不高,为使设计简单所以选74LS283型加法器。

2.译码器的选取译码器的功能是将二进制代码(输入)按其编码时的原意翻译成对应的信号或十进制数码(输出)。

译码器是组合逻辑电路的一个重要器件,其可以分为:变量译码和显示译码两类。

译码器的种类很多,但它们的工作原理和分析设计方法大同小异,其中二进制译码器、二-十进制译码器和显示译码器是三种最典型,使用十分广泛的译码电路。

quartus_4位二进制加减法计数器

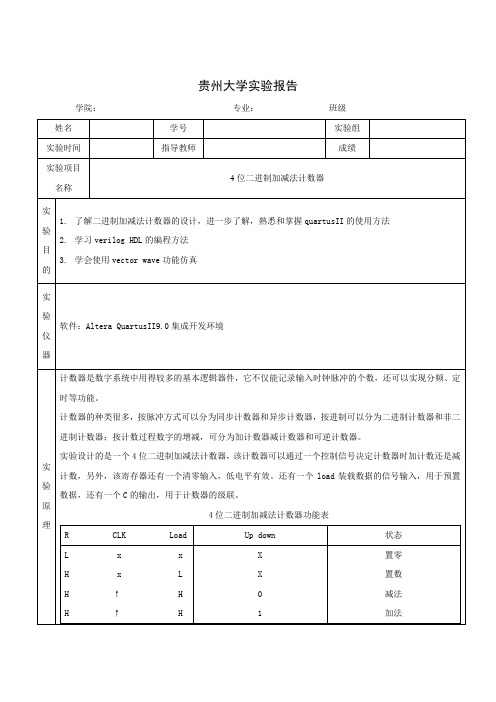

贵州大学实验报告学院:专业:班级设计原理框图从原理图中可见,需要有1bit装载位(load)、1bit清零位(clr)、方向控制位up_down和4bit数据选择位DIN[3..0]。

装载位我们采用SW0,清零位采用SW1,方向控制位为SW2。

SW3-SW6作为数据输入端,LED1-LED4显示数据的输出,LED5为溢出标志位。

实验内容编写一个带预置输入,清零输入,可加可减计数器的verilog代码或VHDL代码并仿真,编译下载验证module counter4(load,clr,c,DOUT,clk,up_down,DIN);//定义模块input load;//定义输入信号input clk;//wire load;//定义线网型input clr;//wire clr;//input up_down;//wire up_down;//input [3:0]DIN;//定义4位二进制输入信号wire [3:0]DIN;// 定义4位二进制线网型信号output c;//定义输出信号reg c;//定义寄存器类型信号output [3:0]DOUT;//wire [3:0]DOUT;reg [3:0]data_r;assign DOUT=data_r;always@(posedge clk or posedge clr or posedge load)//检测clk,clr,load的上升沿beginif(clr)//当clr=1的时候进行下面的运行程序data_r<=0;//将data_r置零else if(load) //当load=1的时候进行下面的运行程序data_r<=DIN;//将DIN的值赋给data_relse begin if(up_down)//load=0的时候进行下面的操作beginif(data_r==4'b1111)begin///当data_r==4'b1111的时候进行下面的运行程序data_r<=4'b0000;c=1;endelse begin//当data_r不等于4'b1111的时候进行下面的运行程序data_r<=data_r+1;//进行加法计数c=0;endendelsebeginif(data_r==4'b0000)begin//当data_r==4'b0000的时候进行下面的运行程序data_r<=4'b1111;c=1;endelse begin//当data_r不等于4'b1111的时候进行下面的运行程序data_r<=data_r-1;//进行减法计数c=0;endendendendendmodule//结束模块实验数据如图为波形仿真结果,当clr为1的时候,输出结果为0000;当clr为0,load为1时,输出结果为输入数据DIN的值,当up_down为1时,加法进位,进行加1运算,当data_r达到1111时,data_r变为0000,级零信号c为1;当up_down为0时,减法进位,进行减1运算,当data_r达到0000时,data_r变为1111,级零信号c为0。

4位同步二进制加法计数器计数最大值

4位同步二进制加法计数器是一种常见的数字电路,用于实现二进制计数。

它可以将二进制数字表示为电信号,并且在每次输入脉冲时进行递增。

下面将详细介绍4位同步二进制加法计数器及其计数的最大值。

一、4位同步二进制加法计数器的原理1. 4位同步二进制加法计数器由4个触发器组成,每个触发器对应一个二进制位。

当输入一个脉冲时,每个触发器根据前一位的状态以及输入脉冲的信号进行状态转换。

这样就实现了二进制数的递增。

2. 触发器之间通过门电路连接,用于控制触发器状态的变化。

这些门电路可以根据具体的设计选择不同的逻辑门,常见的有AND门、OR 门、NOT门等。

3. 4位同步二进制加法计数器是同步计数器,即所有触发器同时接收输入脉冲,确保计数的同步性。

二、4位同步二进制加法计数器的计数最大值1. 4位二进制数的表示范围是0~15,因此4位同步二进制加法计数器的计数最大值为15。

2. 在计数到15后,再输入一个脉冲,计数器将重新从0开始计数,即实现了循环计数。

三、4位同步二进制加法计数器的应用1. 4位同步二进制加法计数器常用于数字电子钟、信号发生器等数字电路中,用于实现计数和定时功能。

2. 它还可以作为其他数字电路的组成部分,用于构建更复杂的逻辑功能。

3. 在数字系统中,计数器是十分重要的组件,它能够实现数字信号的计数和控制,广泛应用于各种数字系统中。

4位同步二进制加法计数器是一种重要的数字电路,通过它可以实现对二进制数的递增计数。

其计数的最大值为15,应用领域广泛。

希望本文内容能够对读者有所启发。

四、4位同步二进制加法计数器的工作原理4位同步二进制加法计数器是一种晶体管数字集成电路,它利用触发器和逻辑门等基本元件构成,能够实现二进制数字的加法计数。

在4位同步二进制加法计数器中,每个触发器代表一个二进制位,通过输入脉冲的控制,能够实现对二进制数的递增计数。

具体来说,当输入一个脉冲信号时,4位同步二进制加法计数器会根据触发器之间的连线和逻辑门的作用,根据之前的状态和输入脉冲的信号进行状态转换,从而实现二进制数的递增。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

•超前进位加法原理

A0 B0

C-1 A0 B0 A1 B1

C-1 A0 A1B0 B1 A2 B2 C-1 A0 A2 B0 B2 A3 B3 C-1 A0 A3 B0 B3

……

…

…

0 C-1 FA0

C0 进位逻辑

C0 FA1

C1 进位逻辑

C1 FA2

C2 进位逻辑

C2 FA3

C3 进位逻辑 C3

S0

0

C0

C1

C2

C3

C-1

FA0

FA1

FA2

FA3

S0

S1

S2

C3

S3

CO ∑

CI CI

CI

A3 B3

C2

S2

CO ∑

CI CI

CI

A2 B2C1S1Fra bibliotekCO ∑

CI CI

CI

A1 B1

所求结果为:C3S3S2S1S0

S3

C0

S0

CO ∑

CI CI

CI

A0 B0

C0-1

超前进位全加器-----74LS283

S1

S2

S3

• 进位输入是由专门的“进位逻辑门”来提供 • 该门综合所有低位的加数、被加数及最低位进位输入

超前进位加法器使每位的进位直接由加数和被加数产生, 而无需等待低位的进位信号

Si Ai Bi Ci1 Ci Ai Bi AiCi1 BiCi1

定义两个中间变量Gi和Pi : Gi= AiBi ……产生变量 Pi= Ai+Bi ……传输变量 Ki= GiPi = Ai ⊕Bi ……中间变量

全加器真值表

输入端:Ai、Bi、Ci-1

输出端:Si、Ci A为加数,B为被加数 如A=1101, A3=1,A2=1,A1=0, A0=1

Ai Bi Ci-1 Si Ci

00 000 00 110

01 010

0 1 1 01 10 010

10 101

11 001

11 111

Ci-1表示进位输入

例:11+10=101 若看高位则A1=1 , B1=1,而低位进位输入C0=0,所以相

S3= K3⊕C2 = A3 ⊕ B3 ⊕ C2

进位信号的产生

Si= Ki ⊕Ci-1 Ci= Gi+Pi Ci-1

C0= G0+P0 C-1

C1= G1+P1 C0= G1+P1 G0+ P1P0 C-1

C2= G2+P2 C1= G2+P2 G1+ P2 P1 G0+ P2 P1 P0C-1 C3= G3+P3 C2= G3+P3 G2+ P3 P2 G1+ P3P2 P1G0

注意进位信号的产生

Si= Ki ⊕ Ci-1 Ci= Gi+Pi Ci-1

本位和信号的产生

Si= Ki ⊕Ci-1 Ci= Gi+Pi Ci-1

S0= K0 ⊕C-1 = A0 ⊕ B0 ⊕ C-1 S1= K1 ⊕C0 = A1 ⊕ B1 ⊕ C0 S2= K2⊕C1 = A2 ⊕ B2 ⊕ C1

2. 并行进位加法器: 并行进位加法器的所有各位的进位都直接依赖最低 位进位C-1(值为0),即所有各位的进位可以直接 从C-1并行产生,因此又称为超前进位。超前进位 的所有位数进位是同时完成的,运算速度快 。

4位串行进位全加器----采用四个1位全加器组成

A0 B0

A1 B1

A2 B2

A3 B3

+ P3P2 P1 P0C-1

因为进位信号只与变量Gi、Pi和 C-1有关,而C-1是向最低 位的进位信号,其值为0,即各位的进位信号都只与两个加 数A和B有关,所以它们是可以并行产生的。

B3

A3 B2

A2 B1 A1 B0 A0 C-1

&

P3

≥1

&

P2

≥1

&

≥1 P1

&

≥1 P0

1

74LS283逻辑图

=1 =1 Si

&

&

Ci

&

逻辑图

实现电路

集成全加器

• 在一位全加器的基础上,通过多级级联可以构成多 位全加器,称为集成全加器,而进位方式分串行进 位和并行进位两种。

1. 串行进位加法器:把n个全加器按低位的进位输出 与高位的进位输入相连的方法连接起来,各位全加 器的进位信号以串联形式逐位传递、逐位产生的并 行加法器称为串行进位加法器。

Ci表示进位输出 加之后C1=1,S1=0。输出的结果就是

S表示本位和

C1S1S0=101

逻辑表达式:

Ai

Si AiBiCi1 AiBiCi1 AiBiCi1 AiBiCi1 B i

Ai Bi Ci1

Ci-1

Ci Ai Bi BiCi1 AiCi1

Ai

∑

Si

Bi

Ci-1

CI

CO

Ci

74LS283

• 功能:四位二进制超前进位全加器。 • 全加和半加: 1. 若不考虑有来自低位的进位将两个

1位二进制数相加,称为半加。

2. 将两个多位二进制数相加时,除了 最低位以外,每一位都应考虑来自 低位的进位,即将两个对应的加数 和来自低位的进位3个数相加,这 种运算称为全加。

全加器

全加器逻辑符号:

1 ≥1

& & &

&

CO (C3)

&

K3

1 ≥1

&

=1

S3

&

C2

&

&

K2

1 ≥1

&

=1

S2

&

C1

&

K1

=1

S1

1 ≥1

&

C0

&

K0

=1

S0

1

C-1

Si= Ki ⊕Ci-1 Ci= Gi+Pi Ci-1

Gi= AiBi Pi= Ai+Bi Ki= GiPi = Ai ⊕Bi