设计示例432位先行进位加法器的设计

加法器课程设计---四位二进制同步加法计数器

成绩评定表学生姓名班级学号专业课程设计题目四位二进制同步加法器(缺0000,0001,0100,0101) 评语组长签字:成绩日期 20 年月日课程设计任务书学院专业学生姓名班级学号课程设计题目四位二进制同步加法计数器(缺0000,0001,0100,0101)实践教学要求与任务:1.了解数字系统设计方法。

2.熟悉ISE仿真环境及VHDL下载。

3.熟悉Multisim仿真环境。

4.设计实现四位二进制同步加法计数器(缺0000,0001,0100,0101)工作计划与进度安排:第一周:熟悉Multisim及Xilinx及Xilinx ISE环境,练习数字系统设计方法第二周:(1)在ISE环境中仿真实现四位二进制同步加法计数器(缺0000,0001,0100,0101)。

(2)在Multisim环境中仿真实现四位二进制同步加法计数器(缺0000,0001,0100,0101),并通过虚拟仪器验证其正确性。

指导教师:201 年月日专业负责人:201 年月日学院教学副院长:201 年月日目录一、课程设计目的 (1)二、设计框图 (1)三、实现过程 (1)1、Xilinx ISE10.1实现过程(VHDL) (1)1、1、建立工程 (2)1、2、调试程序 (4)1、3、波形仿真 (5)1、4、引脚锁定与下载 (7)1、5、仿真结果分析 (10)2、Multisim10实现过程(电路设计) (10)2、1、设计原理 (10)2、2、基于Multisim的设计电路 (13)2、3、虚拟观察的波形 (14)2、4、仿真结果分析 (14)四、设计总结 (15)五、参考文献 (15)四位二进制加法计数器一. 课程设计的目的1.了解数字系统设计原理及方法。

2.熟悉Xillinx ISE 仿真环境及VHDL 下载。

3.熟悉Mutisim 仿真环境。

4.设计实现(四位二进制加法计数器(缺0000,0001,0100,0101))。

四位二进制加法器的设计[1]

![四位二进制加法器的设计[1]](https://img.taocdn.com/s3/m/713fdc13866fb84ae45c8d4b.png)

长安大学电子技术课程设计四位二进制加法器专业班级姓名指导教师日期四位二进制加法器一、技术要求(1)四位二进制加数与被加数输入(2)二位数码管显示二、摘要理论上,由二进制数算法的运算可知,加、减、乘、除运算都可分解成加法进行运算,而实际上,为了减少硬件复杂性,这些运算基本上也是通过加法来实现的。

此次设计的是简单的四位二进制加法器。

设计中通过不断改变脉冲信号,来控制数码管的显示。

本次设计选择一个超前进位的4位全加器74LS283。

译码器选择五输入八输出的译码器,用二位数码管显示,采用七段显示译码器。

本次设计采用的是共阴极数码管,所以选择74ls48译码器三、总体设计方案论证与选择设计四位二进制加法器,可以选择串行二进制并行加法器,但为了提高加法器的运算速度,所以应尽量减少或除去由于进位信号逐级传递所花费的时间,使各位的进位直接由加数和被加数来决定,而无须依赖低位进位,因而我们选择超前进位的4位全加器74LS283。

设一个n位的加法器的第i位输入为a i、b i、c i,输出s i和c i+1,其中c i是低位来的进位,c i+1(i=n-1,n-2,…,1,0)是向高位的进位,c0是整个加法器的进位输入,而c n是整个加法器的进位输出。

则和s i=a i + b i + c i+a i b i c i (1)进位c i+1=a i b i+a i c i+b i c i (2)令g i=a i b i,(3)p i=a i+b i, (4)则c i+1= g i+p i c i (5)只要a i b i=1,就会产生向i+1位的进位,称g为进位产生函数;同样,只要a i+b i=1,就会把c i传递到i+1位,所以称p为进位传递函数。

把(5)式展开,得到c i+1= g i+ p i g i-1+p i p i-1g i-2+…+ p i p i-1…p1g0+ p i p i-1…p0c0 (6)随着位数的增加(6)式会加长,但总保持三个逻辑级的深度,因此形成进位的延迟是与位数无关的常数。

课程设计--四位二进制加减法器

组合逻辑电路课程设计之四位二进制加减法器摘要:加法器即是产生数的和的装置。

加数和被加数为输入,和数与进位为输出的装置为半加器。

若加数、被加数与低位的进位数为输入,而和数与进位为输出则为全加器。

对于4位的二进制加法,相关的有五个的量:1,被加数A ,2,被加数B ,3,前一位的进位CIN ,4,此位二数相加的和S ,5,此位二数相加产生的进位COUT 。

前三个量为输入量,后两个量为输出量,五个量均为4位.本文采用4位二进制并行加法器原理,选择74LS283,74LS283是4位二进制先行进位加法器,它只用了几级逻辑来形成,并连接几个异或门,由其构成4位二进制加法器/减法器,并用Verilog HDL 进行仿真。

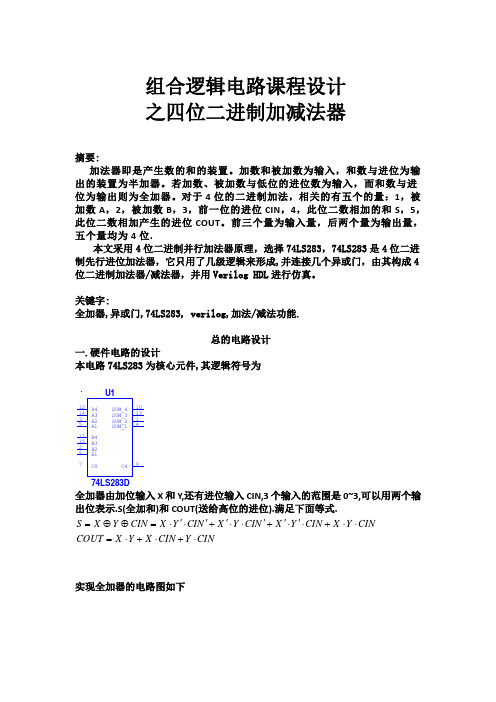

关键字:全加器,异或门,74LS283, verilog,加法/减法功能.总的电路设计 一.硬件电路的设计本电路74LS283为核心元件,其逻辑符号为U174LS283DSUM_410SUM_313SUM_14SUM_21C49B411A412B315A314B22A23B16A15C07全加器由加位输入X 和Y ,还有进位输入CIN,3个输入的范围是0~3,可以用两个输出位表示.S(全加和)和COUT(送给高位的进位).满足下面等式.CINY CIN X Y X COUT CINY X CIN Y X N CI Y X N CI Y X CIN Y X S ⋅+⋅+⋅=⋅⋅+⋅'⋅'+'⋅⋅'+'⋅'⋅=⊕⊕=实现全加器的电路图如下74LS08D本电路还需要4个异或门,要实现加法器和减法器的双重功能,需要有选择功能端,设A为四位二进制被加数,B为二进制被减数.当使能端为0时,电路实现加法运算,当使能端为1时电路实现减法运算.电路原理图如下1.Multisim原理图2.MAX plus2原理图当A口输入为0011,B口输入为0001,使能端为0时.输出为0100.电路图如下当A口输入为0011,B口输入为0001,使能端输入为1时.输出为0010.电路图如下二.软件程序设计Verilog HDL语言程序module b(A,B,C,D,E);input[3:0] A,B;input C;output[3:0] D;output E;assign {E,D}=C?(A+B):(A-B);endmodule当A口输入为0011,B口输入为0001,使能端输入为0,输出为0010,仿真图如下.当A口输入为0011,B口输入为0001,使能端输入为1时.输出为0010.仿真图如下三.总结及心得体会1.通过本次课题设计,自学了一些相关的Verilog语言和MAX+plusII,Multisim 软件的使用方法.2.基本掌握了74LS283的基本原理及使用方法.。

组合逻辑电路3之加法器和减法器

超集 前成 进二 位进 加制 法4 器位

VCC B2 A2 S2 B3 A3 S3 C3

VDD B3 C3 S3 S2 S1 S0 C0-1

16 15 14 13 12 11 10 9 74LS283

12345678

16 15 14 13 12 11 10 9 4008

120 A0 C0-1 GND TTL 加法器 74LS283 引脚图

集成算术逻辑单元

A3 B2 A2 B1 A1 B0 A0 VSS CMOS 加法器 4008 引脚图

• 减法运算

• 数字系统中,二进制数的减法运算通常是通过 加法器来实现的。例如A减B可用A加负B来完 成,因此,实现减法的实质是负数的表示问题。 二进制计数体制中,通常用补码和符号位表示 负数。定义一个无符号数N的n位自然二进制 码为该数的原码,原码各位取反定义为该数的 反码,2n减这个数的原码定义为该数的补码。

• 图用4位二进制加法器和异或门实现4位无符号二 进制数的加或减。实现加法运算时,控制信号0, 送入74283的两个数都是原码(B不反相),运行 结果为两个数之和,符号位输出为0,表示输出和 信号是原码。实现减法运算时,控制信号1,送入 74283的两个数一个是原码,另一个是反码(B反 相),同时CI=1完成反码加1作用,运行结果为 两个数之差,符号位输出为CO反相,0表示输出 和信号是原码(正数),1表示输出和信号是补码 (负数)。

加法器

1. 串行进位加法器 用全加器可以实现多位二进制加法运算,实现四位

二进制加法运算的逻辑图如图所示。图中低位进位输 出作为高位进位输入,依此类推,这种进位方式称为 异步进位。

2.集成四位二进制加法器74283

为克服异步进位方式平均传输延迟时间增大的问题,集成四位二 进制加法器74283采用了超前进位方式,从而使四位二进制加法 器平均传输延迟时间大大小于采用异步进位方式的四位二进制加 法器。74283内部逻辑图及引脚号见图。

先行进位加法器

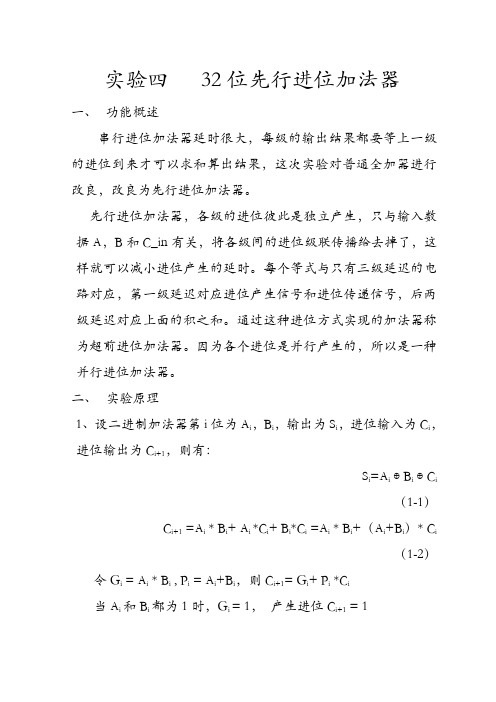

实验四32位先行进位加法器一、功能概述串行进位加法器延时很大,每级的输出结果都要等上一级的进位到来才可以求和算出结果,这次实验对普通全加器进行改良,改良为先行进位加法器。

先行进位加法器,各级的进位彼此是独立产生,只与输入数据A,B和C_in有关,将各级间的进位级联传播给去掉了,这样就可以减小进位产生的延时。

每个等式与只有三级延迟的电路对应,第一级延迟对应进位产生信号和进位传递信号,后两级延迟对应上面的积之和。

通过这种进位方式实现的加法器称为超前进位加法器。

因为各个进位是并行产生的,所以是一种并行进位加法器。

二、实验原理1、设二进制加法器第i位为A i,B i,输出为S i,进位输入为C i,进位输出为C i+1,则有:S i=A i⊕B i⊕C i(1-1)C i+1 =A i * B i+ A i *C i+ B i*C i =A i * B i+(A i+B i)* C i(1-2)令G i = A i * B i , P i = A i+B i,则C i+1= G i+ P i *C i当A i和B i都为1时,G i = 1,产生进位C i+1 = 1当A i和B i有一个为1时,P i = 1,传递进位C i+1= C i因此G i定义为进位产生信号,P i定义为进位传递信号。

G i的优先级比P i高,也就是说:当G i = 1时(当然此时也有P i = 1),无条件产生进位,而不管C i是多少;当G i=0而P i=1时,进位输出为C i,跟C i之前的逻辑有关。

下面推导4位超前进位加法器。

设4位加数和被加数为A 和B,进位输入为C in,进位输出为C out,对于第i位的进位产生G i = A i·B i ,进位传递P i=A i+B i , i=0,1,2,3。

于是这各级进位输出,递归的展开Ci,有:C0 = C inC1=G0 + P0·C0C2=G1 + P1·C1 = G1 + P1·G0 + P1·P0▪C0C3=G2+ P2·C2= G2+ P2·G1+ P2·P1·G0+P2·P1·P0·C0C4=G3+ P3·C3= G3+ P3·G2+ P3·P2·G1+P3·P2·P1·G0 + P3·P2·P1·P0·C0 (1-3)C out=C4由此可以看出,各级的进位彼此独立产生,只与输入数据Ai、Bi和Cin有关。

先行进位加法器课件

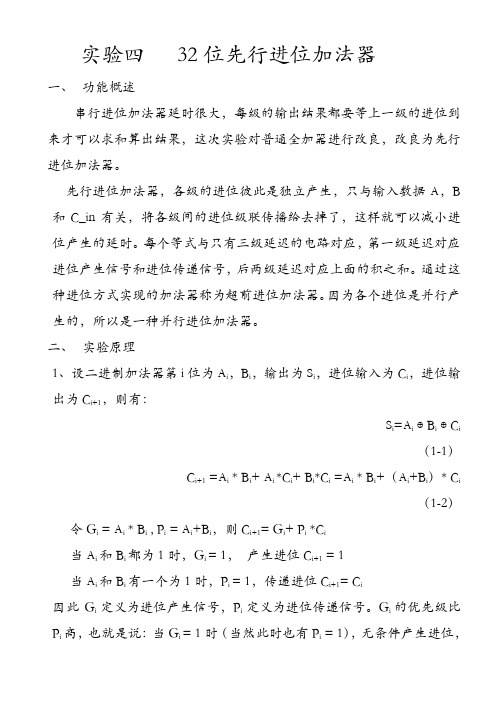

实验四32位先行进位加法器一、功能概述串行进位加法器延时很大,每级的输出结果都要等上一级的进位到来才可以求和算出结果,这次实验对普通全加器进行改良,改良为先行进位加法器。

先行进位加法器,各级的进位彼此是独立产生,只与输入数据A,B 和C_in有关,将各级间的进位级联传播给去掉了,这样就可以减小进位产生的延时。

每个等式与只有三级延迟的电路对应,第一级延迟对应进位产生信号和进位传递信号,后两级延迟对应上面的积之和。

通过这种进位方式实现的加法器称为超前进位加法器。

因为各个进位是并行产生的,所以是一种并行进位加法器。

二、实验原理1、设二进制加法器第i位为A i,B i,输出为S i,进位输入为C i,进位输出为C i+1,则有:S i=A i⊕B i⊕C i(1-1)C i+1 =A i * B i+ A i *C i+ B i*C i =A i * B i+(A i+B i)* C i(1-2)令G i = A i * B i , P i = A i+B i,则C i+1= G i+ P i *C i当A i和B i都为1时,G i = 1,产生进位C i+1 = 1当A i和B i有一个为1时,P i = 1,传递进位C i+1= C i因此G i定义为进位产生信号,P i定义为进位传递信号。

G i的优先级比P i高,也就是说:当G i = 1时(当然此时也有P i = 1),无条件产生进位,而不管C i是多少;当G i=0而P i=1时,进位输出为C i,跟C i之前的逻辑有关。

下面推导4位超前进位加法器。

设4位加数和被加数为A和B,进位输入为C in,进位输出为C out,对于第i位的进位产生G i = A i·B i,进位传递P i=A i+B i , i=0,1,2,3。

于是这各级进位输出,递归的展开Ci,有:C0 = C inC1=G0 + P0·C0C2=G1 + P1·C1 = G1 + P1·G0 + P1·P0▪C0C3=G2 + P2·C2 = G2 + P2·G1 + P2·P1·G0 + P2·P1·P0·C0C4=G3 + P3·C3 = G3 + P3·G2 + P3·P2·G1 + P3·P2·P1·G0 + P3·P2·P1·P0·C0 (1-3)C out=C4由此可以看出,各级的进位彼此独立产生,只与输入数据Ai、Bi和Cin有关。

先行进位加法器

先⾏进位加法器实验四32位先⾏进位加法器⼀、功能概述串⾏进位加法器延时很⼤,每级的输出结果都要等上⼀级的进位到来才可以求和算出结果,这次实验对普通全加器进⾏改良,改良为先⾏进位加法器。

先⾏进位加法器,各级的进位彼此是独⽴产⽣,只与输⼊数据A,B和C_in有关,将各级间的进位级联传播给去掉了,这样就可以减⼩进位产⽣的延时。

每个等式与只有三级延迟的电路对应,第⼀级延迟对应进位产⽣信号和进位传递信号,后两级延迟对应上⾯的积之和。

通过这种进位⽅式实现的加法器称为超前进位加法器。

因为各个进位是并⾏产⽣的,所以是⼀种并⾏进位加法器。

⼆、实验原理1、设⼆进制加法器第i位为A i,B i,输出为S i,进位输⼊为C i,进位输出为C i+1,则有:S i=A i⊕B i⊕C i(1-1)C i+1 =A i * B i+ A i *C i+ B i*C i =A i * B i+(A i+B i)* C i(1-2)令G i = A i * B i , P i = A i+B i,则C i+1= G i+ P i *C i当A i和B i都为1时,G i = 1,产⽣进位C i+1 = 1当A i和B i有⼀个为1时,P i = 1,传递进位C i+1= C i因此G i定义为进位产⽣信号,P i定义为进位传递信号。

G i的优先级⽐P i⾼,也就是说:当G i = 1时(当然此时也有P i = 1),⽆条件产⽣进位,⽽不管C i是多少;当G i=0⽽P i=1时,进位输出为C i,跟C i之前的逻辑有关。

下⾯推导4位超前进位加法器。

设4位加数和被加数为A 和B,进位输⼊为C in,进位输出为C out,对于第i位的进位产⽣G i = A i·B i ,进位传递P i=A i+B i , i=0,1,2,3。

于是这各级进位输出,递归的展开Ci,有:C0 = C inC1=G0 + P0·C0C2=G1 + P1·C1 = G1 + P1·G0 + P1·P0?C0C3=G2+ P2·C2= G2+ P2·G1+ P2·P1·G0+P2·P1·P0·C0C4=G3+ P3·C3= G3+ P3·G2+ P3·P2·G1+P3·P2·P1·G0 + P3·P2·P1·P0·C0 (1-3)C out=C4由此可以看出,各级的进位彼此独⽴产⽣,只与输⼊数据Ai、Bi和Cin有关。

四位二进制加法器的设计[1]

长安大学电子技术课程设计四位二进制加法器专业班级姓名指导教师日期四位二进制加法器一、技术要求(1)四位二进制加数与被加数输入(2)二位数码管显示二、摘要理论上,由二进制数算法的运算可知,加、减、乘、除运算都可分解成加法进行运算,而实际上,为了减少硬件复杂性,这些运算基本上也是通过加法来实现的。

此次设计的是简单的四位二进制加法器。

设计中通过不断改变脉冲信号,来控制数码管的显示。

本次设计选择一个超前进位的4位全加器74LS283。

译码器选择五输入八输出的译码器,用二位数码管显示,采用七段显示译码器。

本次设计采用的是共阴极数码管,所以选择74ls48译码器三、总体设计方案论证与选择设计四位二进制加法器,可以选择串行二进制并行加法器,但为了提高加法器的运算速度,所以应尽量减少或除去由于进位信号逐级传递所花费的时间,使各位的进位直接由加数和被加数来决定,而无须依赖低位进位,因而我们选择超前进位的4位全加器74LS283。

设一个n位的加法器的第i位输入为a i、b i、c i,输出s i和c i+1,其中c i是低位来的进位,c i+1(i=n-1,n-2,…,1,0)是向高位的进位,c0是整个加法器的进位输入,而c n是整个加法器的进位输出。

则和s i=a i + b i + c i+a i b i c i (1)进位c i+1=a i b i+a i c i+b i c i (2)令g i=a i b i,(3)p i=a i+b i, (4)则c i+1= g i+p i c i (5)只要a i b i=1,就会产生向i+1位的进位,称g为进位产生函数;同样,只要a i+b i=1,就会把c i传递到i+1位,所以称p为进位传递函数。

把(5)式展开,得到c i+1= g i+ p i g i-1+p i p i-1g i-2+…+ p i p i-1…p1g0+ p i p i-1…p0c0 (6)随着位数的增加(6)式会加长,但总保持三个逻辑级的深度,因此形成进位的延迟是与位数无关的常数。

四则运算计算器数字电路设计

四则运算运算计算器数字电路设计由于加减乘除计算器的各电路较复杂,就不将其组合在一起了,以下是各个加法,减法,乘法,除法计算器的单独电路图,其中输入均采用二进制四位输入。

一.加法计算器这个较为简单,可以直接利用中规模四位全加器74LS283,即可制成加法计算器。

电路图:A4 A3 A2 A1 为二进制被加数;B4 B3 B2 B1 为二进制加数;SUM4 SUM3 SUM2 SUM1 为二进制得数。

加上输入输出后如图所示:仿真图形为:前四个图像为被加数,中间四位为加数,后四位为得数。

由此可看出,已成功制成加法计算器。

二.减法计算器电路图:利用数据选择器和四输入与非门,可以实现减法计算器的功能,其中,C1 C2 C3 C4为四位二进制被减数输入端;B1 B2 B3 B4 为四位二进制减数输入端;输出端 27 26 25 24 为得数。

加上输入输出后如图所示:仿真图形如下:前四位为被减数,中间四位为减数,最下面四位为得数,由仿真图形可看出,已成功制成减法计算器。

三.乘法计算器利用中规模四位全加器74LS283和而输入与门可以实现乘法计算器功能。

其中,输入端4 3 2 1 为二进制四位被乘数,输入端5 6 7 8 为二进制四位乘数,输出端54 50 51 52 53 49 48 46 47为得数。

电路图如下:加上输入输出后:仿真图形为:1被乘数和乘数:2得数:由仿真图形可以看出,已成功制成了乘法计算器。

四.除法计算器这个实在是太难了,想了好久也没想到怎么设计,作业催的紧,就只好先不做了,请老师见谅,哈!以上就是四则计算器的数字电路设计与仿真。

计算机组成原理课程设计—超前进位加法器的设计资料

沈阳航空航天大学课程设计报告课程设计名称:计算机组成原理课程设计课程设计题目:超前进位加法器的设计院(系):计算机学院专业:班级:学号:姓名:指导教师:完成日期:沈阳航空航天大学课程设计报告目录第1章总体设计方案 (1)1.1设计原理 (1)1.2设计思路 (2)1.3设计环境 (3)第2章详细设计方案 (4)2.1顶层方案图的设计与实现 (4)2.1.1创建顶层图形设计文件 (4)2.1.2器件的选择与引脚锁定 (5)2.1.3编译、综合、适配 (7)2.2功能模块的设计与实现 (7)2.2四位超前进位加法器模块的设计与实现 (7)2.3仿真调试 (9)第3章编程下载与硬件测试 (11)3.1编程下载 (11)3.2硬件测试及结果分析 (11)参考文献 (13)附录(程序清单或电路原理图) (14)第1章总体设计方案1.1设计原理八位超前进位加法器,可以由2个四位超前进位加法器构成。

由第一个四位超前进位加法器的进位输出作为第二个超前进位加法器的进位输入即可实现八位超前进位加法器的设计。

超前进位产生电路是根据各位进位的形成条件来实现的。

只要满足下述条件,就可形成进位C1、C2、C3、C4。

所以:第一位的进位C1=X1*Y1+(X1+Y1)*C0第二位的进位C2=X2*Y2+(X2+Y2)*X1*Y1+(X2+Y2)(X1+Y1)C0第三位的进位C3=X3*Y3+(X3+Y3)X2*Y2+(X3+Y3)*(X2+Y2)*X1*Y1+(X3+Y3)(X2+Y2)(X1+Y1)*C0第四位的进位C4=X4*Y4+(X4+Y4)*X3*Y3+(X4+Y4)*(X3+Y3) * X2*Y2+(X4+Y4)(X3+Y3)(X2+Y2)*X1*Y1+(X4+Y4)(X3+Y3)(X2+Y2)(X1+Y1)*C0 下面引入进位传递函数Pi和进位产生函数Gi的概念。

它们定义为:Pi=Xi+YiGi=Xi*YiP1的意义是:当X1和Y1中有一个为1时,若有进位输入,则本位向高位传递此进位。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

设计示例4:32位先行进位加法器的设计

1、功能概述:

先行进位加法器是对普通的全加器进行改良而设计成的并行加法器,主要是针对普通全加器串联时互相进位产生的延迟进行了改良。

超前进位加法器是通过增加了一个不是十分复杂的逻辑电路来做到这点的。

设二进制加法器第i位为A i,B i,输出为S i,进位输入为C i,进位输出为C i+1,则有:S i=A i⊕B i⊕C i (1-1)

C i+1 =A i * B i+ A i *C i+ B i*C i =A i * B i+(A i+B i)* C i(1-2)

令G i = A i * B i , P i = A i+B i,则C i+1= G i+ P i *C i

当A i和B i都为1时,G i = 1,产生进位C i+1 = 1

当A i和B i有一个为1时,P i = 1,传递进位C i+1= C i

因此G i定义为进位产生信号,P i定义为进位传递信号。

G i的优先级比P i高,也就是说:当G i = 1时(当然此时也有P i = 1),无条件产生进位,而不管C i是多少;当G i=0而P i=1时,进位输出为C i,跟C i之前的逻辑有关。

下面推导4位超前进位加法器。

设4位加数和被加数为A和B,进位输入为C in,进位输出为C out,对于第i位的进位产生G i = A i·B i ,进位传递P i=A i+B i , i=0,1,2,3。

于是这各级进位输出,递归的展开Ci,有:

C0 = C in

C1=G0 + P0·C0

C2=G1 + P1·C1 = G1 + P1·G0 + P1·P0▪C0

C3=G2 + P2·C2 = G2 + P2·G1 + P2·P1·G0 + P2·P1·P0·C0

C4=G3 + P3·C3 = G3 + P3·G2 + P3·P2·G1 + P3·P2·P1·G0 + P3·P2·P1·P0·C0 (1-3)

C out=C4

由此可以看出,各级的进位彼此独立产生,只与输入数据Ai、Bi和Cin有关,将各级间的进位级联传播给去掉了,因此减小了进位产生的延迟。

每个等式与只有三级延迟的电路对应,第一级延迟对应进位产生信号和进位传递信号,后两级延迟对应上面的积之和。

实现上述逻辑表达式(1-3)的电路称为超前进位部件(Carry Lookahead Unit),也称为CLA 部件。

通过这种进位方式实现的加法器称为超前进位加法器。

因为各个进位是并行产生的,所以是一种并行进位加法器。

从公式(1-3)可知,更多位数的CLA部件只会增加逻辑门的输入端个数,而不会增加门的级数,因此,如果采用超前进位方式实现更多位的加法器,从理论上讲,门延迟不变。

但是由于CLA部件中连线数量和输入端个数的增多,使得电路中需要具有大驱动信号和大扇入门,这会大大增加门的延迟,起不到提高电路性能的作用。

因此更多位数的加

法器可通过4位CLA 部件和4位超前进位加法器来实现,如图2所示。

将式(1-3)中进位C 4的逻辑方程改写为:

C 4=G m0 + P m0·C 0 (1-4)

C4表示4位加法器的进位输出,Pm0、Gm0分别表示4位加法器的进位传递输出和进位产生输出,分别为:

P m0 = P 3·P 2·P 1·P 0

G m0 = G 3 + P 3·G 2 + P 3·P 2·G 1 + P 3·P 2·P 1·G 0

将式(1-4)应用于4个4位先行进位加法器,则有:

C 4=G m0 + P m0·C 0

C 8= G m1 + P m1·C 4 = G m1 + P m1·G m0 + P m1·P m0 ▪C 0

C 12= G m2 + P m2·C 8 = G m2 + P m2·G m1 + P m2·P m1·G m0 + P m2·P m1·P m0·C 0

C 16=G m3+P m3·C 12=G m3+P m3·G m2+P m3·P m2·G m1+P m3·P m2·P m1·G m0+P m3·P m2·P m1·P m0·C 0

(1-5)

比较式(1-3)和式(1-5),可以看出这两组进位逻辑表达式是类似的。

不过式(1-3)表示的是组内进位,式(1-5)表示的是组间的进位。

实现逻辑方程组(1-5)的电路称为成组先行进位部件。

图1a 为所设计的32位超前进位加法器的结构框图,该加法器采用三级超前进位加法器设计,组内和组间均采用超前进位。

由8个4位超前进位加法器与3个BCLA 部件构成。

图1b 为采用超前进位和进位选择实现的32位先行进位加法器结构图。

2、结构框图:

(a ) 32位超前进位加法器结构图

S S

(b ) 超前进位+进位选择实现结构 图1 32位先行进位加法器结构图

3、接口说明:

表1: 32位超前进位加法器接口信号说明表

4、4位超前进位加法器的设计(4bits CLA )

4.1 功能概述

产生进位信号(如图2a )、4位加法器的进位传递信号Px 以及4位加法器的进位产生信号Gx 。

P x = P 3·P 2·P 1·P 0

G x = G 3 + P 3·G 2 + P 3·P 2·G 1 + P 3·P 2·P 1·G 0

4.2 结构框图

P 0

G 0P 1G 1P 2G 2P 3G 3

(a ) 4位超前进位链

A 0

B 1

A 1

A 2

B 3

A 3

B 0

(b ) 4位超前进位加法器

图2 4位CLA 部件和4位超前进位加法器

5、设计电路源代码(部分)

//4bit carry lookahead unit

module cla_4(p,g,c_in,c,gx,px);

input[3:0] p,g;

input c_in;

output[4:1] c;

output gx,px;

assign c[1] = p[0]&c_in | g[0];

assign c[2] = p[1]&p[0]&c_in | p[1]&g[0] | g[1];

assign c[3] = p[2]&p[1]&p[0]&c_in | p[2]&p[1]&g[0] | p[2]&g[1] | g[2]; assign c[4] = px&c_in | gx;

assign px = p[3]&p[2]&p[1]&p[0];

assign gx = g[3] | p[3]&g[2] | p[3]&p[2]&g[1] | p[3]&p[2]&p[1]&g[0]; endmodule。