modelsim使用入门(VHDL_

Modelsim上机指导1

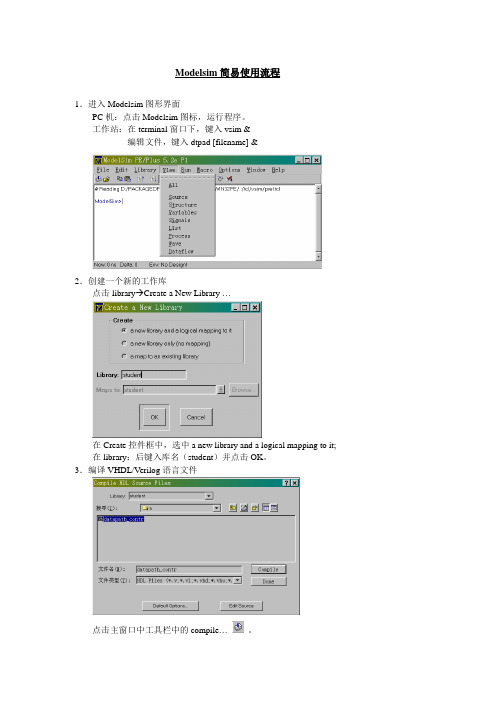

Modelsim简易使用流程1.进入Modelsim图形界面PC机:点击Modelsim图标,运行程序。

工作站:在terminal窗口下,键入vsim &编辑文件,键入dtpad [filename] &2.创建一个新的工作库点击library Create a New Library …在Create控件框中,选中a new library and a logical mapping to it;在library:后键入库名(student)并点击OK。

3.编译VHDL/Verilog语言文件点击主窗口中工具栏中的compile…。

A.选择编译文件在library后的选择控件中选择工作库(student),选中要编译的VHDL/Verilog文件。

B.选择VHDL-87/93标准点击Default Options…按钮,在弹出的compiler options窗口中选中Use 1993 Language Syntax,即使用VHDL-93标准编译文件。

C.编译文件在Compile HDL Source Files窗口中点击compile按钮。

编译的结果显示在主窗口中,warning、error信息分别以蓝色和红色字符显示。

D.修改VHDL/Verilog文件在Compile HDL Source Files窗口中点击Edit Source按钮,在弹出的窗口中修改文件。

注:如果该文件在仿真条件下被打开,只读属性被设置,在菜单Edit中点击Read Only,去除只读属性后,进行修改。

4.仿真A.载入设计点击主窗口的Load Design按钮。

选择要仿真的实体名、结构体名或配置名,点击Load按钮。

在Modelsim5.5a中,可以直接双击主窗口library标签中对应的实体名、结构体名或配置名。

B.调试点击主窗口的View→Structure;在弹出的Structure窗口中选择要观察的实体名。

modelsim使用指南.

执行仿真 (UI)

选择 timesteps数量就 可以执行仿真

Restart – 重装任何已改动 的设计元素并把仿真时间设 为零 COM) restart

38

run 命令参数

可选的参数

– -<timesteps> <time_unit> • 指定运行的timesteps数量 • 单位可用{fs, ps, ns, ms, sec}

用户界面 (UI)

– 能接受菜单输入和命令行输入 – 课程主要讨论

批处理模式

– 从DOS或UNIX命令行运行批处理文件 – 不讨论

13

基本仿真步骤

1 Ö 建立库

2 Ö 映射库到物理目录

3 Ö 编译源代码 - 所有的HDL代码必须被编译 - Verilog和VHDL是不同的

4 Ö 启动仿真器 5 Ö 执行仿真

UI) Design -> Compile Cmd) vlog -work <library_name> <file1>.v <file2>.v

– 文件按出现的顺序被编译 – 文件的顺序或者编辑的顺序不重要

支持增量式编译 缺省编译到work库

– 例如. vlog my_design.v

– -sdfmin | -sdftyp | -sdfmax <instance>=<sdf_filename> • 注释SDF文件 • 可选项 • 使用实例名也是可选项; 如果没有使用, SDF用于顶级

36

5 Ö 执行仿真

UI) Run COM) run <time_step> <time_units> 按timesteps指定的时间长度执行仿真

debussy和modelsim协同仿真(VHDL)

debussy和modelsim协同仿真(VHDL)1、编辑modelsim根目录下的modelsim.ini文件,将; Veriuser = veriuser.sl 更换为Veriuser = novas_fli.dll。

2、将C:\Novas\Debussy\share\PLI\modelsim_fli54\WINNT下的novas_fli.dll 拷贝至C:\Modeltech_6.1d\win32中3、将C:\Novas\Debussy\share\PLI\modelsim_fli54\WINNT下的novas.vhd拷贝至工程所在目录4、打开modelsim,在工程所在目录新建一个novas的LIB,然后编译novas.vhd文件。

5、在testbentch中增加library novas;use novas.pkg.all;6、在testbentch中添加debussy_debug:processbeginfsdbDumpfile("**.fsdb");fsdbDumpvars(0,"顶层文件名(有testbench的话即为testbench名)");wait;end process debussy_debug;7、编译整个工程,然后仿真8、打开debussy, import design加载文件,设置好顶层文件,打开nWARE,加入信号即可为了更加方便的使用DEBUSSY,我们可以编写DO文件来达到这一目的:1、先新建dc16_tca目录。

比如在E:/WORK/TEMP里新建该目录,把源程序都放在dc16_tca/soure里头。

2、编写tca.do文件:下面是以TCA为例说明一下这个步骤:tca.do:#start#建立并编译novas库vlib novasvmap novas novasvcom -work novas D:/WORK/temp/dc16_TCA/source/novas.vhd#建立并编译work库vlib workvcom -work work d:/work/temp/dc16_tca/source/dc16_constant_def.vhdvcom -work work d:/work/temp/dc16_tca/source/dc16_tca.vhdvcom -work work d:/work/temp/dc16_tca/source/dc16_tca_tb.vhdvsim dc16_tca_tb#仿真运行时间run 10000usquit#end3、然后在dos界面先进入到dc16_tca目录里,比如E:/WORK/TEMP/dc16_tca然后再输入>c:\modeltech_6.1b\win32/vsim -c -do tca.do这里假设modelsim装在C盘个人感觉modelsim的仿真速度用DO文件的方式比用modelsim的GUI方式要快很多。

modelsim的VHDL仿真

modelsim的VHDL仿真前⾯⽤过vivado⾃带的仿真软件,我这个仿真新⼿发现它不能仿真signal信号,所以改⽤modelsim进⾏仿真,虽然经历了⼀些波折,总归仿出结果了,下⾯记录下仿真过程作为备忘:⾸先新建project ,添加主⽂件.vhd和testbench.vhd,全部编译,如下图即是编译成功:⼀定要在如下library⾥点击仿真,不然可能会出现信号缺失的情况:然后在work下⾯找到testbench中的architecture,右击,simulation:这时⾃动跳到波形界⾯,此时在instance单元左击testbench就会在objects看到输⼊输出信号,但是没有内部型号:左击instance中uut模块就可以看到主⽂件内的signal信号和定义的各种变量常量:这时,就可以将需要的信号抓到观测区,选中需要的信号,右击,add wave:带观测区如下:这时就是最后⼀步了,设置仿真时间点击显⽰,就是点击仿真时间右边的那个run(开始忘记这⼀步,发现总是看不见波形,恼⽕!),其实直接在命令⾏输⼊run也是可以的。

此时就可以看到波形咯!最后放下我两个程序吧,⼀个mystate,⼀个mystate_tb是状态机学习的程序:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;--------------------------------------------------------ENTITY mystate ISPORT(A,clk,rst: IN STD_LOGIC;output_state: OUT STD_LOGIC);END mystate;--------------------------------------------------------ARCHITECTURE rtl OF mystate ISCONSTANT s0: STD_LOGIC_VECTOR(1downto0):="00";CONSTANT s1: STD_LOGIC_VECTOR(1DOWNTO0):="01";CONSTANT S2: STD_LOGIC_VECTOR(1DOWNTO0):="11";SIGNAL current_state: STD_LOGIC_VECTOR(1DOWNTO0);SIGNAL next_state: STD_LOGIC_VECTOR(1DOWNTO0);BEGINPROCESS(clk,rst)BEGINIF(rst='1') THENcurrent_state<=s0;ELSIF(clk'EVENT AND clk='1') THENcurrent_state<=next_state;END IF;END PROCESS;PROCESS(current_state,A)BEGINCASE current_state ISWHEN s0=>IF(A='0') THENnext_state<=s0;ELSEnext_state<=s1;END IF;WHEN s1=>IF(A='0') THENnext_state<=s2;ELSEnext_state<=s1;END IF;WHEN s2=>next_state<=s0;WHEN OTHERS=>NULL;END CASE;END PROCESS;PROCESS(current_state,A)BEGINCASE current_state ISWHEN s0=>IF(A='0') THENoutput_state<='0';ELSEoutput_state<='1';END IF;WHEN s1=>IF(A='0') THENoutput_state<='1';ELSEoutput_state<='0';END IF;WHEN s2=>IF(A='0') THENoutput_state<='0';ELSEoutput_state<='1';END IF;WHEN OTHERS=>NULL;END CASE;END PROCESS;END rtl;library IEEE;use IEEE.Std_logic_1164.all;use IEEE.Numeric_Std.all;entity mystate_tb isend;architecture bench of mystate_tb is component mystatePORT(A,clk,rst: IN STD_LOGIC;output_state: OUT STD_LOGIC);end component;signal A,clk,rst: STD_LOGIC;signal output_state: STD_LOGIC;constant clock_period: time := 10 ns;signal stop_the_clock: boolean;beginuut: mystate port map ( A => A,clk => clk,rst => rst,output_state => output_state );stimulus: processbeginA<='0';wait for 20ns;A<='1';wait for 20ns;A<='0';wait for 20ns;A<='0';wait;stop_the_clock <= true;wait;end process;clocking: processbeginwhile not stop_the_clock loopclk <= '0', '1'after clock_period / 2;wait for clock_period;end loop;wait;end process;resetmy:PROCESSBEGINrst<='1';wait for30 ns;rst<='0';wait;END PROCESS;end;。

modelsim使用教程

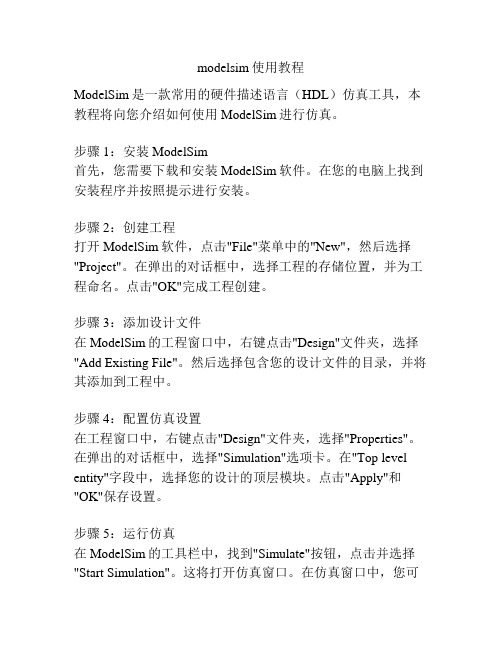

modelsim使用教程ModelSim是一款常用的硬件描述语言(HDL)仿真工具,本教程将向您介绍如何使用ModelSim进行仿真。

步骤1:安装ModelSim首先,您需要下载和安装ModelSim软件。

在您的电脑上找到安装程序并按照提示进行安装。

步骤2:创建工程打开ModelSim软件,点击"File"菜单中的"New",然后选择"Project"。

在弹出的对话框中,选择工程的存储位置,并为工程命名。

点击"OK"完成工程创建。

步骤3:添加设计文件在ModelSim的工程窗口中,右键点击"Design"文件夹,选择"Add Existing File"。

然后选择包含您的设计文件的目录,并将其添加到工程中。

步骤4:配置仿真设置在工程窗口中,右键点击"Design"文件夹,选择"Properties"。

在弹出的对话框中,选择"Simulation"选项卡。

在"Top level entity"字段中,选择您的设计的顶层模块。

点击"Apply"和"OK"保存设置。

步骤5:运行仿真在ModelSim的工具栏中,找到"Simulate"按钮,点击并选择"Start Simulation"。

这将打开仿真窗口。

在仿真窗口中,您可以使用不同的命令来控制和观察设计的行为。

步骤6:查看仿真结果您可以在仿真窗口中查看信号波形、调试设计并分析仿真结果。

在仿真窗口的菜单栏中,您可以找到一些常用的查看和分析工具,如波形浏览器、信号分析器等。

步骤7:结束仿真当您完成仿真时,可以选择在仿真窗口的菜单栏中找到"Simulate"按钮,并选择"End Simulation"以结束仿真。

modelsim的详细使用方法

一、简介ModelSim是一款由美国Mentor Graphics公司推出的集成电路仿真软件,广泛应用于数字电路和系统设计领域。

它提供了强大的仿真和验证功能,能够帮助工程师快速高效地进行电路设计与验证工作。

本文将详细介绍ModelSim的使用方法,以帮助读者更好地掌握这一工具的操作技巧。

二、安装与配置1. 下载ModelSim安装包,并解压到指定目录2. 打开终端,进入ModelSim安装目录,执行安装命令3. 安装完成后,配置环境变量,以便在任何目录下都能够调用ModelSim程序4. 打开ModelSim,进行软件注册和授权,确保软件可以正常运行三、工程创建与管理1. 新建工程:在ModelSim主界面点击“File” -> “New” -> “Project”,输入工程名称和存储路径,选择工程类型和目标设备,点击“OK”完成工程创建2. 添加文件:在工程目录下右键点击“Add Existing”,选择要添加的源文件,点击“OK”完成文件添加3. 管理工程:在ModelSim中可以方便地对工程进行管理,包括文件的增删改查以及工程参数的设置等四、代码编写与编辑1. 在ModelSim中支持Verilog、VHDL等多种硬件描述语言的编写和编辑2. 在ModelSim主界面点击“File” -> “New” -> “File”,选择要新建的文件类型和存储位置,输入文件名称,点击“OK”完成文件创建3. 在编辑器中进行代码编写,支持代码高亮、自动缩进、语法检查等功能4. 保存代码并进行语法检查,确保代码符合规范,没有错误五、仿真与调试1. 编译工程:在ModelSim中进行代码编译,生成仿真所需的可执行文件2. 设置仿真参数:在“Simulation”菜单下选择“S tart Simulation”,设置仿真时钟周期、输入信号等参数3. 运行仿真:点击“Run”按钮,ModelSim将开始对设计进行仿真,同时显示波形图和仿真结果4. 调试设计:在仿真过程中,可以通过波形图和仿真控制面板对设计进行调试,查找并解决可能存在的逻辑错误六、波形查看与分析1. 查看波形:在仿真过程中,ModelSim会生成相应的波形文件,用户可以通过“Wave”菜单查看波形并进行波形分析2. 波形操作:支持波形的放大、缩小、平移、选中等操作,方便用户对波形进行分析和观察3. 波形保存:用户可以将波形结果保存为图片或文本文件,以便日后查阅和分析七、性能优化与验证1. 时序优化:在设计仿真过程中,可以通过观察波形和性能分析结果,对设计进行优化,提高设计的时序性能2. 逻辑验证:通过对仿真的结果进行逻辑验证,确保设计符合预期的逻辑功能3. 时序验证:对设计的时序性能进行验证,确保信号传输和时钟同步的正确性八、项目输出与文档整理1. 输出结果:在仿真和验证完成后,可以将仿真结果、波形图和性能分析结果输出为文本文件或图片,方便后续的文档整理和报告撰写2. 结果分析:对仿真结果和验证结果进行详细的分析,确定设计的性能和功能是否符合设计要求3. 文档整理:根据仿真和验证结果,进行文档整理和报告撰写,为后续的设计和优化工作提供参考九、总结与展望ModelSim作为一款专业的集成电路仿真软件,具有着强大的功能和丰富的特性,可以帮助工程师进行电路设计与验证工作。

modelsim使用方法

modelsim使用方法ModelSim 是一种功能强大的硬件描述语言 (HDL) 模拟工具,支持VHDL和Verilog,可用于设计和验证数字系统。

本文将介绍如何使用ModelSim。

**安装 ModelSim****创建项目**在启动 ModelSim 后,首先需要创建一个新的项目。

选择 "File" 菜单,然后选择 "New" -> "Project"。

在打开的对话框中,选择项目的文件夹和项目名称,然后点击 "OK"。

**添加设计文件和测试文件**在项目中,您需要添加设计文件和测试文件。

选择 "Project" 菜单,然后选择 "Add to Project" -> "Add Files". 在打开的对话框中,选择您的设计文件 (VHDL 或 Verilog) 和测试文件,然后点击 "OK"。

**设置仿真**在编译代码之后,下一步是设置仿真选项。

选择 "Simulate" 菜单,然后选择 "Start Simulation"。

在打开的对话框中,选择您的顶层模块。

您还可以选择以 GUI 模式还是批处理模式运行仿真。

在设置仿真之前,您可以添加信号波形文件以在仿真过程中显示波形。

选择 "Simulate" -> "Wave" -> "Add Waveform". 然后,选择信号波形文件 (.do 或 .vcd),并点击 "OK"。

**运行仿真**设置仿真选项后,您可以开始执行仿真。

通过选择 "Simulate" -> "Run",可以运行单步或连续仿真。

Modelsim详细使用教程

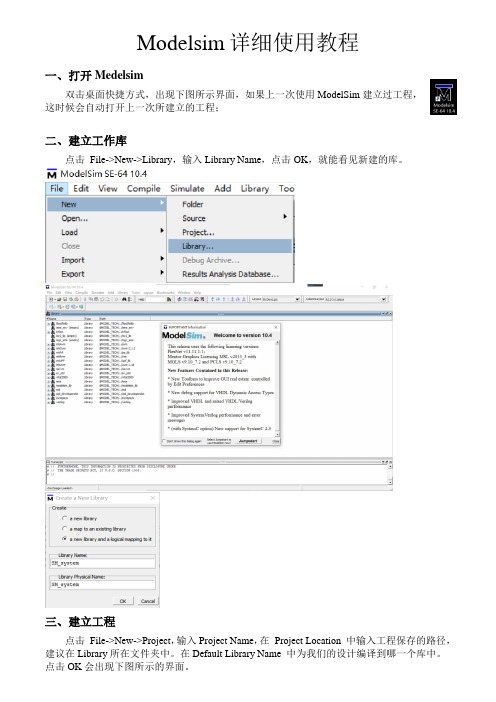

Modelsim详细使用教程一、打开Medelsim双击桌面快捷方式,出现下图所示界面,如果上一次使用ModelSim建立过工程,这时候会自动打开上一次所建立的工程;二、建立工作库点击File->New->Library,输入Library Name,点击OK,就能看见新建的库。

三、建立工程点击File->New->Project,输入Project Name,在Project Location 中输入工程保存的路径,建议在Library所在文件夹中。

在Default Library Name 中为我们的设计编译到哪一个库中。

点击OK会出现下图所示的界面。

四、为工程添加文件Create New File 为工程添加新建的文件;Add Existing File为工程添加已经存在的文件;Create Simulation为工程添加仿真;Create New Folder为工程添加新的目录。

这里我们点击Create New File,来写仿真代码。

输入File Name,再输入文件类型为Verilog (默认为VHDL,Modelsim也可以仿真System Verilog代码),Top Level表示文件在刚才所设定的工程路径下。

点击OK,并点击Close关闭Add items to the Project窗口。

这时候在Workspace窗口中出现了Project选项卡,里面有8_11.v,其状态栏有一个问号,表示未编译,双击该文件,这时候出现8_11.v的编辑窗口,可以输入我们的Verilog代码。

五、编写Verilog代码写完代码后,不能马上就编译,要先File->Save保存,否则,编译无效。

然后选择Compile->Compile All。

Transcript脚本窗口出现一行绿色字体Compile of 8_11.v was successful. 说明文件编译成功,并且该文件的状态栏显示绿色的对号。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

modelsim使用实例(VHDL)

标签: modelsim仿真testbench FPGA

看了几天的modelsim以及如何在quartusII中调用,浏览了N个网页,尝试了N次,......终于初步完成。

下面是入门部分介绍。

modelsim是专业的仿真软件,仿真运行速度比同类的其他仿真软件都要快很多。

Quartus 自己都不再做仿真器了,普遍使用modelsim,自有其缘由。

这里用的是modelsim-altera(6.6d)版本,与quartus II 11.0搭配。

据说Altera公司推出的Quartus软件不同版本对应不同的modelsim,相互之间不兼容。

某些功能齐全的modelsim版本可以进行两种语言的混合编程, modelsim-altera只能支持一种语言进行编程(VHDL或者Verilog选其一)。

1、新建工程

打开modelsim-->file-->new-->project 新建工程,输入工程名,文件存放路径后(不可直接放在某盘下,必须放入文件夹中),进入下一步。

在主体窗口下方出现project标签。

见下图。

2、新建文件

--create new file:输入名称div10,选择语言VHDL --关闭对话框

新的工程文件将会在工程窗口出现。

3、写入源程序(VHDL)

双击div10.vhd,打开文本编辑器。

实例代码如下(一个十分频的VHDL源代码):library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

use ieee.std_logic_unsigned.all;

entity div10 is --实体要与工程名相同 port(clk :in std_logic;

div :out std_logic );

end div10;

architecture behav of div10 is

signal temp :std_logic:='0';

signal count :std_logic_vector(2 downto 0):="000";

begin

process(clk)

begin

if(clk'event and clk='1') then

if(count="100") then

count<=(others=>'0');

temp<=not temp;

else

count<=count+1;

end if;

end if;

end process;

div<=temp;

end behav;

4、写testbench

modelsim单独使用时需要自己写testbench,输入时钟,给测试电路加以激励源以驱动电路。

再次新建一个VHDL文件,即写入testbench,采用50MHZ时钟频率命名div10_tb library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

use ieee.std_logic_unsigned.all;

entity div10_tb is

end div10_tb;

architecture one of div10_tb is

component div10 is

port(clk :in std_logic;

div :out std_logic);

end component;

signal clk :std_logic:='0';

signal div :std_logic:='0';

constant clk_period:time:=20 ns;

begin

u1:

div10 port map

(clk=>clk,div=>div);

process

begin

wait for clk_period/2;

clk<='1';

wait for clk_period/2;

clk<='0';

end process;

end;

保存为div10_tb.vhd文件,见图下。

如果新建的testbench文件不在工程中,则需要将它添加过来。

在workspace中右击--add to project--existing file--选择所要添加的文件div10_tb.

全部添加完成后,全部编译一次compile all,见下图。

5、开始仿真

--在命令行中输入vsim work.div10_tb 对生成的testbench进行仿真

--输入view wave 查看波形

--输入 add wave -hex *添加信号到波形图 hex只用十六进制观看注意 hex与*之间有个空格。

--输入run 3us 观察波形

这样即完成波形的仿真。