任意波形发生器方案

基于DSP技术的任意波形发生器的设计与实现

Um ax、U i m n、Qm ax、Qm i n。

对于Um ax、Um i n的整定,可参照当地的电网运行规程,设定合格电压的上下限。

例如:如果当地10k V的合格电压的范围为9.8~10.7kV,因此Um ax设定为10.7,Um i n设定为10.0,对于10k V因馈线长网损较大的特殊情况,可将Um i n适当增大。

4.1.2 无功Qm ax、Qm in的整定Qm ax与Qm i n的整定比较复杂,因为Q与负荷大小密切相关。

对于Qm ax、Qm i n的整定,应先根据当地电网对于功率因数的运行规定,确定COS m ax及CO S m i n。

例如: COS m ax规程允许0.98,COS m in规程允许0.9。

现假设对于一台两卷变压器,容量为50000kVA。

现考虑该台变压器运行在额定负荷的80%情况下,则可得出Qm ax及Qm i n在80%的额定负荷条件下的值:Qm ax=80%*S* (1-CO S m i n*COS m in=17436kV arQm i n=80%*S* (1-CO S m ax*COS m ax=7960k V ar因为负荷是变化的,因此Qm ax与Qm in随着不同的负荷变化而变化。

因此VQ C软件一般都要求分时段执行定值。

所以可根据当地的负荷变化规律,在不同的时段整定不同的Qm ax与Qm i n大小。

本装置有可分为5个时段。

4.2 投退一组并联电容器对电压的变化率 U确定投一组并联电容器对母线电压的影响,通常比较困难。

因为负荷受时间、季节的变化而不同,因此要精确整定是比较困难的。

可以利用综合自动化系统的遥测数据来确定此定值。

4.3 投一组并联电容器对无功的变化率对于一组并联电容器,其出厂铭牌都会注明其容量,例如对于某电容器组,其参数为5010k V ar,则其容量可直接作为投一组并联电容器对无功的变化大小,例如对于上述电容,则其对无功的变化率为5010k V ar。

基于FPGA的任意波形发生器设计

典型的模拟滤波器有巴特沃斯 (Butterworth) 滤波器、切比雪夫 (Chcbyshcv) 滤波器、贝塞尔(Scsscl) 滤波器和椭I 圜(Ellipsc) 滤波器。

这几种低通滤波器都有各自的幅频特性。通带与阻带之间称为过渡带,过渡 带越窄,说明滤波器的选择性越好。巴特沃斯滤波器的响应最为平坦,它的 通带内没有波纹,在靠近零频处,有最平坦通带,趋向阻带时衰减单调增大, 缺点是从通带到阻带的过渡带最宽,对于带外干扰信号的衰减作用最弱,过 渡带不够陡峭。切比雪夫滤波器在通带内衰减在零值和一个土限值之间做等 起伏变化,阻带内衰减单调增大,通带或组带有波动,但过渡带比较陡峭。 贝塞尔滤波器通带内有较好的线性相位持性。椭圆函数滤波器不仅通带内有 起伏,阻带内也有起伏,而且过渡带陡峭。

? 单片机主要完成以下三个方向的任务:

(1) 根据键盘设置的波形和频率,完成波形的选择、编辑,并产生相应的 频率控制字送FPGA 。

(2) 将输出信号的频率送数码管显示。

(3) 与USB 接口芯片实现USB 接口电路并与上位PC 机通信。

主要要完成的工作:

? 1)基于FPGA 的DDS 实现 首先熟悉Quartus II 开发环境,其次对确定FPGA

工艺,无需另行架构,波形稳定度与准确度都比较高,有 理想的波形质量。但是,专用的DDS 芯片的数据表都已 经固化在芯片里,因此对于不同的应用其灵活性相对较, 无法灵活的实现任意波形的输出,同时DDS 芯片加单片 机的设计模式使硬件电路相对复杂。

基于DDS技术选择的实施方案

? 方案二: 基于FPGA 实现DDS 功能,通过单片机实现控制。此方 案的核心在于FPGA 的设计实现逻辑功能,通过对存储器 查表后输出信号,由相连接的数模转换器转换为要求的波 形。单片机作为控制器,易于控制与调试。

高速任意波形发生器的设计

p o o a o h e e ao a e n d gtl f q e c y t e i t c n q e h a d r ic i o l u i n ot r r p s l fr t e g n r tr b s d o i i r u n y s n h ss e h iu . e h r wa e c ru t f al n t a d s f a e r s wa e d sg o e i n fr MCU ae d s u s d i eal h r p s li c a a trs c o ta y w v fr ,ae y s r d wa e r d t r ic ce t f s d a eo m s fl —t e v f m aa, i i e o o s l l cr a i u t n O o i e e e t c l r i a d S n,a d tu f ih p a t a au s mp i cc n h so g rc i l l e . h c v

Ke r s r i ay wa e r g n r tr ii lf q e c y te i ;w v fr e ea o i u t i e i ut d s n; y wo d :ab t r v f m e e ao ;d gt e u n y s n h s r o a r s a eo i g n r tr c r i;F l rc r i e i n c t c g

dds任意波形发生器设计.

目录1.1 DDS的基本结构 (2)1.2 DDS的工作特点 (4)1.3 DDS的技术指标 (5)1.4实现方案 (7)1.5硬件结构说明 (7)1.6设计过程 (8)1.7频率测量 (18)1.8误差与杂散分析 (19)DDS(Direct Digital Synthesis)的概念首先由美国学者J.Tierncy,C.M.Radar和B.Gold在1971年提出,但限于当时的技术和工艺水平,DDS技术仅仅限于理论研究,而没有应用到实际中去。

近20年来,随着VLSI(Very Large Scale Integration),FPGA(Field Programmable Gates Array)以及DSP(Digital Signal Processing)的发展,这种结构独特的频率合成技术得到了飞速发展。

目前该技术已经被广泛用于接收机本振、信号发生器、通信系统、雷达系统等相关领域中。

1.1 DDS的基本结构DDS(Direct Digital Synthesis)技术设计思想是基于数值计算信号波形的抽样值来实现频率合成的。

它包括数字器件与模拟器件两部分,主要有相位累加器、ROM波形查询表、数模转换器组成。

其基本框图如下。

(1)相位累加器是DDS的核心部分。

一般是由数字全加器和数字寄存器组成,实现相位累加。

如下图所示。

一般DDS的累加器都采用二进制,线性数字信号通过相位累加器实现逐级的累加。

假设累加器字长为N,频率控制字为K,控制时钟频率为f c,系统在同一个时钟下工作,每个时钟周期加法器做一次累加计算。

因为累加器的满偏是2N,所以累加一次,相当于做一次2N模的运算。

得到的和作为相位值。

(2)波形函数存储在ROM中。

根据累加器输出的相位值,作为地址,寻找存储在ROM中的波形函数的幅度量化值,完成相位到幅值的转换,输出相对应的序列。

(3)数模转换器DAC是DDS中的重要部分。

经过查表以后得到的是离散的脉冲信号,通过数模转换器将转换成为连续平滑的信号。

任意波形发生器方案

任意波形发生器的设计方案12电信1 张晓航 1200301108 一,选择课题:电子测量仪器设计——任意波形发生器设计二,设计要求:能产生方波、三角波、正弦波、锯齿波信号。

主要技术指标:(1)输出频率范围100HZ~1KHZ、1~10KHZ(2)输出电压:方波UPP=6V,三角波UPP=6V,正弦波UPP>1V,锯齿波UPP=6V。

三,仪器仪表清单:1.直流稳压电源 1台 2.双踪示波器 2台3.运放741(LM324n)*3 4.二极管 1N4154*2 1N4680*25.电位器50K*2 1K*1 6.电容1μF 47nF *17.电阻 100k 10k 5k 3k 4k 96k若干 8.面包板 1块9.剪刀1把 10.仪器探头线 2根11.电源线若干四,设计考虑因素:信号发生器可以通过多种方法设计产生,但是考虑到如果使用芯片去完成可能所需要的成本比较高,但如果用单片机等则设计太复杂,还需要嵌入相应代码,有点大材小用,综合多方面的因素考虑该方案是可行性比较高,性价比比较高的一种方案,同时,能够让我对于一些专业基础知识有了更深的了解。

元器件可重复利用,符合现在可持续发展的绿色思想。

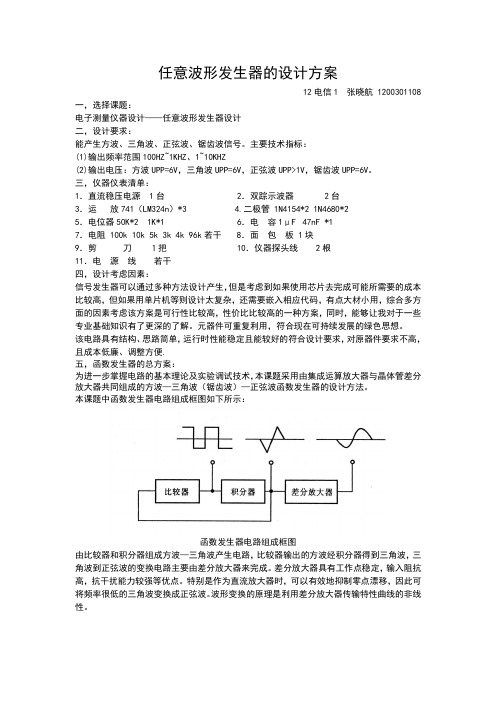

该电路具有结构、思路简单,运行时性能稳定且能较好的符合设计要求,对原器件要求不高,且成本低廉、调整方便.五,函数发生器的总方案:为进一步掌握电路的基本理论及实验调试技术,本课题采用由集成运算放大器与晶体管差分放大器共同组成的方波—三角波(锯齿波)—正弦波函数发生器的设计方法。

本课题中函数发生器电路组成框图如下所示:函数发生器电路组成框图由比较器和积分器组成方波—三角波产生电路,比较器输出的方波经积分器得到三角波,三角波到正弦波的变换电路主要由差分放大器来完成。

差分放大器具有工作点稳定,输入阻抗高,抗干扰能力较强等优点。

特别是作为直流放大器时,可以有效地抑制零点漂移,因此可将频率很低的三角波变换成正弦波。

波形变换的原理是利用差分放大器传输特性曲线的非线性。

任意波形发生器设计

任意波形发生器设计一、设计目标和需求分析在进行任意波形发生器设计之前,首先需要明确设计目标和需求。

根据实际应用需求,我们需要设计一种具有以下特点的任意波形发生器:1.多种波形形状:能够产生包括正弦波、方波、三角波、锯齿波等多种波形形状的输出信号。

2.高精度输出:能够提供稳定、精确的波形输出,满足对波形频率、幅度、相位等参数的要求。

3.宽频率范围:能够在较宽的频率范围内产生波形信号,适应不同应用场景的需求。

4.灵活性和操作便捷:具备灵活的参数调节和操作界面,方便用户配置所需波形信号。

二、电路设计和构成基于以上需求,我们可以采用数字/模拟混合电路来设计任意波形发生器。

整体电路结构包括信号发生器、波形调节电路、滤波器、放大器和输出接口等几大部分。

1.信号发生器:信号发生器是生成基本信号的核心部分。

可以采用数字逻辑电路,通过编程控制产生不同形状的基本波形,例如正弦波、方波、三角波、锯齿波等。

可以使用存储器来存储基本波形的采样点,并通过数字模拟转换器(DAC)将数字信号转换为模拟信号。

2.波形调节电路:波形调节电路用于调整波形的频率、幅度和相位等参数。

通过调整振荡电路中的电阻、电容或电感等元件,实现对基本波形的变换和调节。

可以设计多种电路模块来完成这一任务,例如可变电容二极管电路、可调电阻电路等。

3.滤波器:滤波器用于对产生的波形信号进行滤波处理,除去高频或低频的杂散分量,保留所需频率范围内的信号。

可以采用各种类型的滤波器电路,例如RC滤波器、有源滤波器或数字滤波器等。

4.放大器:放大器用于增强波形信号的幅度,确保输出的信号具备足够的驱动能力,可以驱动接收端电路。

可以采用运放等放大电路,根据需要选择合适的增益。

5.输出接口:输出接口用于将产生的波形信号输出给外部设备。

可以设计多种类型的输出接口,例如模拟输出接口(BNC接口)、数字输出接口(USB接口)等,方便用户接入不同类型的设备。

三、实现方法和关键技术在设计任意波形发生器时,需要考虑以下关键技术和实现方法:1.数字信号处理技术:通过数字信号处理技术,实现对基本波形的生成、存储和输出。

频率可变的任意波形发生器的设计

深圳大学实验报告课程名称:Verilog数字系统设计教程实验工程名称:频率可变任意波形发生器的设计学院:电子科学与技术专业:微电子指导教师:刘春平报告人:潘志钟学号: 2007160051班级: 07级微电1班实验时间:2009-12-8 ~ 2010-1-11实验报告提交时间:2010-1-4教务处制(·····这里可加前言摘要之类的东西····自己想来写···)1设计原理DDS 是一种把数字信号通过数/模转换器转换成模拟信号的合成技术。

直接数字频率合成技术(DDS )是一种以采样定理为基础的全数字化频率合成波形的方法。

DDS 频率合成器主要由频率寄存器、相位寄存器(需要时可加入)、相位累加器、波形存储表(ROM ),DAC 转换器和模拟低通滤波器(LPF )等组成。

在系统时钟(SYSCLK )输入一定的情况下,频率寄存器中的频率控制字决定系统输出频率,而相位累加器的位数决定了系统频率分辨率。

总体设计方案及其原理说明:图 1-1 系统总体设计方案相位累加器由N 位加法器和N 位累加寄存器级联而成。

每当系统时钟SYSCLK 产生一个上升沿,N位加法器将频率寄存器中的频率控制字(FREQDAT A)与上一个系统时钟累加寄存器输出的累加相位数据相加,相加后的结果送累加寄存器。

这样在系统时钟的作用下,不断对频率控制字进行线性相位累加,相位累加器的溢出率就是DDS任意波形发生器的输出频率。

2设计与实现实际上DDS就是通过改变地址增量来达到控制输出频率的目的,而波形存储器(ROM)是以相位为地址,存有一个或多个按相位划分幅值的波形幅度信息。

参考频率f_clk为整个合成器的工作频率,输入的频率字保存在频率寄存器中,经N位相位累加器,累加一次,相位步进增加,经过内部ROM波形表得到相应的幅度值,经过D/A转换和低通滤波器得到合成的波形(数模转换在这里不作要求)。

DDS任意波形发生器

基于DDS技术的任意波形发生器研究与设计1 DDS概述1.1 DDS基本原理直接数字合成技术(Direet Digital Synthesis,简称DDS)是建立在采样定理基础上,首先对需要产生的波形进行采样,将采样值数字化后存入存储器作为查找表,然后通过查表读取数据,再经D/A转换器转换为模拟量,将保存的波形重新合成出来。

DDS基本原理框图如图1所示。

由图l看出,除了滤波器(LPF)之外,DDS系统都是以数字集成电路实现,因此DDS 系统易于集成和小型化。

DDS系统的参考时钟源通常是一个具有高稳定性的晶体振荡器,整个系统的各个组成部分提供同步时钟。

频率字(FSW)实际上是相位增量值(二进制编码),作为相位累加器的累加值。

相位累加器在每一个参考时钟脉冲输入时,累加一次频率字,其输出相应增加一个步长的相位增量。

由于相位累加器的输出连接在波形存储器(ROM)的地址线上,因此其输出的改变就相当于查表。

这样就可把存储在波形存储器内的波形抽样值(二进制编码)经查找表查出。

ROM的输出送到D/A转换器,经D/A转换器转换成模拟量输出。

1.2 DDS的基本参数及其计算在系统时钟脉冲的作用下,相位累加器不停累加,即不停查表,把波形数据送到D/A 转换器转换成模拟量输出,从而合成波形。

滤波器则进一步平滑D/A转换器输出的近似正弦波的锯齿阶梯波,同时衰减不必要的杂散信号。

设频率字(FSW)的值为d,系统时钟频率为f,相位累加器的字长为N,则系统的输出频率为:2 任意波形发生器的设计方案基于DDS技术的任意波形发生器主要由微处理器控制模块、键盘与显示模块、DDS通道的FPGA实现模块、D/A转换模块以及滤波器模块组成。

同时片外扩展了4 KB程序存储器SRAM和6 KB数据存储器ROM,分别用于存储波形抽样数据和3种标准输出波形抽样数据。

本系统设计原理如图2所示。

2.1 微处理器控制模块采用AT89C5l单片机完成数据处理和控制其他电路工作。

DDS任意波形发生器波形数据生成及传输接口设计

签舫 名开 :

导师签 名:

日介 日 期 介对 少

第一章 绪论

第一章 绪论

波形发生器概 述 波形发生器即通常所说的信号发生 器是一种常用的 信号源, 广泛应用于电 子 电 路、自 动控制和科学试验领域,是 一种为电 子测量工作提供符合严格技术要求 的电 信号 设备, 和示波器、电 压表、 频率计等仪器一样是最普通、最基本也是应 用最广泛的电 子仪器之一, 几乎所有电 参量的 测量都要用到 波形发生器。

中的数字部分及该部分与单片机的接 口进行 了设计 ,其中的波形 RM是任意波形 A

数据的接收 端。 在此基础上,使 用当前 流行的虚 拟仪 器设计语言 L wn叨 /v b d a i 5Cl 作为开发工具,利用计算机强大的计 算显示 功能, 设计实现任意波形发 生器的 操

作面板 。通过在操作面板上选择 正弦波、方波 、三角波 、锯齿波等常规波形或手 动绘制测试需求的任意波形 ,并 设置波 形参数 ,产 生符合接 收要求 的波形数据 , 进而控制硬件模块产 ቤተ መጻሕፍቲ ባይዱ相应 的波 形信号。产生手 动绘制任 意波 形数据 是设计过程 中的重点和难点,集 中体现 了任意波形发生器的 “ 任意性” 。在众多 的计算机接口

ABSTR ACT

户 t 了节 vf n ee o A G sn oh o to l n 刀 es 厄e n Gn ar W ioe t m sp u i tm ti 曲l r 出 o r ( ) t f e Pa s n n r m d ttgd a , c r r es d eP g ico o s as oe ei o l w h e e tt e 1 i d e1 fi lo n r sn m n h P s h v o n r tn g u s i n e n r e c . Drt it f un y es S av e e 1 n l 0 ia ld t ic Dga r ec n s仍D ) da d ayi 9 ss f1 ga e il e ys 小 i q c n r 7 o i 1 i tho g f f u c s hs i L T e o f s h i g a f a t C o r 闪n e l o r e y”t i t U m 比 d 邓t z w o d s n y es , s r o s n e l e i v r 叩 n

任意波形发生器设计报告.

2008级计算机科学与技术专业微机接口课程设计报告2010-2011学年第一学期项目名称:任意波形发生器姓名:_ 学号:成绩:姓名:学号:成绩:指导教师:一、设计:1、设计说明:利用实验仪上的数模转换器DAC0832,将程序中的一组波形的数据转换为电压的变化曲线,并用示波器测量模数转换器的输出端,观察生成的波形2、设计目标:设计一个简易波形发生器,要求该系统能通过开关或按钮有选择性的输出正弦波、三角波、方波、及阶梯波等四种波形,并且这四种波形的频率均可通过输入电位器在一定范围内调节3、实验电路图:4、设计内容: (1)主程序(2)子程序:方波程序、正弦波程序、锯齿波、三角波、键盘扫描与处理 各模块的流程图如下:A 、 主程序和键盘扫描流程:B 、 三角波、方波、正弦波、锯齿波解析如下:三角波的产生较为简单,因为它的上升沿遵循数据加1的规律。

下降沿则按数据减1的规律产生。

所以在波形的上升沿只要判断上一次的数据是否为最大值FFH ,如果不是最大值,将原数据加1输出;而在波形的下降沿只要判断上一次数据是否为0,如果不是0,则将原数据减1即可 方波只有两个值,可以采用两个极端值0和FFH正弦波使用查表法产生查表法是事先将正弦波的数据计算出来,列表放在程序中,运行时直接调取数据锯齿波与三角波类似,只是下降时直接降至0即可。

各流程图如下:延时N主程序处理流程 键盘扫描流程二、程序模块代码: .model small .stack;***********定义8255有关参数****************** addrA EQU 200h addrB EQU 201h addrC EQU 202h CTRL EQU 203h addrDA EQU 208h;*******************定义8279有关的参数*******************方波流程三角波流程锯齿波流程Z8279 EQU 212H ; 8279的控制口地址D8279 EQU 210H ; 8279的数据口地址LEDMOD EQU 00 ;左边输入,八位显示外部译码八位显示(8279的控制字)LEDFEQ EQU 38H ;8279 扫描频率;*************以上参数写在主程序开头*****************.codestart:mov al,90h ;方式0,A口输入,B、C口输出mov dx,CTRLout dx,almov ax,csmov ds,axcall CSH8279 ;调用子程序CSH8279call SMXS ;调用子程序SMXSs:call KeyPress;调用子程序keyscanmov di,offset KeyNummov si,offset XSDATAmov al,[di] ;波形号mov [si+6],almov al,[di+1] ;暂存值mov [si],almov al,[di+2] ;幅度mov [si+3],alcall SMXSmov di,offset KeyNummov al,[di]cmp al,1jne C1call A1 ;跳转到方波jmp s ;无条件跳转sC1:cmp al,2jne C2call A2 ;跳转到锯齿波jmp sC2:cmp al,3jne C3call A3 ;跳转到三角波jmp sC3:cmp al,4jne C4call A4 ;跳转到正弦波C4:jmp smov ah,4chint 21hKeyNum DB 0,0,0 ;波形参数,第一个为波形号,第二个为暂存值,第三个为幅度参数DMBIAO DB 3FH,06H,5BH,4FH,66H,6DH,7DH,07H,7FH,6FH,77H,7CH,39H DB 5EH,79H,71H,00h ;段码表,1亮,0灭,可以根据需要再设计显示字符;段中已有的显示字符是0--F和全灭。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

任意波形发生器的设计方案

12电信1 张晓航 1200301108 一,选择课题:

电子测量仪器设计——任意波形发生器设计

二,设计要求:

能产生方波、三角波、正弦波、锯齿波信号。

主要技术指标:

(1)输出频率范围100HZ~1KHZ、1~10KHZ

(2)输出电压:方波UPP=6V,三角波UPP=6V,正弦波UPP>1V,锯齿波UPP=6V。

三,仪器仪表清单:

1.直流稳压电源 1台 2.双踪示波器 2台

3.运放741(LM324n)*3 4.二极管 1N4154*2 1N4680*2

5.电位器50K*2 1K*1 6.电容1μF 47nF *1

7.电阻 100k 10k 5k 3k 4k 96k若干 8.面包板 1块

9.剪刀1把 10.仪器探头线 2根

11.电源线若干

四,设计考虑因素:

信号发生器可以通过多种方法设计产生,但是考虑到如果使用芯片去完成可能所需要的成本比较高,但如果用单片机等则设计太复杂,还需要嵌入相应代码,有点大材小用,综合多方面的因素考虑该方案是可行性比较高,性价比比较高的一种方案,同时,能够让我对于一些专业基础知识有了更深的了解。

元器件可重复利用,符合现在可持续发展的绿色思想。

该电路具有结构、思路简单,运行时性能稳定且能较好的符合设计要求,对原器件要求不高,且成本低廉、调整方便.

五,函数发生器的总方案:

为进一步掌握电路的基本理论及实验调试技术,本课题采用由集成运算放大器与晶体管差分放大器共同组成的方波—三角波(锯齿波)—正弦波函数发生器的设计方法。

本课题中函数发生器电路组成框图如下所示:

函数发生器电路组成框图

由比较器和积分器组成方波—三角波产生电路,比较器输出的方波经积分器得到三角波,三角波到正弦波的变换电路主要由差分放大器来完成。

差分放大器具有工作点稳定,输入阻抗高,抗干扰能力较强等优点。

特别是作为直流放大器时,可以有效地抑制零点漂移,因此可将频率很低的三角波变换成正弦波。

波形变换的原理是利用差分放大器传输特性曲线的非线性。

方波、三角波、正弦波、锯齿波信号发生器的原理框图六,模拟仿真:

Multisim 12中电路仿真。