用verilog编写的16位超前加法器verilog程序

用verilog编写的8位扩展超前进位加法器代码

+ Pi * Pi-1 * ... * P1 * P0 * C0

Gij = Gi + Pi * Gi-1 + Pi * Pi-1 * Gi-2 + ... + Pi * Pi-1 * ... * Pj+1 * Gj

Pij = Pi * Pi-1 * ... * Pj+1 * Pj;

Gi,i = Gi;

Pi,i = Pi;

***************************************************************************** */

module adder_8bits( s, co, a, b, ci );

assign c[ 5 ] = g04_04 | p04_04 & c[ 4 ];

assign c[ 6 ] = g05_04 | p05_04 & c[ 4 ];

assign c[ 7 ] = g06_06 | p06_06 & c[ 6 ];

assign c[ 8 ] = g07_00 | p07_00 & c[ 0 ];

8位扩展超前进位加法器

/* *****************************************************************************

Ci+1 = Ai * Bi + Bi * Ci + Ci * Ai

= Ai * Bi + ( Ai + Bi ) * Ci

verilog实现加法器

verilog实现加法器半加器如果不考虑来⾃低位的进位将两个1⼆进制数相加,称为半加。

实现半加运算的逻辑电路称为半加器。

真值表>> 逻辑表达式和s=ab′+a′b>> 逻辑表达式进位输出co=abverilog codemodule halfadder(output s, //sumoutput co, //carryinput a,input b);assign s = a ^ b;assign co = a & b;//assign {co,s} = a + b;endmoduletestbenchmodule halfadder_tb;wire s;wire co;reg a;reg b;initialbegina = 0;b = 0;#10 a = 0 ;b = 0;#10 a = 0 ;b = 1;#10 a = 1 ;b = 0;#10 a = 1 ;b = 1;#10 $finish;endinitial begin$fsdbDumpfile("test.fsdb");$fsdbDumpvars();endhalfadder u_halfadder(.s(s),.co(co),.a(a),.b(b));endmodule全加器在将两位多位⼆进制数相加时,除了最低位以外,每位都应该考虑来⾃低位的进位,即将两个对应位的加数和来⾃低位的进位3个数相加。

这种运算称为全加,所⽤的电路称为全加器。

真值表逻辑表达式和s=(a′b′ci′+ab′ci+a′bci+abci′)′>> 逻辑表达式进位输出co=(a′b′+b′ci′+a′ci′)′verilog codemodule fulladder(output s, //sumoutput co, //carry to high bitinput a,input b,input ci //carry from low bit);//RTL levelassign s = ~((~a&~b&~ci)||(a&~b&ci)||(~a&b&ci)||(a&b&~ci));assign co = ~((~a&~b)||(~b&~ci)||(~a&~ci));//assign {co,s} = a + b + ci;endmoduletestbenchmodule fulladder_tb;wire s;wire co;reg a;reg b;reg ci;initialbeginci = 0; a = 0 ;b = 0;#10 ci = 0; a = 0 ;b = 1;#10 ci = 0; a = 1 ;b = 0;#10 ci = 0; a = 1 ;b = 1;#10 ci = 1; a = 0 ;b = 0;#10 ci = 1; a = 0 ;b = 1;#10 ci = 1; a = 1 ;b = 0;#10 ci = 1; a = 1 ;b = 1;#10 $finish;endinitial begin$fsdbDumpfile("test.fsdb");$fsdbDumpvars();endfulladder u_fulladder(.s(s),.co(co),.a(a),.b(b),.ci(ci));endmodule多位加法器串⾏进位加法器依次将低位全加器的进位输出co接到全加器的进位输⼊端ci,就可以构成多位加法器。

16位超前加法器实验报告

16位超前加法器设计实验一、实验分析:四位超前进位加法器HDL程序:module add4_head ( a, b, ci, s, pp, gg);input[3:0] a;input[3:0] b;input ci;output[3:0] s;output pp;output gg;wire[3:0] p;wire[3:0] g;wire[2:0] c;assign p[0] = a[0] ^ b[0];assign p[1] = a[1] ^ b[1];assign p[2] = a[2] ^ b[2];assign p[3] = a[3] ^ b[3];assign g[0] = a[0] & b[0];assign g[1] = a[1] & b[1];assign g[2] = a[2] & b[2];assign g[3] = a[3] & b[3];assign c[0] = (p[0] & ci) | g[0];assign c[1] = (p[1] & c[0]) | g[1];assign c[2] = (p[2] & c[1]) | g[2];assign pp = p[3] & p[2] & p[1] & p[0];assign gg = g[3] | (p[3] & (g[2] | p[2] & (g[1] | p[1] & g[0])));assign s[0] = p[0] ^ ci;assign s[1] = p[1] ^ c[0];assign s[2] = p[2] ^ c[1];assign s[3] = p[3] ^ c[2];endmodulep表示进位否决信号(pass),如果p为0就否决调前一级的进位输入。

否决的意思就是即使前一级有进位,本级也不会向后一级产生进位输出。

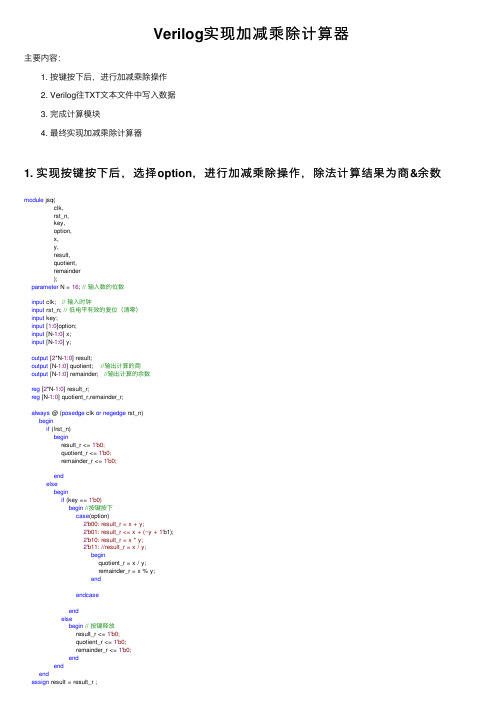

Verilog实现加减乘除计算器

Verilog实现加减乘除计算器主要内容: 1. 按键按下后,进⾏加减乘除操作 2. Verilog往TXT⽂本⽂件中写⼊数据 3. 完成计算模块 4. 最终实现加减乘除计算器1. 实现按键按下后,选择option,进⾏加减乘除操作,除法计算结果为商&余数module jsq(clk,rst_n,key,option,x,y,result,quotient,remainder);parameter N = 16; // 输⼊数的位数input clk; // 输⼊时钟input rst_n; // 低电平有效的复位(清零)input key;input [1:0]option;input [N-1:0] x;input [N-1:0] y;output [2*N-1:0] result;output [N-1:0] quotient; //输出计算的商output [N-1:0] remainder; //输出计算的余数reg [2*N-1:0] result_r;reg [N-1:0] quotient_r,remainder_r;always @ (posedge clk or negedge rst_n)beginif (!rst_n)beginresult_r <= 1'b0;quotient_r <= 1'b0;remainder_r <= 1'b0;endelsebeginif (key == 1'b0)begin//按键按下case(option)2'b00: result_r = x + y;2'b01: result_r <= x + (~y + 1'b1);2'b10: result_r = x * y;2'b11: //result_r = x / y;beginquotient_r = x / y;remainder_r = x % y;endendcaseendelsebegin// 按键释放result_r <= 1'b0;quotient_r <= 1'b0;remainder_r <= 1'b0;endendendassign result = result_r ;assign quotient= quotient_r;assign remainder = remainder_r;endmoduleView Code`timescale 1ns/1ps`define clock_period 20module jsq_tb;reg clk;reg rst_n;reg key;reg [1:0]option;reg [15:0] x,y;wire [31:0] result;wire [15:0] quotient;wire [15:0] remainder;initial beginclk = 1'b1;rst_n = 1'b0;key = 1'b1; // 复位时,按键释放# 20//复位20nsrst_n = 1'b1;# 20key = 1'b0;option = 2'b10;# 100key = 1'b1;# 20key = 1'b0;option = 2'b11;# 100// key = 1'b1;// # 20$stop;endalways #(`clock_period/2) clk = ~clk; //50Mjsq #(.N(16)) jsq_0(.clk(clk),.rst_n(rst_n),.key(key),.option(option),.x(x),.y(y),.result(result),.quotient(quotient),.remainder(remainder));initial beginx = 0;repeat(20)#(`clock_period) x = {$random}%100; //通过位拼接操作{}产⽣0—59范围的随机数endinitial beginy = 0;repeat(20)#(`clock_period) y = {$random}%50;end/*integer i;initial beginx = 0;y = 0;for(i = 0; i < 20; i = i + 1)begin//利⽤$random系统函数产⽣随机数。

verilog 加法

Verilog加法一、概述在数字电路设计中,加法是最基本的运算之一。

Verilog是一种硬件描述语言,常用于数字电路的建模和仿真。

本文将详细介绍Verilog中的加法实现方法和相关知识。

二、加法原理加法是一种基本的算术运算,用于将两个数值相加得到它们的和。

在数字电路中,加法可以通过逻辑门电路来实现。

常见的加法电路有半加器、全加器、加法器等。

2.1 半加器半加器是最基本的加法电路,用于将两个输入位相加,并输出它们的和以及进位。

半加器的真值表如下:A B Sum Carry0 0 0 00 1 1 01 0 1 01 1 0 12.2 全加器全加器是一种可以处理两个输入位和一个进位位的加法电路。

全加器的真值表如下:A B Cin Sum Cout0 0 0 0 00 0 1 1 00 1 0 1 00 1 1 0 11 0 0 1 01 0 1 0 11 1 0 0 11 1 1 1 12.3 加法器加法器是由多个全加器组成的电路,用于实现多位数的加法运算。

常见的加法器有Ripple Carry Adder(连续进位加法器)、Carry Look-ahead Adder(预先计算进位加法器)等。

三、Verilog实现在Verilog中,可以使用模块化的方式来实现加法器电路。

下面是一个4位全加器的Verilog代码示例:module FullAdder(input wire A,input wire B,input wire Cin,output wire Sum,output wire Cout);assign Sum = A ^ B ^ Cin;assign Cout = (A & B) | (Cin & (A ^ B));endmodulemodule FourBitAdder(input wire [3:0] A,input wire [3:0] B,output wire [3:0] Sum,output wire Cout);wire [3:0] carry;FullAdder FA0(A[0], B[0], 1'b0, Sum[0], carry[0]);FullAdder FA1(A[1], B[1], carry[0], Sum[1], carry[1]);FullAdder FA2(A[2], B[2], carry[1], Sum[2], carry[2]);FullAdder FA3(A[3], B[3], carry[2], Sum[3], Cout);endmodulemodule TestFourBitAdder;reg [3:0] A;reg [3:0] B;wire [3:0] Sum;wire Cout;FourBitAdder FBA(A, B, Sum, Cout);initial beginA = 4'b0001;B = 4'b0011;#10;$display("Sum: %b", Sum);$display("Cout: %b", Cout);endendmodule四、仿真结果通过上述Verilog代码进行仿真,可以得到以下结果:Sum: 0100Cout: 0五、总结本文介绍了Verilog中加法的原理和实现方法。

74181 ALU的设计及16位加法功能验证

74181 ALU的设计及16位加法功能验证This is a controlled document.Printed copies must have the revision number verified prior to each use.修改记录分工情况目录修改记录................................................................................................... 错误!未定义书签。

分工情况................................................................................................... 错误!未定义书签。

目录................................................................................................... 错误!未定义书签。

1.0B关于本文 ......................................................................................... 错误!未定义书签。

1.1 4B目的............................................................................................ 错误!未定义书签。

1.2 5B术语列表........................................................................................ 错误!未定义书签。

1.3 6B相关文档........................................................................................ 错误!未定义书签。

基于FPGA的模可变16进制加法器的设计

课程设计任务书学生姓名:兰翔专业班级:电子科学与技术2班指导教师:葛华工作单位:信息工程学院题目:模可变16位加法计数器设计初始条件:QuartusII6.0,微机要求完成的主要任务:深入学习Verilog HDL语言与FPGA理论知识。

利用QuartusII强大的硬件语言处理功能,数字电路仿真功能以及波形处理功能,实现模可变16位加法计数器设计。

1.利用Verilog HDL语言描述计数器功能;2.用QuartusII对Verilog HDL语言进行仿真;3. 撰写《EDA技术应用实践》课程设计说明书。

时间安排:学习Verilog HDL语言的概况第1天学习Verilog HDL语言的基本知识第2、3天学习QuartusII的应用环境,仿真功能。

第4、5天课程设计第6-9天答辩第10天指导教师签名:年月日系主任(或责任教师)签名:年月日目录摘要 (I)A BSTRACT.......................................................... I I1.设计任务 (1)1.1初始条件 (1)1.2课题要求 (1)1.3设计要求 (1)2.Q UARTUS II简介 (2)3.课题内容 (3)3.1 总体框图 (3)3.2 各部分功能 (3)3.2.1按键触发 (3)3.2.2 LED显示部分 (5)3.2.3计数部分 (6)4.心得体会 (8)参考文献 (9)附录一V ERILOG HDL原程序 (10)附录二总原理图 (15)摘要FPGA(Field Programmable Gate Array)即“现场可编程门阵列”是应着当代微电子技术迅猛发展而产生的一种技术,到现在为止,已经存在了27年。

由于其电路执行速度快、上市时间短、成本低廉、可靠性高、易于维护升级而被人们所青睐,目前已经广泛用于通信、信号处理、嵌入式处理器、图形处理和工业控制的领域。

本次课设就是在Altera公司的FPGA设计平台QuartusII上进行的计数器设计。

verilog 加法

verilog 加法(最新版)目录1.Verilog 简介2.Verilog 加法原理3.Verilog 加法实例4.总结正文1.Verilog 简介Verilog 是一种硬件描述语言,主要用于数字系统硬件的描述、模拟和验证。

它是由 Phil Moorby 在 1983 年为描述和模拟数字电路而创建的。

后来,Verilog 得到了广泛应用,并成为了电子设计自动化(EDA)领域的标准语言。

Verilog 具有易学易用、功能强大等特点,是数字电路设计工程师必备的技能。

2.Verilog 加法原理在 Verilog 中,加法原理主要通过“与”、“与非”和“或”等基本逻辑门实现。

这些逻辑门可以组合成复杂的加法电路。

例如,全加器可以通过“与”门、“与非”门和“或”门实现。

全加器的输入有三个:A、B 和 Cin(输入的 C),输出有两个:S(和)和 Cout(输出的 C)。

S 等于 A 与 B 与 Cin,Cout 等于 A 与 Cin 或B 与 Cin 或 A 与 B。

通过这个全加器,我们可以实现两个二进制数的加法运算。

3.Verilog 加法实例下面是一个简单的 Verilog 代码实例,用于实现两个 4 位二进制数的加法:```verilogmodule adder_4bit(input [3:0] A, input [3:0] B, input Cin, output S, output Cout);assign S[3:0] = A[3:0] & B[3:0] & Cin;assign Cout[3:0] = (A[3:0] & Cin) | (B[3:0] & Cin) | (A[3:0] & B[3:0]);endmodule```在这个例子中,我们定义了一个名为 adder_4bit 的模块,它有 5 个输入端口(A、B、Cin、S 和 Cout)和 2 个输出端口(S 和 Cout)。