2、3、4输入或非门版图设计

双4输入或非门(有选通端)

7425………… …………………………………. 0~70℃

存储温度 ……………………………源电压 VCC

h输入高电平电压ViH t输入低电平电压ViL t输出高电平电流IOH p输出低电平电流IOL

5425/7425

最小

额定

最大

单位

54

4.5

5

Vcc=最大

54 74

Vcc=最大

Vcc=最大

‘25 最小 最大

-1.5 2.4

0.4 1 160 40 -6.4 -1.6 -20 -55 -18 -55 16 19

单位

V V V mA uA

mA

mA

mA mA

f [1]: 测试条件中的“最小”和“最大”用推荐工作条件中的相应值。

an 动态特性(TA=25℃) 参数 s tPLH输出由低到高传输延迟时间 .com tPHL输出由高到低传输延迟时间

5.5

V

74

4.75

5

5.25

2

V

0.8

V

-800

µA

16

mA

:/ 静态特性(TA 为工作环境温度范围)

/参 数

测 试 条 件【1】

w VIK输入嵌位电压 w IOH 输出高电平电压

VOL输出低电平电压 II最大输入电压时输入电流

w IIH输入高电平电流

1ST,2ST 其余输入

. IIL输入低电平电流 1ST,2ST e 其余输入

测试条件 Vcc =5V,CL=15Pf ,RL=400Ω

‘25 最大 22 15

单位

ns ns

l IOS输出短路电流 e ICCH输出高电平时电源电流 c ICCL输出低电平时电源电流

四输入与非门版图

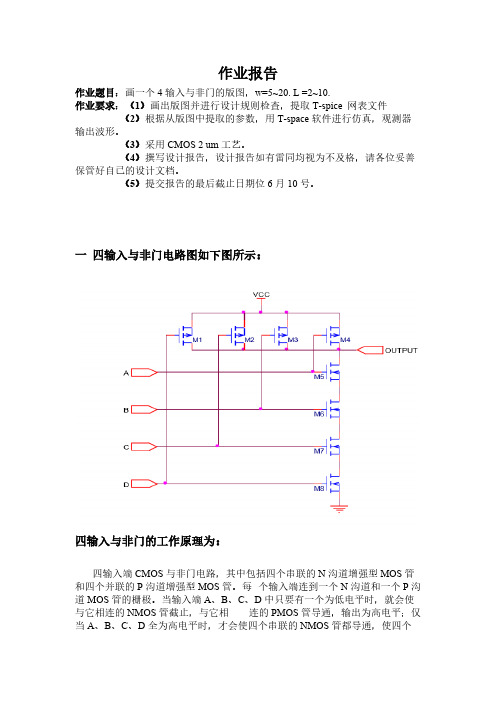

作业报告作业题目:画一个4输入与非门的版图,w=5~20. L =2~10.作业要求:(1)画出版图并进行设计规则检查,提取T-spice 网表文件(2)根据从版图中提取的参数,用T-space软件进行仿真,观测器输出波形。

(3)采用CMOS 2 um工艺。

(4)撰写设计报告,设计报告如有雷同均视为不及格,请各位妥善保管好自己的设计文档。

(5)提交报告的最后截止日期位6月10号。

一四输入与非门电路图如下图所示:四输入与非门的工作原理为:四输入端CMOS与非门电路,其中包括四个串联的N沟道增强型MOS管和四个并联的P沟道增强型MOS管。

每个输入端连到一个N沟道和一个P沟道MOS管的栅极。

当输入端A、B、C、D中只要有一个为低电平时,就会使与它相连的NMOS管截止,与它相连的PMOS管导通,输出为高电平;仅当A、B、C、D全为高电平时,才会使四个串联的NMOS管都导通,使四个并联的PMOS管都截止,输出为低电平。

真值表如下所示:二版图的绘制这次作业要求四输入与非门的宽和长的范围是w=5~20. L =2~10。

我绘制的版图选取W=16 um L=2um ,绘制的过程为:(1)绘制接合端口Abut(2)绘制电源Vdd和Gnd,以及相应端口(3)绘制Nwell层(4)绘制N阱节点(5)绘制衬底节点(6)绘制Nselect区和Pselect区(7)绘制NMOS有源区和PMOS有源区(8)绘制多晶硅层(9)绘制NAND 4 的输入口(10)绘制NAND 4 的输出口(11)绘制NMOS有源区和PMOS的源极三T-spice仿真在绘制完版图之后,经过设计规则检查无误后就可以提取网表进行仿真了。

(1)版图的网表提取结果为:* Circuit Extracted by Tanner Research's L-Edit Version 13.00 / Extract Version 13.00 ; * TDB File: D:\\youwenhao-NAND4.tdb* Cell: Cell0 Version 1.03* Extract Definition File: D:\Tanner EDA\Tanner Tools v13.0\ExampleSetup\lights.ext* Extract Date and Time: 06/10/2014 - 01:20.include "C:\Users\Administrator\Desktop\ml5_20.md"V1 Vdd Gnd 5va A Gnd PULSE (0 2.5 100n 2.5n 2.5n 100n 200n)vb B Gnd PULSE (0 2.5 50n 2.5n 2.5n 50n 100n)vc C Gnd PULSE (0 2.5 25n 2.5n 2.5n 25n 50n)vd D Gnd PULSE (0 2.5 12.5n 2.5n 2.5n 12.5n 25n).tran 1n 400n.print tran v(A) v(B) v(C) v(D) v(Out)* Warning: Layers with Unassigned FRINGE Capacitance.* <Pad Comment>* <Poly1-Poly2 Capacitor ID>* NODE NAME ALIASES* 1 = GND (34.5 , -41.5)* 2 = vdd (32, 15)* 3 = OUT (47.5 , 9)* 4 = D (84 , -6)* 5 = C (70.5 , -5.5)* 6 = B (59.5 , -6)* 7 = A (38 , -5)V1 Vdd Gnd 5va A Gnd PULSE (0 12.5 500n 12.5n 12.5n 5100n 1000n)vb B Gnd PULSE (0 12.5 250n 12.5n 12.5n 250n 500n)vc C Gnd PULSE (0 12.5 125n 12.5n 12.5n 125n 250n)vd D Gnd PULSE (0 12.5 62.5n 12.5n 12.5n 62.5n 125n).tran 1n 1000n.print tran v(D) v(C) v(B) v(A) v(Out)M1 Vdd 4 Out Vdd PMOS L=2u W=16u AD=88p PD=47u AS=60p PS=23.5u $ (44 37 46 53)M2 Out 5 Vdd Vdd PMOS L=2u W=16u AD=60p PD=23.5u AS=56p PS=23u $ (34.5 37 36.5 53)M3 Vdd 6 Out Vdd PMOS L=2u W=16u AD=56p PD=23u AS=112p PS=30u $ (25.5 37 27.5 53)M4 Out 7 Vdd Vdd PMOS L=2u W=16u AD=112p PD=30u AS=88p PS=47u $ (9.5 37 11.5 53)M5 Out 4 Out Gnd NMOS L=2u W=16u AD=120p PD=47u AS=60p PS=23.5u $ (44 0 46 16)M6 Out 5 Out Gnd NMOS L=2u W=16u AD=60p PD=23.5u AS=56p PS=23u $ (34.5 0 36.5 16)M7 Out 6 Out Gnd NMOS L=2u W=16u AD=56p PD=23u AS=112p PS=30u $ (25.5 0 27.5M8 Out 7 Gnd Gnd NMOS L=2u W=16u AD=112p PD=30u AS=92p PS=47u $ (9.5 0 11.5 16)* Pins of element D1 are shorted:* D1 vdd vdd D_lateral $ (88 18.5 91 26.5)* Pins of element D2 are shorted:* D2 vdd vdd D_lateral $ (36 18.5 39.5 26.5)* Total Nodes: 11* Total Elements: 10* Total Number of Shorted Elements not written to the SPICE file: 0* Output Generation Elapsed Time: 0.001 sec* Total Extract Elapsed Time: 0.746 sec.END(2)提取的网表经过T-spice运行后的文件为:T-Spice - Tanner SPICET-Spice - Tanner SPICEVersion 13.00Standalone hardware lockProduct Release ID: T-Spice Win32 13.00..01:01:33Copyright ?1993-2008 Tanner EDAOpening output file "C:\Users\Administrator\Desktop\游文浩\youwenhao-NAND4.out"Parsing "C:\Users\Administrator\Desktop\游文浩\youwenhao-NAND4.spc"Initializing parser from header file "C:\Users\Administrator\Desktop\游文浩\header.sp"Including "C:\Users\Administrator\Desktop\ml5_20.md"Loaded MOSLevel2 model library, SPICE Level 2 MOSFET revision 1.0Warning : Pulse period is too small, reset to rt + ft + pw = 5.125e-006Accuracy and Convergence options:numndset|dchold = 100Timestep and Integration options:relq|relchgtol = 0.0005Model Evaluation options:dcap = 2 defnrb = 0 [sq] defnrd = 0 [sq]defnrs = 0 [sq] tnom = 25 [deg C]General options:search = C:\Users\Administrator\Desktop temp = 25 [degthreads = 4Output options:acout = 1 ingold = 0Device and node counts:MOSFETs - 8 MOSFET geometries - 8BJTs - 0 JFETs - 0 MESFETs - 0 Diodes - 0 Capacitors - 0 Resistors - 0Inductors - 0 Mutual inductors - 0 Transmission lines - 0 Coupled transmission lines - 0 V oltage sources - 5 Current sources - 0VCVS - 0 VCCS - 0CCVS - 0 CCCS - 0 V-control switch - 0 I-control switch - 0 Macro devices - 0 External C model instances - 0HDL devices - 0Subcircuits - 0 Subcircuit instances - 0 Independent nodes - 5 Boundary nodes - 6 Total nodes - 11*** 1 WARNING MESSAGE GENERATED DURING SETUPParsing 0.00 secondsSetup 0.01 secondsDC operating point 0.00 secondsTransient Analysis 0.11 secondsOverhead 1.50 seconds-----------------------------------------Total 1.62 secondsSimulation completed with 1 Warning(3)仿真结果为:四作业总结:完成这次作业之后,我对于集成电路版图的绘制有了一个全新的认识,初步掌握了Tunner软件的使用以及T-spice仿真软件的使用。

四输入或非门电路和版图设计说明

成绩评定表课程设计任务书目录目录 (III)1.绪论 (1)1.1 设计背景 (1)1.2 设计目标 (1)2.四输入或非门 (2)2.1 四输入或非门电路结构 (2)2.2 四输入或非门电路仿真 (3)2.3 四输入或非门的版图绘制 (4)2.4 四输入或非门的版图电路仿真 (5)2.5 LVS检查匹配 (6)总结 (7)附录一:原理图网表 (9)附录二:版图网表 (10)1.绪论1.1 设计背景Tanner集成电路设计软件是由Tanner Research 公司开发的基于Windows平台的用于集成电路设计的工具软件。

该软件功能十分强大,易学易用,包括S-Edit,T-Spice,W-Edit,L-Edit与LVS,从电路设计、分析模拟到电路布局一应俱全。

其中的L-Edit 版图编辑器在国内应用广泛,具有很高知名度。

L-Edit Pro是Tanner EDA软件公司所出品的一个IC设计和验证的高性能软件系统模块,具有高效率,交互式等特点,强大而且完善的功能包括从IC设计到输出,以及最后的加工服务,完全可以媲美百万美元级的IC设计软件。

L-Edit Pro包含IC设计编辑器(Layout Editor)、自动布线系统(Standard Cell Place & Route)、线上设计规则检查器(DRC)、组件特性提取器(Device Extractor)、设计布局与电路netlist的比较器(LVS)、CMOS Library、Marco Library,这些模块组成了一个完整的IC设计与验证解决方案。

L-Edit Pro丰富完善的功能为每个IC设计者和生产商提供了快速、易用、精确的设计系统。

1.2 设计目标1.用tanner软件中的原理图编辑器S-Edit编辑四输入或非门电路原理图。

2.用tanner软件中的TSpice对四输入或非门电路进行仿真并观察波形。

3.用tanner软件中的L-Edit绘制四输入或非门版图,并进行DRC验证。

二输入与非门、或非门版图设计

课程名称Course 集成电路设计技术项目名称Item二输入与非门、或非门版图设计与非门电路的版图:.spc文件(瞬时分析):* Circuit Extracted by Tanner Research's L-Edit V7.12 / Extract V4.00 ;* TDB File: E:\cmos\yufeimen, Cell: Cell0* Extract Definition File: C:\Program Files\Tanner EDA\L-Edit\spr\morbn20.ext * Extract Date and Time: 05/25/2011 - 10:03.include H:\ml2_125.mdVPower VDD GND 5va A GND PULSE (0 5 0 5n 5n 100n 200n)vb B GND PULSE (0 5 0 5n 5n 50n 100n).tran 1n 400n.print tran v(A) v(B) v(F)* WARNING: Layers with Unassigned AREA Capacitance.* <Poly Resistor>* <Poly2 Resistor>* <N Diff Resistor>* <P Diff Resistor>* <N Well Resistor>* <P Base Resistor>* WARNING: Layers with Unassigned FRINGE Capacitance.* <Pad Comment>* <Poly Resistor>* <Poly2 Resistor>* <N Diff Resistor>* <P Diff Resistor>* <N Well Resistor>* <P Base Resistor>* <Poly1-Poly2 Capacitor>* WARNING: Layers with Zero Resistance.* <Pad Comment>* <Poly1-Poly2 Capacitor>* <NMOS Capacitor>* <PMOS Capacitor>* NODE NAME ALIASES* 1 = VDD (34,37)* 2 = A (29.5,6.5)* 3 = B (55.5,6.5)* 4 = F (42.5,6.5)* 6 = GND (25,-22)M1 VDD B F VDD PMOS L=2u W=9u AD=99p PD=58u AS=54p PS=30u* M1 DRAIN GATE SOURCE BULK (47.5 14.5 49.5 23.5)M2 F A VDD VDD PMOS L=2u W=9u AD=54p PD=30u AS=99p PS=58u* M2 DRAIN GATE SOURCE BULK (39.5 14.5 41.5 23.5)M3 F B 5 GND NMOS L=2u W=9.5u AD=52.25p PD=30u AS=57p PS=31u * M3 DRAIN GATE SOURCE BULK (47.5 -18 49.5 -8.5)M4 5 A GND GND NMOS L=2u W=9.5u AD=57p PD=31u AS=52.25p PS=30u * M4 DRAIN GATE SOURCE BULK (39.5 -18 41.5 -8.5)* Total Nodes: 6* Total Elements: 4* Extract Elapsed Time: 0 seconds.END与非门电路仿真波形图(瞬时分析):.spc文件(直流分析):* Circuit Extracted by Tanner Research's L-Edit V7.12 / Extract V4.00 ;* TDB File: E:\cmos\yufeimen, Cell: Cell0* Extract Definition File: C:\Program Files\Tanner EDA\L-Edit\spr\morbn20.ext * Extract Date and Time: 05/25/2011 - 10:03.include H:\ml2_125.mdVPower VDD GND 5va A GND 5vb B GND 5.dc va 0 5 0.02 vb 0 5 0.02.print dc v(F)* WARNING: Layers with Unassigned AREA Capacitance.* <Poly Resistor>* <Poly2 Resistor>* <N Diff Resistor>* <P Diff Resistor>* <N Well Resistor>* <P Base Resistor>* WARNING: Layers with Unassigned FRINGE Capacitance.* <Pad Comment>* <Poly Resistor>* <Poly2 Resistor>* <N Diff Resistor>* <P Diff Resistor>* <N Well Resistor>* <P Base Resistor>* <Poly1-Poly2 Capacitor>* WARNING: Layers with Zero Resistance.* <Pad Comment>* <Poly1-Poly2 Capacitor>* <NMOS Capacitor>* <PMOS Capacitor>* NODE NAME ALIASES* 1 = VDD (34,37)* 2 = A (29.5,6.5)* 3 = B (55.5,6.5)* 4 = F (42.5,6.5)* 6 = GND (25,-22)M1 VDD B F VDD PMOS L=2u W=9u AD=99p PD=58u AS=54p PS=30u* M1 DRAIN GATE SOURCE BULK (47.5 14.5 49.5 23.5)M2 F A VDD VDD PMOS L=2u W=9u AD=54p PD=30u AS=99p PS=58u* M2 DRAIN GATE SOURCE BULK (39.5 14.5 41.5 23.5)M3 F B 5 GND NMOS L=2u W=9.5u AD=52.25p PD=30u AS=57p PS=31u * M3 DRAIN GATE SOURCE BULK (47.5 -18 49.5 -8.5)M4 5 A GND GND NMOS L=2u W=9.5u AD=57p PD=31u AS=52.25p PS=30u * M4 DRAIN GATE SOURCE BULK (39.5 -18 41.5 -8.5)* Total Nodes: 6* Total Elements: 4* Extract Elapsed Time: 0 seconds.END与非门电路仿真波形图(直流分析):或非门电路的版图:.spc文件(瞬时分析):* Circuit Extracted by Tanner Research's L-Edit V7.12 / Extract V4.00 ;* TDB File: E:\cmos\huofeimen, Cell: Cell0* Extract Definition File: C:\Program Files\Tanner EDA\L-Edit\spr\morbn20.ext * Extract Date and Time: 05/25/2011 - 10:04.include H:\CMOS\ml2_125.mdVPower VDD GND 5va A GND PULSE (0 5 0 5n 5n 100n 200n)vb B GND PULSE (0 5 0 5n 5n 50n 100n).tran 1n 400n.print tran v(A) v(B) v(F)* WARNING: Layers with Unassigned AREA Capacitance.* <Poly Resistor>* <Poly2 Resistor>* <N Diff Resistor>* <P Diff Resistor>* <N Well Resistor>* <P Base Resistor>* WARNING: Layers with Unassigned FRINGE Capacitance.* <Poly Resistor>* <Poly2 Resistor>* <N Diff Resistor>* <P Diff Resistor>* <N Well Resistor>* <Pad Comment>* <P Base Resistor>* <Poly1-Poly2 Capacitor>* WARNING: Layers with Zero Resistance.* <Pad Comment>* <Poly1-Poly2 Capacitor>* <NMOS Capacitor>* <PMOS Capacitor>* NODE NAME ALIASES* 1 = VDD (34,37)* 2 = A (29.5,6.5)* 3 = B (55.5,6)* 4 = F (42.5,6.5)* 5 = GND (25,-22)M1 6 A VDD VDD PMOS L=2u W=9u AD=54p PD=30u AS=49.5p PS=29u* M1 DRAIN GATE SOURCE BULK (39.5 14.5 41.5 23.5)M2 F B 6 VDD PMOS L=2u W=9u AD=49.5p PD=29u AS=54p PS=30u* M2 DRAIN GATE SOURCE BULK (47.5 14.5 49.5 23.5)M3 F A GND GND NMOS L=2u W=9.5u AD=57p PD=31u AS=104.5p PS=60u * M3 DRAIN GATE SOURCE BULK (39.5 -18 41.5 -8.5)M4 GND B F GND NMOS L=2u W=9.5u AD=104.5p PD=60u AS=57p PS=31u * M4 DRAIN GATE SOURCE BULK (47.5 -18 49.5 -8.5)* Total Nodes: 6* Total Elements: 4* Extract Elapsed Time: 0 seconds.END或非门电路仿真波形图(瞬时分析):.spc文件(直流分析):* Circuit Extracted by Tanner Research's L-Edit V7.12 / Extract V4.00 ;* TDB File: E:\cmos\huofeimen, Cell: Cell0* Extract Definition File: C:\Program Files\Tanner EDA\L-Edit\spr\morbn20.ext * Extract Date and Time: 05/25/2011 - 10:04.include H:\CMOS\ml2_125.mdVPower VDD GND 5va A GND 5vb B GND 5.dc va 0 5 0.02 vb 0 5 0.02.print dc v(F)* WARNING: Layers with Unassigned AREA Capacitance.* <Poly Resistor>* <Poly2 Resistor>* <N Diff Resistor>* <P Diff Resistor>* <N Well Resistor>* <P Base Resistor>* WARNING: Layers with Unassigned FRINGE Capacitance.* <Poly Resistor>* <Poly2 Resistor>* <N Diff Resistor>* <P Diff Resistor>* <N Well Resistor>* <Pad Comment>* <P Base Resistor>* <Poly1-Poly2 Capacitor>* WARNING: Layers with Zero Resistance.* <Pad Comment>* <Poly1-Poly2 Capacitor>* <NMOS Capacitor>* <PMOS Capacitor>* NODE NAME ALIASES* 1 = VDD (34,37)* 2 = A (29.5,6.5)* 3 = B (55.5,6)* 4 = F (42.5,6.5)* 5 = GND (25,-22)M1 6 A VDD VDD PMOS L=2u W=9u AD=54p PD=30u AS=49.5p PS=29u* M1 DRAIN GATE SOURCE BULK (39.5 14.5 41.5 23.5)M2 F B 6 VDD PMOS L=2u W=9u AD=49.5p PD=29u AS=54p PS=30u* M2 DRAIN GATE SOURCE BULK (47.5 14.5 49.5 23.5)M3 F A GND GND NMOS L=2u W=9.5u AD=57p PD=31u AS=104.5p PS=60u * M3 DRAIN GATE SOURCE BULK (39.5 -18 41.5 -8.5)M4 GND B F GND NMOS L=2u W=9.5u AD=104.5p PD=60u AS=57p PS=31u * M4 DRAIN GATE SOURCE BULK (47.5 -18 49.5 -8.5)* Total Nodes: 6* Total Elements: 4* Extract Elapsed Time: 0 seconds.END或非门电路仿真波形图(直流分析):内容(方法、步骤、要求或考核标准及所需工具、设备等)一、实训设备与工具1.PVI计算机一台;2.Tanner Pro集成电路设计软件二、实训方法、步骤与要求1.二输入与非门电路的线路结构2.二输入或非门电路的线路结构3.CMOS倒相器电路的版图4.根据与非门、或非门线路结构,在一个工程中,重新新建两个新CELL,分别对应与非门和或非门版图,并设计与非门、或非版图结构。

实验七反相器,二输入与非门以及二输入或非门版图设计

实验七反相器,⼆输⼊与⾮门以及⼆输⼊或⾮门版图设计学号姓名

实验七1.反相器

反相器EECMOS的schematic图如下所⽰

其中PMOS管L=180nm W=720nm NMOS管L=180nm W=240nm

根据schematic画出的layout图如下所⽰

其中该版图长:2.16um 宽:4.87um

则版图⾯积为S=L*W=2.16*4.87=10.5192(um^2)

经过多此修改后,DRC验证如下

LVS验证如下

2.⼆输⼊与⾮门

⼆输⼊与⾮门nand2的schematic图如下所⽰

其中两个PMOS管的L=180nm W=720nm 两个NMOS管的L=180nm W=720nm 根据schematic图画出的layout版图如下所⽰

其中nand2版图的长:2.76um 宽:5.14um

则版图的⾯积S=L*W=2.76*5.14=14.1864(um^2)

通过改错后,DRC验证结果如下

LVS验证结果如下

3.⼆输⼊或⾮门

⼆输⼊或⾮门nor的schematic图如下所⽰

其中两个PMOS管的L=180nm W=2.51um 两个NMOS管的L=180nm W=500nm

由schematic图画出的layout版图如下所⽰

由于PMOS管的宽度较⼤,为了提⾼能通过的峰值电流,不浪费diff的⾯积,最⼤限度打满了源漏孔

其中该版图的长:2.91um 宽6.65um

则版图⾯积S=L*W=2.91*6.65=19.3531(um^2)

通过改错,DRC验证结果如下

LVS验证结果如下。

四输出与非门版图

作业报告作业题目:画一个4输入与非门的版图,w=5~20. L =2~10.作业要求:(1)画出版图并进行设计规则检查,提取T-spice 网表文件(2)根据从版图中提取的参数,用T-space软件进行仿真,观测器输出波形。

(3)采用CMOS 2 um工艺。

(4)撰写设计报告,设计报告如有雷同均视为不及格,请各位妥善保管好自己的设计文档。

(5)提交报告的最后截止日期位6月10号。

一四输入与非门电路图如下图所示:四输入与非门的工作原理为:四输入端CMOS与非门电路,其中包括四个串联的N沟道增强型MOS管和四个并联的P沟道增强型MOS管。

每个输入端连到一个N沟道和一个P沟道MOS管的栅极。

当输入端A、B、C、D中只要有一个为低电平时,就会使与它相连的NMOS管截止,与它相连的PMOS管导通,输出为高电平;仅当A、B、C、D全为高电平时,才会使四个串联的NMOS管都导通,使四个并联的PMOS管都截止,输出为低电平。

真值表如下所示:二版图的绘制这次作业要求四输入与非门的宽和长的范围是w=5~20. L =2~10。

我绘制的版图选取W=16 um L=2um ,绘制的过程为:(1)绘制接合端口Abut(2)绘制电源Vdd和Gnd,以及相应端口(3)绘制Nwell层(4)绘制N阱节点(5)绘制衬底节点(6)绘制Nselect区和Pselect区(7)绘制NMOS有源区和PMOS有源区(8)绘制多晶硅层(9)绘制NAND 4 的输入口(10)绘制NAND 4 的输出口(11)绘制NMOS有源区和PMOS的源极三T-spice仿真在绘制完版图之后,经过设计规则检查无误后就可以提取网表进行仿真了。

(1)版图的网表提取结果为:* Circuit Extracted by Tanner Research's L-Edit Version 13.00 / Extract Version 13.00 ; * TDB File: D:\20113250\youwenhao-NAND4.tdb* Cell: Cell0Version 1.03* Extract Definition File: D:\Tanner EDA\Tanner Tools v13.0\ExampleSetup\lights.ext* Extract Date and Time: 06/10/2014 - 01:20.include "C:\Users\Administrator\Desktop\ml5_20.md"V1 Vdd Gnd 5va A Gnd PULSE (0 2.5 100n 2.5n 2.5n 100n 200n)vb B Gnd PULSE (0 2.5 50n 2.5n 2.5n 50n 100n)vc C Gnd PULSE (0 2.5 25n 2.5n 2.5n 25n 50n)vd D Gnd PULSE (0 2.5 12.5n 2.5n 2.5n 12.5n 25n).tran 1n 400n.print tran v(A) v(B) v(C) v(D) v(Out)* Warning: Layers with Unassigned FRINGE Capacitance.* <Pad Comment>* <Poly1-Poly2 Capacitor ID>* NODE NAME ALIASES* 1 = GND (34.5 , -41.5)* 2 = vdd (32, 15)* 3 = OUT (47.5 , 9)* 4 = D (84 , -6)* 5 = C (70.5 , -5.5)* 6 = B (59.5 , -6)* 7 = A (38 , -5)V1 Vdd Gnd 5va A Gnd PULSE (0 12.5 500n 12.5n 12.5n 5100n 1000n)vb B Gnd PULSE (0 12.5 250n 12.5n 12.5n 250n 500n)vc C Gnd PULSE (0 12.5 125n 12.5n 12.5n 125n 250n)vd D Gnd PULSE (0 12.5 62.5n 12.5n 12.5n 62.5n 125n).tran 1n 1000n.print tran v(D) v(C) v(B) v(A) v(Out)M1 Vdd 4 Out Vdd PMOS L=2u W=16u AD=88p PD=47u AS=60p PS=23.5u $ (44 37 46 53)M2 Out 5 Vdd Vdd PMOS L=2u W=16u AD=60p PD=23.5u AS=56p PS=23u $ (34.5 37 36.5 53)M3 Vdd 6 Out Vdd PMOS L=2u W=16u AD=56p PD=23u AS=112p PS=30u $ (25.5 37 27.5 53)M4 Out 7 Vdd Vdd PMOS L=2u W=16u AD=112p PD=30u AS=88p PS=47u $ (9.5 37 11.5 53)M5 Out 4 Out Gnd NMOS L=2u W=16u AD=120p PD=47u AS=60p PS=23.5u $ (44 0 46 16) M6 Out 5 Out Gnd NMOS L=2u W=16u AD=60p PD=23.5u AS=56p PS=23u $ (34.5 0 36.5 16)M7 Out 6 Out Gnd NMOS L=2u W=16u AD=56p PD=23u AS=112p PS=30u $ (25.5 0 27.5 16)M8 Out 7 Gnd Gnd NMOS L=2u W=16u AD=112p PD=30u AS=92p PS=47u $ (9.5 0 11.5 16)* Pins of element D1 are shorted:* D1 vdd vdd D_lateral $ (88 18.5 91 26.5)* Pins of element D2 are shorted:* D2 vdd vdd D_lateral $ (36 18.5 39.5 26.5)* Total Nodes: 11* Total Elements: 10* Total Number of Shorted Elements not written to the SPICE file: 0* Output Generation Elapsed Time: 0.001 sec* Total Extract Elapsed Time: 0.746 sec.END(2)提取的网表经过T-spice运行后的文件为:T-Spice - Tanner SPICET-Spice - Tanner SPICEVersion 13.00Standalone hardware lockProduct Release ID: T-Spice Win32 13.00.20080321.01:01:33Copyright ?1993-2008 Tanner EDAOpening output file "C:\Users\Administrator\Desktop\游文浩20113250\youwenhao-NAND4.out"Parsing "C:\Users\Administrator\Desktop\游文浩20113250\youwenhao-NAND4.spc"Initializing parser from header file "C:\Users\Administrator\Desktop\游文浩20113250\header.sp"Including "C:\Users\Administrator\Desktop\ml5_20.md"Loaded MOSLevel2 model library, SPICE Level 2 MOSFET revision 1.0Warning : Pulse period is too small, reset to rt + ft + pw = 5.125e-006Accuracy and Convergence options:numndset|dchold = 100Timestep and Integration options:relq|relchgtol = 0.0005Model Evaluation options:dcap = 2 defnrb = 0 [sq] defnrd = 0 [sq]defnrs = 0 [sq] tnom = 25 [deg C]General options:search = C:\Users\Administrator\Desktop temp = 25 [deg C]threads = 4Output options:acout = 1 ingold = 0Device and node counts:MOSFETs - 8 MOSFET geometries - 8BJTs - 0 JFETs - 0MESFETs - 0 Diodes - 0Capacitors - 0 Resistors - 0Inductors - 0 Mutual inductors - 0Transmission lines - 0 Coupled transmission lines - 0Voltage sources - 5 Current sources - 0VCVS - 0 VCCS - 0CCVS - 0 CCCS - 0 V-control switch - 0 I-control switch - 0Macro devices - 0 External C model instances - 0HDL devices - 0Subcircuits - 0 Subcircuit instances - 0Independent nodes - 5 Boundary nodes - 6Total nodes - 11*** 1 WARNING MESSAGE GENERATED DURING SETUPParsing 0.00 secondsSetup 0.01 secondsDC operating point 0.00 secondsTransient Analysis 0.11 secondsOverhead 1.50 seconds-----------------------------------------Total 1.62 secondsSimulation completed with 1 Warning(3)仿真结果为:四作业总结:完成这次作业之后,我对于集成电路版图的绘制有了一个全新的认识,初步掌握了Tunner软件的使用以及T-spice仿真软件的使用。

三输入或门版图设计

1绪论1.1 设计背景随着集成电路技术的日益进步,使得计算机辅助设计(CAD)技术已成为电路设计师不可缺少的有力工具[1]。

国内外电子线路CAD软件的相继推出与版本更新,使CAD技术的应用渗透到电子线路与系统设计的各个领域,如芯片版图的绘制、电路的绘图、模拟电路仿真、逻辑电路仿真、优化设计、印刷电路板的布线等。

CAD技术的发展使得电子线路设计的速度、质量和精度得以保证。

在众多的CAD工具软件中,Spice程序是精度最高、最受欢迎的软件工具,tanner是用来IC版图绘制软件,许多EDA系统软件的电路模拟部分是应用Spice程序来完成的,而tanner软件是一款学习阶段应用的版图绘制软件,对于初学者是一个上手快,操作简单的EDA软件。

Tanner集成电路设计软件是由Tanner Research 公司开发的基于Windows 平台的用于集成电路设计的工具软件。

该软件功能十分强大,易学易用,包括S-Edit,T-Spice,W-Edit,L-Edit与LVS,从电路设计、分析模拟到电路布局一应俱全。

其中的L-Edit版图编辑器在国内应用广泛,具有很高知名度。

L-Edit Pro是Tanner EDA软件公司所出品的一个IC设计和验证的高性能软件系统模块,具有高效率,交互式等特点,强大而且完善的功能包括从IC设计到输出,以及最后的加工服务,完全可以媲美百万美元级的IC设计软件。

L-Edit Pro包含IC设计编辑器(Layout Editor)、自动布线系统(Standard Cell Place & Route)、线上设计规则检查器(DRC)、组件特性提取器(Device Extractor)、设计布局与电路netlist的比较器(LVS)、CMOS Library、Marco Library,这些模块组成了一个完整的IC设计与验证解决方案[2]。

L-Edit Pro 丰富完善的功能为每个IC设计者和生产商提供了快速、易用、精确的设计系统。

2、3、4输入或非门版图设计

《集成电路工艺与版图设计》课堂作业班级:电子科学与技术01班姓名:曾海学号:201031722、3、4输入异或门版图设计如下:一、二输入异或门:(1)原理图:<2>L-edit中进行设计的如下二输入或非门版图<3>提取后在T-SPICE中进行参数及输入输出设置如下:VA A GND BIT ({1011} pw=20N lt=10N ht=10N on=5 off=0)VB B GND BIT ({0010} pw=20N lt=10N ht=10N on=5 off=0)Vdd Vdd GND 5.tran 10N 100N.print tran v(OUT) v(A) v(B)<4>在W-EDIT中得到仿真波形图:二、三输入或非门<1>三输入异或门版图<3>参数及输入输出设置VA A GND BIT ({1011} pw=20N lt=10N ht=10N on=5 off=0) VB B GND BIT ({0010} pw=20N lt=10N ht=10N on=5 off=0)Vdd Vdd GND 5.tran 10N 100N.print tran v(OUT) v(A) v(B)<3>仿真图三、四输入或非门<1>版图设计<2>参数及输入输设置Vdd Vdd GND 5VA A GND BIT ({1001} pw=20N lt=10N ht=10N on=5 off= 0)VB B GND BIT ({1010} pw=20N lt=10N ht=10N on=5 off= 0)VC C GND BIT ({1011} pw=20N lt=10N ht=10N on=5 off= 0)VD D GND BIT ({1011} pw=20N lt=10N ht=10N on=5 off= 0).tran 20N 100N.print tran v(OUT) v(A) v(B) v(C) v(D)<3>仿真图4、版图设计总结(1)本次设计中,由仿真图可以看出,仿真波形不是标准的方波图形,而是有相应的误差,可能是由于版图的设计中,布线或器件的放置不合理导致的。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

《集成电路工艺与版图设计》课堂作业

班级:电子科学与技术01班

姓名:曾海

学号:20103172

2、3、4输入异或门版图设计如下:

一、二输入异或门:

(1)原理图:

<2>L-edit中进行设计的如下二输入或非门版图

<3>提取后在T-SPICE中进行参数及输入输出设置如下:

VA A GND BIT ({1011} pw=20N lt=10N ht=10N on=5 off=0)

VB B GND BIT ({0010} pw=20N lt=10N ht=10N on=5 off=0)

Vdd Vdd GND 5

.tran 10N 100N

.print tran v(OUT) v(A) v(B)

<4>在W-EDIT中得到仿真波形图:

二、三输入或非门

<1>三输入异或门版图

<3>参数及输入输出设置

VA A GND BIT ({1011} pw=20N lt=10N ht=10N on=5 off=0) VB B GND BIT ({0010} pw=20N lt=10N ht=10N on=5 off=0)

Vdd Vdd GND 5

.tran 10N 100N

.print tran v(OUT) v(A) v(B)

<3>仿真图

三、四输入或非门

<1>版图设计

<2>参数及输入输设置

Vdd Vdd GND 5

VA A GND BIT ({1001} pw=20N lt=10N ht=10N o n=5 off=0)

VB B GND BIT ({1010} pw=20N lt=10N ht=10N o n=5 off=0)

VC C GND BIT ({1011} pw=20N lt=10N ht=10N o n=5 off=0)

VD D GND BIT ({1011} pw=20N lt=10N ht=10N o n=5 off=0)

.tran 20N 100N

.print tran v(OUT) v(A) v(B) v(C) v(D)

<3>仿真图

4、版图设计总结

(1)本次设计中,由仿真图可以看出,仿真波形不是标准的方波图形,而是有相应的误差,可能是由于版图的设计中,布线或器件的放置不合理导致的。

通过这次设计,我深感自己的不足,特别是在画版图方面,容易出错,花费时间也长,需要加强这方面的练习已达到更加熟练地掌握版图的设计。

(2)通过本次设计,是我了解到,只有更加深入里理解电路的原理及集成电路的制造过程,才能更好更准确你设计出地电路版图

(注:可编辑下载,若有不当之处,请指正,谢谢!)。