16设计和开输入输出

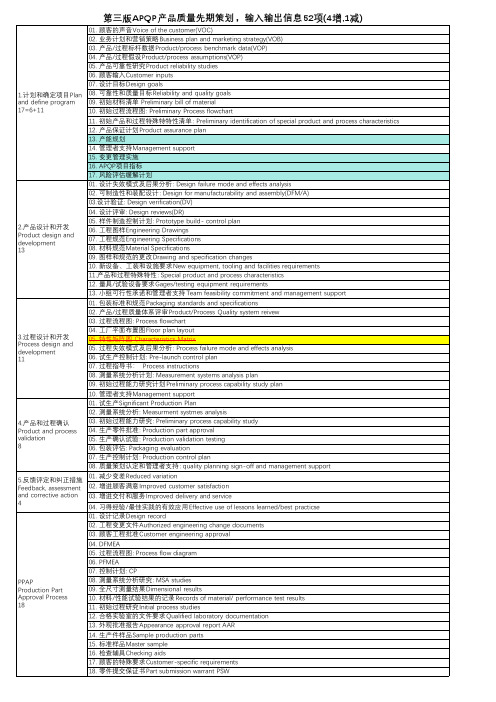

第3版APQP输入输出信息资料

PPAP Production Part Approval Process 18

01. 设计记录Design record 02. 工程变更文件Authorized engineering change documents 03. 顾客工程批准Customer engineering approval 04. DFMEA 05. 过程流程图: Process flow diagram 06. PFMEA 07. 控制计划: CP 08. 测量系统分析研究 : MSA studies 09. 全尺寸测量结果Dimensional results 10. 材料/性能试验结果的记录 Records of material/ performance test results 11. 初始过程研究Initial process studies 12. 合格实验室的文件要求 Qualified laboratory documentation 13. 外观批准报告Appearance approval report AAR 14. 生产件样品Sample production parts 15. 标准样品Master sample 16. 检查辅具Checking aids 17. 顾客的特殊要求Customer-specific requirements 18. 零件提交保证书Part submission warrant PSW

35

DFM/A

36 2.2 产品开发

设计验证

37

设计评审

38

产品和过程特殊特性清案

40 2.4 样件制造 41

样件-CP A-8样件-CP检查清单

42 2.5 工程图样

工程图样

43 2.6 工程规范

顾客技术协议工程规范

groth16 电路设计

groth16 电路设计

Groth16是一种零知识证明系统,它可以用于验证某些信息的真实性而不泄露具体的信息内容。

在Groth16电路设计中,通常涉及到将特定的计算或验证过程转化为电路的形式,以便能够在硬件或软件中进行运算和验证。

这种电路设计通常需要考虑到性能、安全性和可扩展性等方面的因素。

在进行Groth16电路设计时,需要考虑以下几个方面:

1. 功能需求,首先需要明确电路的功能需求,包括需要进行的计算或验证过程以及所涉及的输入和输出数据。

2. 电路架构设计,根据功能需求,设计电路的整体架构,包括各个模块之间的连接方式、数据流向以及可能涉及的并行计算等。

3. 逻辑设计,在电路的各个模块中,需要进行逻辑设计,确定各种逻辑门、寄存器、存储器等元件的布局和连接方式,以实现所需的功能。

4. 时序设计,在电路设计中需要考虑时序问题,包括各个信号

的传播延迟、时钟频率等,以确保电路的正确运行。

5. 性能优化,针对Groth16电路设计,还需要考虑性能优化的

问题,包括减小电路的延迟、减小面积占用、降低功耗等方面的优化。

6. 安全性考虑,由于Groth16通常用于安全验证,因此在电路

设计中需要考虑安全性的问题,包括防止信息泄露、抵抗攻击等方

面的考虑。

总之,Groth16电路设计涉及到硬件电路设计和逻辑设计等方面,需要综合考虑功能需求、性能优化和安全性等多个方面的因素。

希望这些信息能够对你有所帮助。

16点输入模块的应用场景

16点输入模块的应用场景

16点输入模块是指具有16个输入通道的数字输入模块,它可

以在许多不同的领域和应用中发挥作用。

首先,16点输入模块常常被用于工业自动化领域。

在工业控制

系统中,这种模块可以用来接收来自传感器、开关或其他设备的信号,然后将这些信号传输给控制器或监控系统。

例如,它可以用于

监测温度、压力、液位、流量等参数,并将这些数据传输给控制系统,从而实现对生产过程的监控和控制。

其次,16点输入模块也常见于建筑自动化系统中。

在建筑物中,它可以用于接收来自各种传感器的信号,比如门窗状态、照明控制、安全系统等。

通过这些输入模块,建筑物的自动化系统可以实现对

各种设备和系统的监控和控制,提高建筑物的安全性和能效性。

此外,16点输入模块还可以应用于环境监测系统中。

比如气象站、环境监测站等场合,它可以用来接收各种环境参数的信号,比

如温度、湿度、风速、气压等,然后将这些数据传输给监测系统进

行分析和处理,以便及时预警和监测环境变化。

总之,16点输入模块在工业控制、建筑自动化、环境监测等领域都有着广泛的应用场景,它可以帮助实现对各种信号和数据的采集、传输和处理,从而实现对各种系统和设备的监控和控制。

09设计开发输入或输出资料清单

09设计开发输入或输出资料清单设计开发输入清单编号:JL-C2-02 序号: 项目名称后吊架总成型号规格 SY6480 序号文件资料或实物名称类别数量备注 1 后吊架总成 1706030-01图纸 1张顾客财产 2 后吊座底板 1706031-01图纸 1 顾客财产 3 后吊座大管 1706050-01图纸 1 顾客财产 4 后吊座中管 1706050-01图纸 1 顾客财产 5 后吊座细管 1706050-01图纸 1 顾客财产 6 落料模 1706031-01-1/3模具 2套顾客财产 7 压弯模1706031-01-2/3模具 2套顾客财产 8 冲孔模 1706031-01-3/3模具 2套顾客财产 9 焊接夹具 1706031-01夹具 3套顾客财产 10 压装模 1706031-01模具1套顾客财产 11 检验量具 1706031-01量具 1套顾客财产用后返回1份 12 顾客合同1份 13 制造可行性评审报告1份 14 制造成本目标1份 15 生产率目标1份 16 制造过程能力目标备注:编制,陈九春 2007年4月20日设计开发输出清单编号:JL-C2-02 序号: 项目名称后吊架总成型号规格 SY6480 序号文件资料或实物名称类别数量 1 后吊架总成转换产品图 8 2 后吊座底板转换产品图 8 3 后吊座大管 8 转换产品图4 后吊座中管 8 转换产品图5 后吊座细管 8 转换产品图6 冲压作业指导书(落料) 工艺文件 87 冲压作业指导书(压弯) 88 冲压作业指导书(冲孔) 8 9 机械加工工艺过程卡片 8 10 8 机械加工工艺过程卡片11 8 机械加工工艺过程卡片8 12 焊接作业指导书13 铆合作业指导书 814 检验指导书 815 检验指导书 816 材料清单 317 制造过程特性清单 318 CPK计算 319 生产率目标 320 制造成本目标 3 备注:编制:陈九春 2007年5月26日。

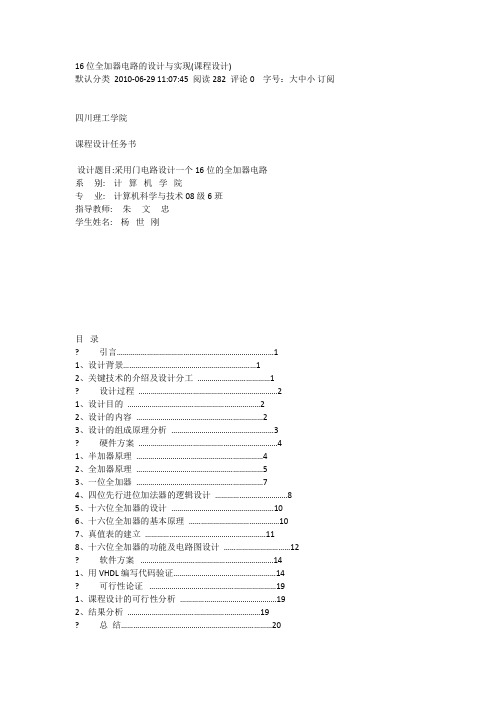

16位全加器电路的设计与实1

16位全加器电路的设计与实现(课程设计)默认分类2010-06-29 11:07:45 阅读282 评论0 字号:大中小订阅四川理工学院课程设计任务书设计题目:采用门电路设计一个16位的全加器电路系别: 计算机学院专业: 计算机科学与技术08级6班指导教师: 朱文忠学生姓名: 杨世刚目录? 引言 (1)1、设计背景 (1)2、关键技术的介绍及设计分工 (1)? 设计过程 (2)1、设计目的 (2)2、设计的内容 (2)3、设计的组成原理分析 (3)? 硬件方案 (4)1、半加器原理 (4)2、全加器原理 (5)3、一位全加器 (7)4、四位先行进位加法器的逻辑设计 (8)5、十六位全加器的设计 (10)6、十六位全加器的基本原理 (10)7、真值表的建立 (11)8、十六位全加器的功能及电路图设计 (12)? 软件方案 (14)1、用VHDL编写代码验证 (14)? 可行性论证 (19)1、课程设计的可行性分析 (19)2、结果分析 (19)? 总结 (20)1、实验结论 (20)? 参考文献 (21)? 引言设计的背景:全加器的运用是相当的广泛的,像各种各样的CPU和某些模型机,然而对于快速正确的加法器的设计是相当的重要的,所以在这次课程设计我选择对全加器的设计与实现。

总的来说多位加法器的构成有两种方式:并行进位(又叫超前进位)和串行进位方式。

并行进位加法器设有并行进位产生逻辑,运算速度快;串行进位方式是将全加器级联构成多位加法器。

并行进位的并行加法器又可以分为组内并行、组间串行的进位链和组内并行、组间并行的进位链。

通常,并行加法器比串行级联加法器占用更多的资源,并且随着位数的增加,相同位数的并行加法器比串行加法器的资源占用差距也会越来越大。

它们的目的就是要进位信号的产生尽可能的快,因此产生了二重进位链或更高重进位链,显然进位速度的提高是以硬件设计的复杂化为代价来实现的。

另外一个器件需要进一步的更新换代,在我们所学的知识领域里面,我们认为应该需要两个方面,一个是设计,有一个好的设计,它就像一种需求一样,即使这种设计在实际上暂时无法得到应用,但是,在一定时期以后,它是可以实现的。

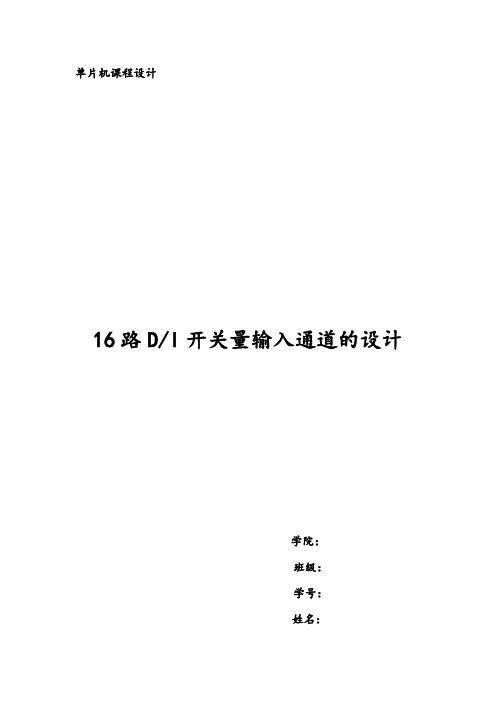

16路DI开关量输入通道的设计

单片机课程设计16路D/I开关量输入通道的设计学院:班级:学号:姓名:16路D/I 开关量输入通道的设计一. 设计目的与任务选择24V 电源输入,设计16路D/I 开关输入通道。

二. 设计中所需软件及设备PC 机电脑、Keil C 软件、Protues 软件。

本次设计所需软件为Keil C51以及Proteus ISIS 仿真软件,应用Proteus ISIS 对实验电路进行仿真,得到实验结果。

三.设计原理说明1.实验方案设计图由于是16路的24V 电源输入,所以不能直接将24V 电源输入到单片机,故需要有隔离或转换电路,将16路24V 电源转换为转换为16路的信号输入到单片机I/O 口,由单片机采集16路电平信号。

方案设计结构图如下图2.硬件设计与结构图(1)电源模块电源部分我们采用变压器降压,用整流桥整流为直流,然后滤波。

最后输出24V 直流电压。

(2)单片机接口单片机我们使用最常用的51单片机。

3.元件的型号选择(1)光耦:由于我们的设计是16路输入,故在隔离光耦的选择上因尽量利用最少的元件达到16路输入,通过查阅资料最终选择TLP521普通光耦。

下面是TLP521光耦基本参数:特性最小值典型值最大值单位提供电压 5 24 V转换电流16 25 mA发射极电流 1 10 mA工作温度-25 85 °C光耦元件的内部结构见下图光耦合器的主要优点:信号单向传输,输入端与输出端完全实现了电气隔离隔离,输出信号对输入端无影响,抗干扰能力强,工作稳定,无触点,使用寿命长,传输效率高。

光耦合器现已广泛用于电气绝缘、电平转换、级间耦合、驱动电路、开关电路、斩波器、多谐振荡器、信号隔离、级间隔离、脉冲放大电路、数字仪表、远距离信号传输、脉冲放大、固态继电器(SSR)、仪器仪表、通信设备及微机接口中。

在单片开关电源中,利用线性光耦合器可构成光耦反馈电路,通过调节控制端电流来改变占空比,达到精密稳压目的。

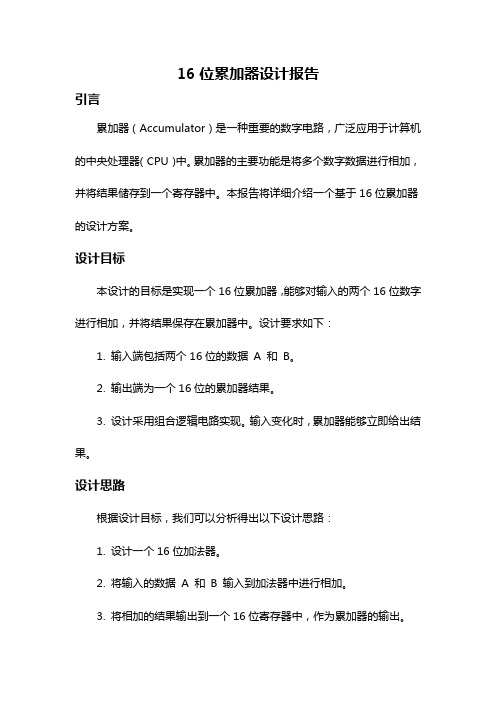

16位累加器设计报告

16位累加器设计报告引言累加器(Accumulator)是一种重要的数字电路,广泛应用于计算机的中央处理器(CPU)中。

累加器的主要功能是将多个数字数据进行相加,并将结果储存到一个寄存器中。

本报告将详细介绍一个基于16位累加器的设计方案。

设计目标本设计的目标是实现一个16位累加器,能够对输入的两个16位数字进行相加,并将结果保存在累加器中。

设计要求如下:1. 输入端包括两个16位的数据A 和B。

2. 输出端为一个16位的累加器结果。

3. 设计采用组合逻辑电路实现。

输入变化时,累加器能够立即给出结果。

设计思路根据设计目标,我们可以分析得出以下设计思路:1. 设计一个16位加法器。

2. 将输入的数据A 和B 输入到加法器中进行相加。

3. 将相加的结果输出到一个16位寄存器中,作为累加器的输出。

16位加法器的设计16位加法器是累加器的核心组件之一。

我们使用全加器来实现16位加法器。

一个全加器能够实现两个输入位和一个进位位的加法,并给出一个输出位和一个进位位。

我们将使用16个全加器来构建16位加法器。

每个全加器的输入为两个加数位和进位位,输出为加法结果和进位结果。

下图是一个全加器的逻辑电路图:plaintext_______AB Full SCi Adder_______Co其中,A 和B 分别是两个输入的加数位,Ci 是输入的进位位,S 是加法结果,Co 是进位结果。

根据全加器的逻辑电路图,我们可以设计一个16位的加法器,将输入的两个16位数字进行相加,并给出16位的输出结果。

累加器的设计基于16位加法器的设计,我们可以构建一个16位累加器。

累加器的设计如下:1. 输入端包括两个16位的数据A 和B。

2. 将输入的两个16位数据A 和B 输入到16位加法器中,进行相加。

3. 将加法器的输出结果输入到一个16位寄存器中,作为累加器的输出。

下图是16位累加器的逻辑电路图:plaintext___________________AB 16-bit Adder___________________Output总结本设计报告介绍了一个基于16位累加器的设计方案。

Vivado设计流程

Vivado设计流程Vivado设计流程以⼀个简单的16位拨码开关的读和16位LED灯的输出电路为例,利⽤Verilog HDL语⾔,在Vivado中创建简单的16位拨码开关的输⼊和16位LED灯的输出电路,将设计下载的Xilinx ⼤学计划ARTIX-7平台。

⼀、新建⼯程1、打开Vivado,然后点击创建⼀个新项⽬(或者在菜单栏选择File->NewProject…),然后点next。

2、输⼊⼯程名称、选择⼯程存储路径,并勾选Create projectsubdirectory选项,为⼯程在指定存储路径下建⽴独⽴的⽂件夹。

设置完成后,点击Next。

最后,如图,整个项⽬将在D:/FPGAprojects/myproject中。

注意:⼯程名称和存储路径中不能出现中⽂和空格,建议⼯程名称以字母、数字、下划线来组成。

3、选择RTL Project⼀项,并勾选Do not specify sources at this time,勾选该选项是为了跳过在新建⼯程的过程中添加设计源⽂件。

点击Next。

4、根据使⽤的FPGA开发平台,选择对应的FPGA⽬标器件。

Nexys4开发板请选择Artix-7 XC7A100TCSG324-1的器件,即Family和Subfamily均为Artix-7,封装形式(Package)为CSG324,速度等级(Speed grade)为-1,温度等级(Temp Grade)为C)。

点击Next。

5、确认相关信息与设计所⽤的的FPGA器件信息是否⼀致,⼀致请点击Finish,不⼀致,请返回上⼀步修改。

6、得到如下的空⽩Vivado⼯程界⾯,完成空⽩⼯程新建。

⼆、设计⽂件输⼊1、点击Flow Navigator下的Project Manager->Add Sources或中间Sources中的对话框打开设计⽂件导⼊添加对话框。

2、选择第⼆项Add or Create Design Sources,⽤来添加或新建Verilog或VHDL源⽂件,点击Next。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

设计和开发输入输出控制程序

Q/PTC-QP 7.3-02-08

1 目的

本程序为了规范公司产品设计和开发输入输出的过程管理,以确保公司产品设计和开发的输入输出能满足规定的要求。

2 范围

本程序适用于公司军品,特种车辆、工程机械、铁路货车等民用产品设计和开发输入输出的控制。

3 术语

3.1 设计和开发输入:与产品有关的性能要求、功能要求、说明性要求、环境要求、安全要求和法规要求等文件。

通常以技术指标、研制合同、研制任务书等形式下达。

3.2 设计和开发输出:通过设计和开发过程,将设计和开发输入转变为图样、技术规范、服务规范、计算报告等供采购、生产、检验和试验、服务等过程所使用的最终技术文件。

4 职责

4.1 发展规划部综合计划处是公司设计和开发输入、输出过程的归口管理部门;负责公司军品设计和开发输入、输出工作的组织与协调;负责公司军品设计和开发输入文件的制定和下达。

4.2 事业部计划部门负责本事业部民品设计和开发输入、输出工作的组织与协调;负责本事业部民品设计和开发输入文件的制定和下达。

4.3 技术部技术管理处负责公司军品过程设计和开发输入、输出的业务管理,并组织实施与控制;负责公司军品设计定型后的设计和开发输入、输出文件的归档、保管、发放和回收等工作。

4.4 技术部军品研究所负责公司军品产品设计和开发输入、输出的业务管理,并组织实施与控制。

4.5 事业部技术部门负责民品设计和开发输入、输出的业务管理,并组织实施与控制;负责本事业部民品设计和开发输入、输出文件的归档、保管、发放和回收等工作。

4.6 公司各有关单位负责配合完成设计和开发输入、输出过程的各项工作。

1

Q/PTC-QP7.3-02-08

5 工程程序

5.1 设计和开发的输入

5.1.1 确定输入的内容

51.1.1 与产品有关的性能要求、功能要求、说明性要求、环境要求、安全要求、法规要求,以及产能、成本、质量等要求。

通常以技术指标、研制合同、研发任务书等形式下达。

5.1.1.2 在下达产品设计输入文件之前,军品由发展规划部综合计划处负责与技术部军品研究所、技术部技术管理处、财务部财务处、发展规划部军品处、质量部质量管理处、经济运行部生产管理处等相关单位沟通;民品由事业部的计划部门负责与本事业部的销售部门、质量部门、技术部门、生产部门、财务部门等单位进行沟通,以确保输入文件的充分性。

设计和开发的输入文件内容,应包括:

a)功能和性能要求;

b)适用的法律法规要求;

c)以前类似设计成功的和成熟技术的有关信息;

d)设计和开发策划中所必须的其他要求,如标准化要求、设计满足易加工、易使用维护、便于保障及需配置的保障资源等要求;

e)成本目标;

f)产能目标;

g)质量目标;

h)可靠性目标;

i)进度目标等。

5.1.2 记录确定的输入

5.1.2.1发展规划部综合计划处或事业部计划部门根据以上确定的输入内容,以下达设计和开发输入文件的方式,记录确定的各项输入内容,并标明其出处或来源,以便于追溯。

5.1.2.2 下达的设计和开发输入文件,其形式可用:

a)技术指标;

b)研制(设计)任务书;

c)研制合同书;

d)设计、试验应遵循的准则和规范等。

2

Q/PTC-QP7.3-02-08

5.1.2.3 下达的设计和开发输入文件军品由技术部军品研究所和技术管理处接收,民品由承制事业部技术部门接收。

产品设计和开发输入文件应作为产品技术文件按《文件控制程序》规定要求,归档保管。

5.1.3设计输入的评审

5.1.3.1 发展规划部综合计划处或事业部计划部门在签订或下达设计和开发输入文件之前;应组织对设计输入文件进行评审,确保输入文件的充分性、适宜性、和可行性,并做好评审记录。

5.2 设计和开发的输出

5.2.1 设计和开发阶段的输出应当包括以下等文件:

a) 产品图样;

b) 设计计算和分析报告;

c) 技术规范;

d) 材料规范;

e) 验收技术规范、试验方法、验收准则;

f) 使用维护说明书;

g) 量具或试验设备要求;

h) 关键件(特性)、重要件(特件)项目明细表;

i) 关键、重要工序明细表;

j) 可靠性分析;

k) 工艺规范等。

5.2.2 输出文件的要求

5.2.2.1 编制的产品技术要求或产品规范,应阐明产品设计和开发输出的内容、并能对其进行输入的符合性验证,证实其满足设计和开发输入的要求。

对涉及的原材料、外购件等采购产品提出明确的要求,可通过编制采购产品的目录提出要求。

5.2.2.2 编制的产品图样、技术规范、过程工艺规范等文件,应明确提出生产和服务提供所需的要求,作为生产和服务提供应实现的目标。

5.2.2.3 编制的制造验收技术条件等文件,应明确产品接收的项目、要求、检验方法、合格证明等产品的接收准则,为产品的符合性判定以及所要求的验证、确认、监视、检验和试验以及产品放行提供准则。

5.2.2.4 对涉及到产品的安全和正常使用的操作要求或常见故障的一般判定和处

3

Q/PTC-QP7.3-02-08

置方法等,应在相关输出文件,如产品使用说明书中做出明确规定。

5.2.2.5 编制《关键件(特性)、重要件(特性)汇总表》,并在产品图和有关的设计文件中做出相应标识。

5.2.2.6 根据产品的特点或顾客的要求,在输出文件中,规定产品使用所必需的保障方案和保障资源要求。

5.2.2.7 输出的图样和技术规范等应符合有关标准的规定。

5.2.2.8 军品定型阶段的输出文件,应满足GJB 1362-1992《军工产品定型程序和要求》中定型文件的要求。

5.2.3 输出文件的评审

技术部军品研究所、技术管理处或事业部技术部门应对设计和开发阶段的输出文件进行评审,并做好评审记录,具体按《设计和开发评审控制程序》执行。

5.2.4 设计输出文件审签

产品设计和开发输出文件在发放前应按文件要求进行审签、工艺和质量会签、标准化检查。

具体按《文件控制程序》的规定进行。

5.2.5 输出文件的归档与管理

5.2.5.1军品设计和开发各阶段形成的输出文件由技术部军品研究所负责管理,设计定型后的输出文件由技术部技术管理处规定进行管理。

5.2.5.2 民品设计和开发各阶段形成的输出文件由各事业部技术部门负责管理。

5.2.5.3 输入文件的管理具体按《文件控制程序》的规定执行。

6 主要质量记录

6.1 设计输入的相关文件

6.2 评审有关的记录

6.3 设计输出的相关文件

7 引用文件

7.1 Q/PTC-QP 4.2-01-08 《文件控制程序》

7.3 Q/PTC-QP 7.3-03-08 《设计和开发评审控制程序》

7.4 GJB 1362-1992 《军工产品定型程序和要求》

4。