74ls138二进制译码器ppt

74ls138二进制译码器_ppt课件

因此,正确连接控制输入端使译码器处于工作 状态,将 Y1 、Y3 、Y5 、Y6 、Y7 经一个与非门输 出,A2、A1、A0分别作为输入变量A、B、C,就可实 现组合逻辑函数。

F (A, B,C) m(1,3,5,6,7)

Y1 Y3 Y5 Y6 Y7

仿真

图3-10 例3-4电路图

S为控制端

(又称使能端)

S=1 译码工作

S=0 禁止译码,

输出全1

S S1 S2 S3

为便于理解功能

而分析内部电路

译码输入端

Y内i 部S电 m路i (图i 0,1,2,7)

输出端

高电平 有效

表3-6 74LS138的功能表

低电平 有效

禁止 译码

译 码 工 作

译中为0低电平有 Fra bibliotek输出Yi S mi (i 0,1,2,7)

2. 应用举例

A3 =0时,片Ⅰ工作,片Ⅱ禁止

(1)功能扩展(利用使能端实现)

仿真

扩展位 控制

图使3能-9 端用两片A734=LS11时38,译片码器Ⅰ构禁成止4线,—片16Ⅱ线工译作码器

(2) 实现组合逻辑函数F(A,B,C)

F(A, B,C) mi (i 0 ~ 7)

3.3.1 二进制译码器

输入:二进制代码(N位), 输出:2N个,每个输出仅包含一个最小项。

输入是三位二进 制代码、有八种状态, 八个输出端分别对应 其中一种输入状态。 因此,又把三位二进 制译码器称为3线—8 线译码器。

图3-7 三位二进制译码器的方框图

1. 74LS138的 逻辑功能 仿真

负逻辑 与非门

F(A, B,C) m(1,3,5,6,7)

74LS138译码器引脚图逻辑图及功能表

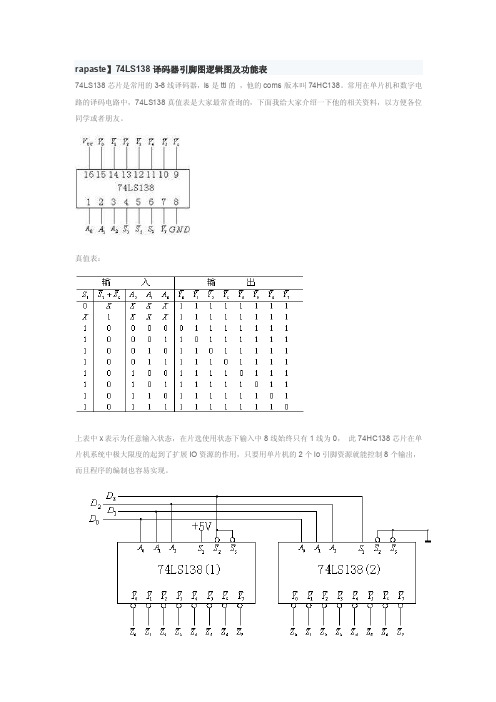

rapaste】74LS138译码器引脚图逻辑图及功能表

74LS138芯片是常用的3-8线译码器,ls是ttl的,他的coms版本叫74HC138。

常用在单片机和数字电路的译码电路中,74LS138真值表是大家最常查询的,下面我给大家介绍一下他的相关资料,以方便各位同学或者朋友。

真值表:

上表中x表示为任意输入状态,在片选使用状态下输入中8线始终只有1线为0,此74HC138芯片在单片机系统中极大限度的起到了扩展IO资源的作用,只要用单片机的2个io引脚资源就能控制8个输出,而且程序的编制也容易实现。

拓展

式(3.3.8)表明时第(1)片74LS138工作而第(2)片74LS138禁止,将的0000~0111这8个代码译成8个低电平信号。

而式(3.3.9)表明时,第(2)片74LS138工作,第(1)片74LS138禁止,将的1000~1111这8个代码译成8个低电平信号。

这样就用两个3线-8线译码器扩展成一个4线-16线的译码器了。

同理,也可一用两个带控制端的4线-16线译码器接成一个5线-32线译码器。

例2.74LS138 3-8译码器的各输入端的连接情况及第六脚()输入信号A的波形如下图所示。

试画出八个输出引脚的波形

解:由74LS138的功能表知,当(A为低电平段)译码器不工作,8个输出引脚全为高电平,当(A为高电平段)译码器处于工作状态。

因所以其余7个引脚输出全为高电平,因此可知,在输入信号A的作用下,8个输出引脚的波形如下:

即与A反相;

其余各引脚的输出恒等于1(高电平)与A的波形无关。

实验4组合逻辑器件的应用(I)-译码器及其应用—74LS138、74LS148

3 实验设备与器件

3 实验设备与器件

KHM-2B型模拟实验装置

4 实验内容及步 骤

4 实验内容及步骤

实验项目

74LS138译码器逻辑功能测试; 用74LS138构成时序脉冲分配器; 用两片74LS138构成一个4-16线译码器(两组结合); 74LS148优先编码器的逻辑功能测试。 数码显示小实验。

掌握用集成译码器、编码器组合逻辑电路的

方法;

熟悉数码管的使用。

2 实验原理

2 实验原理

译码器

一个多输入、多输出的组合逻辑电路;

作用:“翻译”;

用途:1. 代码转换 2. 终端数字显示 3. 数据分配

4. 存储器寻址 5. 组合控制信号;

分类:通用译码器和显示译码器,通用译码器又有变 量译码器、代码变换译码器。

4 实验内容及步骤

5 实验报告要求

5 实验报告要求

复习有关译码器和分配器的原理; 用译码器、优先译码器对实验内容中各函数式进行

预设计。

认真仔细、整洁干净、内容充实、数据准确

下次实验内容:组合逻辑电路的应用-74LS151/153

谢谢!

2 实验原理

74LS138组合4/16译码器

如图,问第一片和第二片分别负责哪些状态?

2 实验原理

8-3线优先编码器-74LS148

74LS148的逻辑图和引脚图

真值表

2 实验原理

数码显示译码器

LED数码管

(a)共阴 (b)共阳

2 实验原理

数码显示译码器

BCD码七段译码驱动器

引脚图

Z A B C A B C A BC ABC

Y0 A2 A1 A0 Y1 A2 A1 A0 Y2 A2 A1 A0 Y3 A2 A1 A0

数字电路译码器PPT课件

(2) 写出标准与—或表达式→与

S1

非表达式。

S2

Y1 ABC ABC C

S3

= ABC ABC ABC ABC ABC

74LS138

= m1 m3 m5 m6 m7

Y 9 A3 A2 A1A0 …

Y 15 A3 A2 A1A0

第27页/共45页

A

S1

S2

S3

D

C B

(4) 画连线图

令A3=A、A2=B、A1=C、A0=D

S1 S2 S3

& Y

第28页/共45页

6.2.3 显示译码器

能够显示数字的器件称为数字显示器。 显示译码器----将与数字对应的二进制代码翻译成数字 显示器所能识别的信号的译码器。

Y3 A2 A1A0 m3

Y4 A2 A1 A0 m4

Y5 A2 A1A0 m5

令A2=A、A1=B、A0=C

Y6 A2 A1 A0 m6 Y7 A2 A1A0 m7

Y m1m3 m5 m6 m7 Y1Y 3Y 5Y 6Y 7

Y2 m0 m7 Y 0Y 7

第24页/共45页

第26页/共45页

(3) 将逻辑函数式和4-16译码器输出表达式比较

Y 0 A3 A2 A1A0

Y 1 A3 A2 A1A0 Y 2 A3 A2A1A0 … Y 7 A3A2 A1A0

Y 8 A3 A2 A1A0

令A3=A、A2=B、A1=C、A0=D

F m0 m1m3 m14 m15 Y 0Y 1Y 3Y 14Y 15

S1

74ls138译码器引脚图

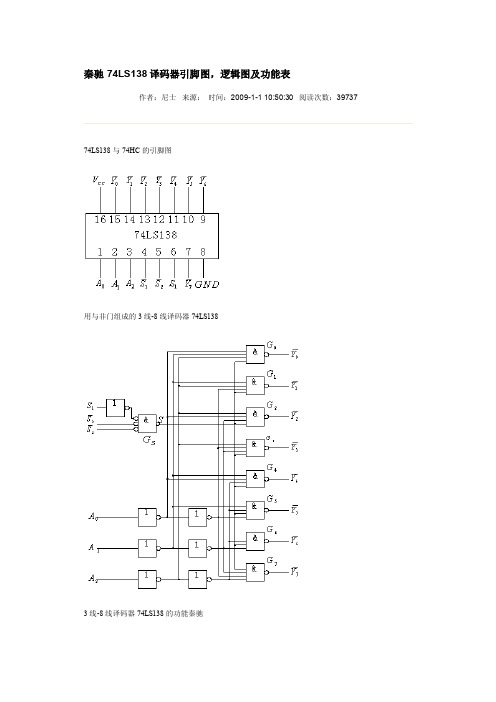

秦驰74LS138译码器引脚图,逻辑图及功能表作者:尼士来源:时间:2009-1-1 10:50:30 阅读次数:39737 74LS138与74HC的引脚图用与非门组成的3线-8线译码器74LS1383线-8线译码器74LS138的功能秦驰无论从逻辑图还是功能表我们都可以看到74LS138的八个输出引脚,任何时刻要么全为高电平1—芯片处于不工作状态,要么只有一个为低电平0,其余7个输出引脚全为高电平1。

如果出现两个输出引脚同时为0的情况,说明该芯片已经损坏。

当附加控制门的输出为高电平(S=1)时,可由逻辑图写出由上式可以看出,同时又是这三个变量的全部最小项的译码输出,所以也把这种译码器叫做最小项译码器。

71LS138有三个附加的控制端、和。

当、时,输出为高电平(S=1),译码器处于工作状态。

否则,译码器被禁止,所有的输出端被封锁在高电平,如表3.3.5所示。

这三个控制端也叫做“片选”输入端,利用片选的作用可以将多篇连接起来以扩展译码器的功能。

带控制输入端的译码器又是一个完整的数据分配器。

在图3.3.8电路中如果把作为“数据”输入端(同时),而将作为“地址”输入端,那么从送来的数据只能通过所指定的一根输出线送出去。

这就不难理解为什么把叫做地址输入了。

例如当=101时,门的输入端除了接至输出端的一个以外全是高电平,因此的数据以反码的形式从输出,而不会被送到其他任何一个输出端上。

【例3.3.2】试用两片3线-8线译码器74LS138组成4线-16线译码器,将输入的4位二进制代码译成16个独立的低电平信号。

解:由图3.3.8可见,74LS138仅有3个地址输入端。

如果想对4位二进制代码,只能利用一个附加控制端(当中的一个)作为第四个地址输入端。

取第(1)片74LS138的和作为它的第四个地址输入端(同时令),取第(2)片的作为它的第四个地址输入端(同时令),取两片的、、,并将第(1)片的和接至,将第(2)片的接至,如图3.3.9所示,于是得到两片74LS138的输出分别为图3.3.9 用两片74LS138接成的4线-16线译码器式(3.3.8)表明时第(1)片74LS138工作而第(2)片74LS138禁止,将的0000~0111这8个代码译成8个低电平信号。

译码器和编码器.ppt

优先编码器 优先编码器是数字系统中实现优先权管理的一个重要逻辑部件。 没有普通编码器的输入使用限制 编码群输出端

使能端 扩展端

权值由高到低

反 码 输 出

例7.7 由148构成16级不同中断请求的中断优先编码器

2

1

7.1.3 多路选择器和多路分配器 功能:完成对多路数据的选择与分配、在公共传输线上实现多路 数据的分时传送。

7.1.2 译码器和编码器

编码器:对输入信号按一定规律进行编排,使每组输出代码具 有一特定的含义. 译码器:对具有特定含义的输入代码进行“翻译”,将其转换 成相应的输出信号.

1、译码器

常见译码器:二进制译码器、二-十进制译码器和数字显示译 码器。

二进制译码器有n 个输入

如:74ls138、T4138等

典型计数器实例之1------T4193(4位二进制同步可逆计数器)

高电平有效清零端 低电平有效预制端

上升沿触发

异步清零

异步置数

同步计数 计数器的作用是不但可以用来计数,还可以构成分频器,一 个二进制计数器还可以用来构成任意进制的计数器

一、用193构成小于16进制的计数器

A、构成模10加法计数器 模10加法计数器的状态图如图

193有16个不同的计数状态,如何使其在第十个状态时 就回到初始状态

反馈清零法

B、构成模12减法计数器

初始状态为1111,如何构成电路?

反 馈 置 数 法

一、用193构成大于16进制的计数器

Q Q Q Q Q Q Q Q Q CC A B C D CB A B C DQ

典型计数器实例之2------74LS161(4位二进制同步计数器)

寄存器实例之一:T1194 见书P242

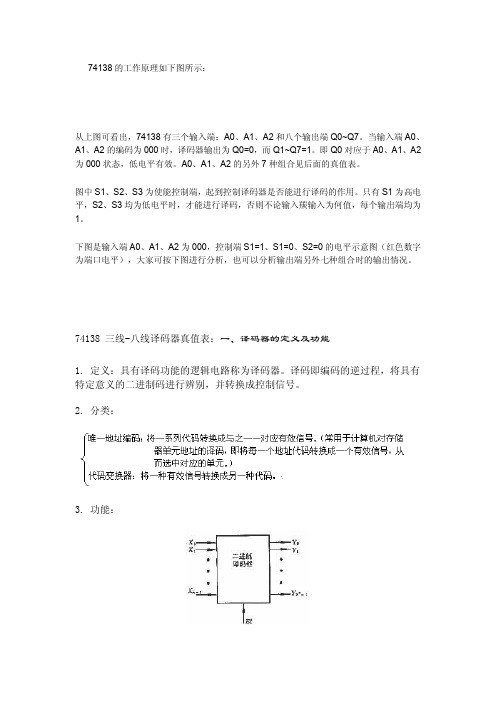

74138的工作原理如下图所示

74138的工作原理如下图所示:从上图可看出,74138有三个输入端:A0、A1、A2和八个输出端Q0~Q7。

当输入端A0、A1、A2的编码为000时,译码器输出为Q0=0,而Q1~Q7=1。

即Q0对应于A0、A1、A2为000状态,低电平有效。

A0、A1、A2的另外7种组合见后面的真值表。

图中S1、S2、S3为使能控制端,起到控制译码器是否能进行译码的作用。

只有S1为高电平,S2、S3均为低电平时,才能进行译码,否则不论输入羰输入为何值,每个输出端均为1。

下图是输入端A0、A1、A2为000,控制端S1=1、S1=0、S2=0的电平示意图(红色数字为端口电平),大家可按下图进行分析,也可以分析输出端另外七种组合时的输出情况。

74138 三线-八线译码器真值表:一、译码器的定义及功能1. 定义:具有译码功能的逻辑电路称为译码器。

译码即编码的逆过程,将具有特定意义的二进制码进行辨别,并转换成控制信号。

2. 分类:3. 功能:二进制译码器一般原理图一个n→2n译码器结构如上图,n个输入端,2n个输出端。

它是一个多输出逻辑组合电路,对每种可能的输入条件,有且仅有一个输出信号为逻辑“1”,所以我们可以把它当作最小项产生器,一个输出就相应于提取一个最小项。

4. 译码器电路结构:首先我们先来分析两输入译码器结构,由于2输入变量A、B共有4种不同状态的组合,因而可以译出4个输出信号,所以简称为2/4线译码器。

2线-4线译码器逻辑图由图可以写出输出端逻辑表达式:根据输出逻辑表达式可以列出功能表。

由表可知,时无论A、B为何种状态,输出全为1,译码器处于非工作状态。

而当时,对应于AB 的某种状态组合,其中只有一个输出量为0,其余各输出量均为1。

例如:AB=0时,输出Y0=0,Y1~Y3=1,由此可见,译码器是通过输出端的逻辑电平来识别不同的代码。

在我们讲述的这种结构中,输出0表示有效电平,所以就叫做低电平有效。

2线-4线译码器功能表二、集成电路译码器1.74138集成译码器下图为常用的集成译码器74LS138的逻辑图和引脚图。

74LS138D译码器真值表仿真以及逻辑分析_数字电子电路分析与应用_[共2页]

![74LS138D译码器真值表仿真以及逻辑分析_数字电子电路分析与应用_[共2页]](https://img.taocdn.com/s3/m/025a68febd64783e08122bca.png)

附录 Multisim 软件介绍及应用实例

– 211 –

2.连接电路

将元件之间用导线连接好,并连接好仪器,得到附图1.5.3所示电路。

附图1.5.3 8421码转余3码电路图

3.仿真结果分析

附图1.5.3中可以看出,输入为“0000”,输出为“0011”,其他的状态可以单击开关来改变输入的值,从而得到对应的输出余3码值,依次如表8.5.1所示,同学们可以依次验证。

附表1.5.1 8421转余3码真值表

1.5.2 74LS138D 译码器真值表仿真以及逻辑分析

74LS138D 译码器真值表的仿真测试可用图1.5.4来实现,即输入部分用单刀双掷开关来改变输入信号的高、低电平,输出用指示灯的亮和灭来指示高低电平的状态,就可看哪个通道处在译码状态。

若该通道就输出低电平(唯一性),该通道对应的输出指示灯就会亮。

也可以调用虚拟仪器工具栏中的字函数信号发生器XWG1和逻辑分析仪XLA2,组成译码器的仿真电路。

字函数信号发生器(Word Generator )是一个最多能产生32位同步数字信号的多路逻辑信号源,也称为数字逻辑信号源。

逻辑分析仪(Logic Analyzer )用于数字逻辑信号的高速采集和时序分析。

1.元件清单、仪器和选取途径

集成3-8译码器74LS138N :Place TTL →74LS →74LS138D 。

电源和地:Place Sources →V CC ;Place Sources →DGND 。

字函数信号发生器:单击虚拟仪器图标即可。

逻辑分析仪:单击虚拟仪器图标即可。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

m1 m 3 m 5 m 6 m 7 m1 m 3 m 5 m 6 m 7 Y1 Y 3 Y 5 Y 6 Y 7

2013年6月1日9时48分 12

因此,正确连接控制输入端使译码器处于工作 状态,将 Y1 、Y3 、Y5 、 6 、 7 经一个与非门输 Y Y 出,A2、A1、A0分别作为输入变量A、B、C,就可实

S S1 S 2 S 3

2013年6月1日9时48分 8

当译码器处于工作状态时,每输入一个二进制代

码将使对应的一个输出端为低电平,而其它输出端均

为高电平。也可以说对应的输出端被“译中”。

74LS138输出端被“译中”时为低电平,所以其逻

辑符号中每个输出端 0~Y7 Y 上方均有“—”符号。

图3-11 二—十进制译码器74LS42的逻辑符号

2013年6月1日9时48分 14

表3-7 二-十进制译码器74LS42的功能表

译中 为0 拒绝 伪码

2013年6月1日9时48分 15

Y i S m i ( i 0 ,1, 2 , 7 )

2013年6月1日9时48分

9

2. 应用举例

A3 =0时,片Ⅰ工作,片Ⅱ禁止

(1)功能扩展(利用使能端实现)

仿真 扩展位 控制 图3-9 用两片74LS138译码器构成4线—16线译码器 A3 =1时,片Ⅰ禁止,片Ⅱ工作 使能端 10 2013年6月1日9时48分

2013年6月1日9时48分 11

例3-4 试用74LS138译码器实现逻辑函数:

F ( A, B , C )

解:因为 则

m (1,3,5 , 6 , 7 )

Y i m i ( i 0 ,1, 2 , 7 )

F ( A, B , C )

m (1,3 ,5 , 6 , 7 )

A1、A0,八个译码输出端 Y0~Y7 ,以及三个控制

端(又称使能端) 1、S2 、 3。 S S S1 、 2 , 3 是译码器的控制输入端,当 S1 S S = 1、 2 + S3 = 0 (即 S1 = 1,S2 和S3 均为0)时,GS S 输出为高电平,译码器处于工作状态。否则,译 码器被禁止,所有的输出端被封锁在高电平。

2013年6月1日9时48分 5 输出端

表3-6 74LS138的功能表

高电平 有效

低电平 有效

禁止 译码 译 码 工 作

译中为0

2013年6月1日9时48分 6

低电平有 效输出

三位二进 制代码

使能端

图3-8 74LS138的逻辑符号

2013年6月1日9时48分

7

74LS138的逻辑功能

三个译码输入端(又称地址输入端)A2、

(2) 实现组合逻辑函数F(A,B,C)

F ( A, B , C )

m i (i 0 ~ 7)

Y i S m i m i ( S 1, i 0 ,1, 2 , 7 )

比较以上两式可知,把3线—8线译码器 74LS138地址输入端(A2A1A0)作为逻辑函数的输 入变量(ABC),译码器的每个输出端Yi都与某一 个最小项mi相对应,加上适当的门电路,就可以利 用译码器实现组合逻辑函数。

3.3

译码器

结束 放映

3.3.1 二进制译码器 3.3.2 二-十进制译码器

2013年6月1日9时48分

1

复习

全班有42名同学,需几位二进制代码才能表示? 为什么要用优先编码器?

2013年6月1日9时48分

2

3.3

译码器

译码: 编码的逆过程,将编码时赋予代码的特 定含义“翻译”出来。 译码器: 实现译码功能的电路。

图3-7 三位二进制译码器的方框图

2013年6月1日9时48分 4

1. 74LS138的 逻辑功能 仿真

负逻辑 与非门

S为控制端 (又称使能端) S=1 译码工作 S=0 禁止译码, 输出全1 S S1 S 2 S 3 为便于理解功能 而分析内部电路 译码输入端

Y 内部电路图 0 ,1, 2 , 7 ) i S m i (i

编码对象

二进制代码

编码 译码

原来信息Biblioteka 常用的译码器有二进制译码器、二-十进制 译码器和显示译码器等。

2013年6月1日9时48分 3

3.3.1 二进制译码器

输入:二进制代码(N位), 输出:2N个,每个输出仅包含一个最小项。 输入是三位二进 制代码、有八种状态, 八个输出端分别对应 其中一种输入状态。 因此,又把三位二进 制译码器称为3线—8 线译码器。

现组合逻辑函数。

F ( A, B , C )

m (1,3,5 , 6 , 7 )

Y1 Y 3 Y 5 Y 6 Y 7

仿真

2013年6月1日9时48分

图3-10 例3-4电路图 13

3.3.2 二-十进制译码器

二—十进制译码器的逻辑功能是将输入的

BCD码译成十个输出信号。