MAX+plus_II教程完整版_new

MaxPlusII简易用户使用入门指南

PPT文档演模板

MaxPlusII简易用户使用入门指南

生成一个图形设计文件

•输入 LPM 符号

lpm (library parameterized megafunction) 符号的输入方法与先前符 号的输入方法相同。 在 Enter Symbol 对话框出现后,在 symbol Libraries 框中选择 “..\maxplus2\max2lib\mega_lpm” 路径。 在 Symbol Files 框中选择您需要的 lpm 符号。 双击参数框 (位于符号的右上角),输入您需要的 lpm 的参数。在 Port Status 框中选择 Unused ,可将您不需门指南

PPT文档演模板

2020/11/2

MaxPlusII简易用户使用入门指南

ES-Site 授权 及 PLS-WEB 特点

•设计输入

•项目编译

•MAX+PLUS II •MAX+PLUS II

•文本编辑器

•图形编辑器

•编译器 •网表提取器

•数据库 •建库器

•项目校验

输入 74 系列的符号

MAX+PLUS II 为实现不同的逻辑功能提供了许多符号,如:图元符 号 ,兆功能符号和宏功能符号。在图形编辑器文件中可直接使用以上 符号。74 系列符号的输入方法和上页图元输入的方法相同。 当 Enter Symbol 对话框出现后,在symbol Libraries 对话框中选 择 “..\maxplus2\max2lib\mf”路径。 在 Symbol Files 对话框中,选择您需要的 74 系列符号。

生成一个图形设计文件

输入 Altera 图元

选择工具按钮有效时,在图 形编辑器窗口的空白处单击 鼠标左键以确定输入位置, 然后选择Enter Symbol,或 双击鼠标左键。

MAX+plusII操作指南

附录一MAX+plusII操作指南完成组合逻辑电路的设计与仿真过程,主要用到以下操作,而且有顺序规定,在编译前需对图形编辑文件保存,并且项目文件必须与图形文件名称一致、保存在同一文件夹,只是后缀不同。

编译正确后才能创建波形文件,波形文件保存后,才能进行仿真,最后进行时序分析。

如中途进行修改,从修改开始的操作步骤要重做一边。

1、建立一个新项目;2、建立一个新的图形输入文件;3、进行图形输入文件的编辑;4、进行项目文件的编译;5、创建波形文件并进行功能仿真;6、进行时序分析。

一、建立一个新项目①启动MAX+plusII:在WINDOWS98界面下,单击开始—程序—Altera—MAX+plusII9.5,进入MAX+plusII9.5管理器窗口,见图1-1。

②用MAX+plusII编译一个设计文件之前,必须先指定一个项目文件,选中File—Project—Name,显示对话框图1-2。

③在Project Name框中,键入项目名,如test1,若改变test1所属子目录,用户可在Directories窗口中修改。

④选择OK,则MAX+plusII9.5窗口标题会变成新的项目名称:MAX+plusIIManager-d:\Max2work\test1。

⑤如已打开一个图形文件,可用菜单File—Project—Set Project To Current File将项目设为与当前图形文件相对应。

注意:换一个电路图,必须重新定义项目名,项目名与文件名必须一致。

图1-1 MAX+plusII9.5管理器窗口图 1-2 建立项目对话框二、 建立一新的图形输入文件在文件菜单中,选中File —New ,出现图1-3对话框New ,New 的对话框供读者选择输入方法:● 图形文件● 符号文件● 文本文件● 波形文件下面介绍的是使用图形输入法。

图1-3新建文件对话框② 选择Graphic Editor file 图形输入文件,选择OK ,则出现一个无名称的图形编辑窗口,如图1-4所示。

MAX+PLUS II操作步骤

1、为本项工程设计建立文件夹 此文件夹被默认为工作库(Work Library) 注意:文件夹名不能用中文,且不可含有 空格。

2、输入源程序 选择菜单File/New….

3、保存 选择File/Save… 注意:(1)保存文件的后缀为.vhd (2)必须保存在新建的文件夹内 (3)保存的文件名必须与实体名保持一 致,否则无法通过编译。

5、创建元件图形符号 选择菜单File /Create Default Symbol, 出现一个对话框,按下“确定”按钮即 可。 6、查看图形符号 选择菜单File/Open… 后缀名为.sym的文件

4、将当前设计设定为工程 (1)选择菜单File/Project/Set Project to Current File,当前设计即可被指定 File 为工程。 (2)选择File/Project/Name

5、check 选择菜单File/Project/save and check 出现错误,双击红色部分,回到程序中改 错,知道通过检查

MaxPlusII使用指南

将当前设计文件设定为工程文件

注意,此路径的指示文件 始终指向当前的工程文件!

开始编译/综合工程文件---半加器

消掉此设置

为顶层设计文件--全加器的设计 另建一原理图编辑窗

设计全加器原理图

存盘!

双击此元件

打开原理 图编辑窗

将当前文件设置

成工程文件!

编译/综合前选定适配元件

消去QUARTUS设 置

使用MAX+PLUS II编译器对Altera器件设计进行编译, 并使用Altera校验工具进行器件或板级仿真。

支持与Synopsys、Viewlogic、Mentor Graphics、Cadence、Exemplar、 Data I/O、Intergraph、Minc、OrCAD等公司提供的工具接口;

选择适配器件

再选择适当的器件, 以下假设所选的器 件是EPF10K10LC84

选择器件系列

编译!

仿真测试全加器的逻辑功能

建立波形 仿真文件

选择波形编辑 器

输入测试信号

输入测试信号

全加器端口信 号

按此键

设置输入信号电平,启动仿真器

启动仿真器

时序仿真

逻辑测 试正确

建立一个新工程

每个设计都都是一个工程,都必须有一个工程名 工程名必须与设计文件名一致(相符)

原理图设计输入 文本设计输入

• 使用 VHDL、AHDL等硬件描述语言

第三方 EDA 工具

EDIF文件

• 利用开发工具FPGA-Express,或SYNPLIFY等生成

OrCAD编辑的原理图,Xilinx公司XNF格式的文件

设计输入文件

VHDL/Verilog AHDL

MAXPLUS2使用教程

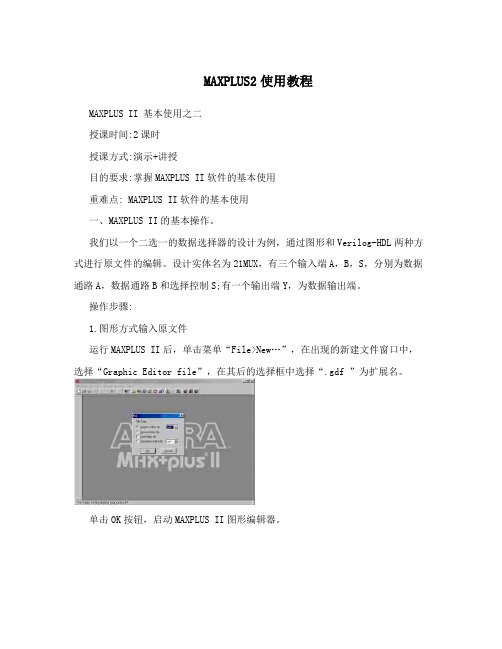

MAXPLUS2使用教程MAXPLUS II 基本使用之二授课时间:2课时授课方式:演示+讲授目的要求:掌握MAXPLUS II软件的基本使用重难点: MAXPLUS II软件的基本使用一、MAXPLUS II的基本操作。

我们以一个二选一的数据选择器的设计为例,通过图形和Verilog-HDL两种方式进行原文件的编辑。

设计实体名为21MUX,有三个输入端A,B,S,分别为数据通路A,数据通路B和选择控制S;有一个输出端Y,为数据输出端。

操作步骤:1.图形方式输入原文件运行MAXPLUS II后,单击菜单“File>New…”,在出现的新建文件窗口中,选择“Graphic Editor file”,在其后的选择框中选择“.gdf ”为扩展名。

单击OK按钮,启动MAXPLUS II图形编辑器。

在上面的图形编辑框中单击右键,在弹出的快捷菜单中选择“Enter Symbol… ”命令,进入Enter Symbol窗口。

在Symbol Library框中双击maxplus2\max2lib\mf所在路径,然后在Symbol Files框中选择21MUX,单击OK按钮。

这时,图形编辑框中出现了一个红框的标名为21MUX的元件。

这就是MAXPLUS II库中自带的一个二选一数据选择器的元件。

按相同方法打开Enter Symbol窗口,双击maxplus2\max2lib\prim所在路径,然后在Symbol Files框中选择input,单击OK按钮。

这时窗口中出现一个红框的输入引脚元件。

按上述方法再输入一个输出引脚元件,其元件名为output。

1接着在按住ctrl键和鼠标左键的同时拖动已有的那个输入引脚元件,在窗口中任意空白处放开。

这样操作一次,就得到已有元件的一个拷贝。

我们在原理图上设置三个输入引脚和一个输出引脚,但这时各输入引脚名称相同,无法区分。

给引脚命名的方法是,用鼠标左键双击引脚的默认引脚名“PIN_NAME”,然后由键盘输入自己的引脚名。

MAXPLUS II简易用户使用入门指南

Max+Plus II简易用户使用入门指南ES-Site授权及PLS-WEB特点深圳市英贝德科技有限公司2004年2月27日第一章 MAX PLUS II的安装运行光盘中的安装程序在开始菜单中选择运行,然后在打开对话框内输入:<CD-ROMdrive>:\pc\maxplus2\install然后按照屏幕上的提示进行操作在安装过程中,如果需要帮助,则选择Help按钮。

当MAX+PLUS II安装成功后,read.me文件将自动出现.它含有一些重要的信息,用户应当仔细阅读它。

第一次运行 MAX+PLUS II双击MAX PLUS II图标或在开始菜单内选择MAX+PLUS II项,开始运行MAX+PLUS II选择ES-Site授权安装第一次运行MAX+PLUS II时,将会出现如下的窗口.选择Essite License按钮。

申请授权代码在您选择ES site license按钮后,出现一个ES Site授权代码申请窗口,如下图所示。

认真填写申请表格,并将其发传真给Altera公司.您将通过电子邮件或传真获得授权代码。

您也可以通过访问Alter公司的www站点: 获得授权代码.MAX+PLUS II管理器窗口ES Site授权有效后,您将返回到MAX PLUS II管理器窗口第二章生成一个图形设计文件1、在File菜单中选择 New2、选择Graphic EditorFile然后按下OK按钮,将会出现一个无标题的图形编辑窗口,如下页所示当选择工具按钮有效时,在图形编辑器窗口的空白处单击鼠标左键以确定输入位置,然后选择Enter Symbol,或双击鼠标左键。

将出现一个Enter Symbol对话框,在symbol Libraries框中选择“..\maxplus2\max2lib\prim”。

所有的Altera图元以列表方式显示出来,选择您想输入的图元,然后选择OK。

输入74系列的符号:MAX+PLUSII为实现不同的逻辑功能提供了许多符号,如:图元符号 ,兆功能符号和宏功能符号。

MAX+plus II使用指导

编程和测试的步骤如下:

(1)选 " MAX+PLUS " 项中的“Programmer”项, 跳出Programmer窗后,选Options项中的硬件设置项 “Hardware Setup”,在此窗的下拉窗中选 “ByteBlaster (MV)”项,点击OK即可。(下载方式 设定:选择MAX+plusII项及其中的编程器 Programmer选项,跳出如图左侧所示的编程器窗口, 然后选择Options项的Hardware Setup硬件设置选项, 其窗口如图左侧所示。在其下拉菜单中选ByteBlaster (MV)编程方式。此编程方式对应计算机的并行口 下载通道,“MV”是混合电压的意思。将实验板连接 好,接好电源,点“Configure”,即进行编程下载。

然后打开MAX+plusII,选择菜单 “File”“New…”,出现对话框,在框中选中 “Text Editor file”,按“OK”按钮,即选中了 文本编辑方式。在出现的“Untitled-Text Editor” 文本编辑窗(图1-1)中键入图1-1所示的 VHDL程序(2选1多路选择器),毕后,选择 菜单“FileSave”,即出现如图1-1所示的 “Save As”对话框。首先在“Directories”目录 框中选择自己已建立好的存放本文件的目录 E:\MUXFILE(用鼠标双击此目录,使其打 开),然后在“File Name”框中键入文件名 “MUX21A.VHD”,按“OK”按钮,即把输入 的文件放在目录E:\MUXFILE中了。

图1-9 在Options选项中消去网格对

图1-10 设定仿真时间宽度

图1-11 设定仿真时间宽度

图1-12为输入信号设定必要的测试电平或数据

MaxplusII入门

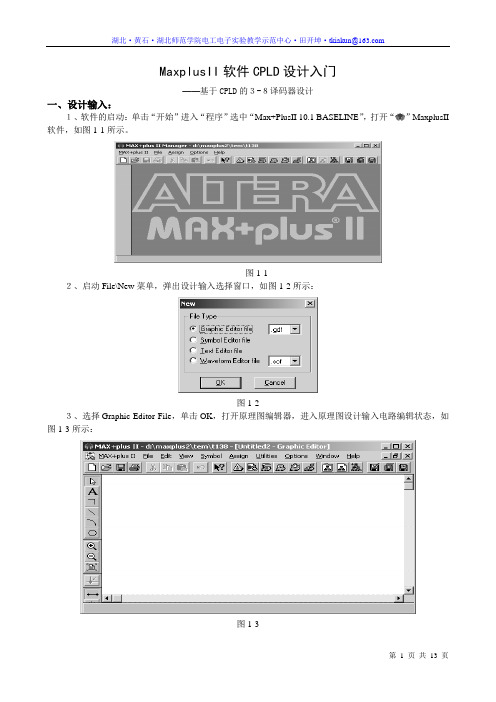

MaxplusII软件CPLD设计入门——基于CPLD的3-8译码器设计一、设计输入:1、软件的启动:单击“开始”进入“程序”选中“Max+PlusII 10.1 BASELINE”,打开“”MaxplusII 软件,如图1-1所示。

图1-12、启动File\New菜单,弹出设计输入选择窗口,如图1-2所示:图1-23、选择Graphic Editor File,单击OK,打开原理图编辑器,进入原理图设计输入电路编辑状态,如图1-3所示:图1-34、设计输入1)放置一个器件在原理图上a、在原理图的空白处双击鼠标左键,出现图1-4。

图1-4b、在光标处输入元件名称(如:input,output,and2,and3,nand2,or2,not,xor,dff等)或用鼠标点击库元件,按下OK即可。

c、如果安放相同的元件,只要按住Ctrl键,同时用鼠标按左键拖动该元件复制即可。

d、一个完整的电路包括:输入端口input、电路元件集合、输出端口output。

e、图1-5为3-8译码器元件安放结果。

图1-52)添加连线到器件的引脚上:把鼠标移到元件引脚附近,则鼠标自动由箭头变为十字,按住鼠标左键拖动,即可画出连线。

3-8译码器原理图连线后如图1-6所示。

图1-63)标记输入/输出端口属性分别双击输入端口的“PINNAME”,当变成黑色时,即可输入标记符并回车确认;输出端口标记方法类似。

本译码器的三输入端分别标记为:A、B、C;其八输出端分别为:D0、D1、D2、D3、D4、D5、D6、D7。

如图1-7所示。

图1-74)保存原理图单击保存按钮图表,对于新建文件,出现类似文件管理器图框,请选择保存路径/文件名称保存原理图,原理图的扩展名为.gdf,本实验中取名为test1.gdf。

(注意:新建项目,一定要建立一个专门的文件夹保存项目文件,在编译过程中将有大量新文件产生。

)5)点击File\Project\Set project to current File设置此项目为当前项目文件,如图1-8所示。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

选 择 mega_lpm 库

选 择 lpm_counter元件

data[ ]: 置入计数器的并行数据输入 clk_en: 高电平使能所有同步操作输入信号 cin: 最低进位输入; clock: 上升沿触发计数时钟输入; updown: 计数器加减控制输入; aclr: 异步清零输入; aset: 异步置位输入; sload: 在的上升沿同步并行数据加载输入; LPM_WIDTH: 计数器位宽; q[ ]: 计数输出; cout: 计数进位或借位输出; cnt_en: 计数使能控制。

2、单击鼠标右键,选择Enter symbol.. 3、选择并双击..\mpeg lpm

4、调出相应模块

二、输入输出端的选择 三、参数的设置 四、基于LPM_COUNTER的数控分频器设计 进制的设置R=1111-d[3..0]+1 五、基于LPM_ROM的4位乘法器设计 乘法表的编辑

设计一个4位计数器

引脚配置窗口

选择引脚 锁定选项

输入信号名

输入对应 的引脚编号

引脚属性

按“Add”键

再次编译

步骤10:编程下载

(1) 调出编程器窗口

菜单MAX+plus II — Programmer

编程窗口

选择Programmer, 调出编程器

(2) 下载方式设定

菜单Options项 — Hardware Setup

3、开放式界面

可以与其他工业标准的设计输入、综合、仿真工具相连接

提供与多种第3方EDA工具的接口,包括:Cadence 3.1, Mentor Graphics C.2, Synopsys FPGA Compiler 3.5 …

4、丰富的设计库 5、MegaCore功能

为实现复杂的系统级功能提供HDL网表文件 — IP核

点击 New 点击 New按纽

符号编辑输入方法, 生成 . sym文件 文本编辑器, 硬件描述语言输入方法, 生成 . vhd 文件 波形图编辑器, 波形图输入方法, 生成 . scf 文件

(2)打开“Enter Symbol”对话框, 调入元件 方法:菜单命令,鼠标右键,双击鼠标左键

菜单命令: Symbol — Enter Symbol

全称:Multiple Array Matrix and Programmable Logic User System II “多阵列矩阵及可编程逻辑用户系统II”

第一代:A + plus,第二代:MAX + plus,第三代:MAX + plus II

MAX+plus II的特点

1、可在多种平台运行

存 盘 编 译 当 前 设 计 项 目 文 件

存 盘 仿 真 当 前 设 计 项 目 文 件

(3)设计文件编辑操作按钮

查 找 字 符

查 找 字 符 并 替 换

查 找 节 点

查 找 元 件 符 号

字 体 选 择

字 体 大 小 选 择

打 开 VHDL 模 板

增 加 缩 进 量

减 小 缩 进 量

(4)绘图操作按钮

进行连接

步骤3:将设计的原理图文件保存至该工程所在的文件夹

首先点击这里 文件名取为: h_adder.gdf

要存在自己建 立的文件夹中

步骤4:将设计项目设置成工程文件(PROJECT)

菜单File项 -> Project -> Set Project to Current File

最后注意此路 径指向的改变

菜单File项 -> Project -> Create Default Symbol

由半加器模块构成的全加器电路原理图

来自低位 的进位信号

向高位 的进位信号

和

步骤9:引脚锁定并重新编译

将设计文件中的输入、输出端口映射到所选器件相应引 脚的过程称为引脚锁定。 菜单Assign项 -> Pin/Location/Chip

波形编辑器, 波形输入文件

4、层次设计输入

支持一个设计方案中含有多个层次的设计,每个层次的 设计文件都可以是以不同方式建立的输入文件。

步骤1:为本工程创建一个文件夹

文件夹名不能用中文, 且不可带空格。

文件夹名取为 My_prjct

半加器电路的设计 (原理图输入方法)

真值表:

S:和项 C:进位项

调出时序分析器

输入输出 时间延迟

包装元件入库

选择菜单“File”→“Open”,在“Open”对话框 中选择原理图编辑文件选项“Graphic Editor Files”,然后选择h_adder.gdf,重新打开半加 器设计文件,然后选择“File”菜单的“Create Default Symbol”项,将当前文件变成了一个包 装好的单一元件(Symbol),并被放置在工程路径 指定的目录中以备后用。

MAXplusII中的设计流程

仿真 PLD器件及下 载配置 流程主体

MAXplusII中的设计流程

3. 原理图输入设计方法

设计输入方法

1、原理图输入

图形编辑器,四个库(含有丰富的单元器件)

2、硬件描述语言设计输入

文本编辑器,接受VHDL、Verilog HDL等设计文件

3、波形图设计输入

选择此项, 将当前的原理图 设计文件设置成工程

步骤5:选择目标器件

菜单Assign项 — Device

选择 ACEX1K系列

消去这里的勾, 使所有速度级别的 器件都能显示出来

根据实验板上的 目标器件型号选 择,如选EP1K30

步骤6:对工程文件进行编译、综合和适配

菜单MAX+plus II 项— Compiler

菜单Node 项 -> Enter Nodes from SNF

从SNF文件中 添加输入输出端口

点击“LIST”

点击

(3) 设定仿真时间

菜单File 项 -> End Time

选择END TIME 设定仿真时间

设为60微秒

(4) 编辑输入信号波形

首先在Options菜单中消去网格对齐Snap to Grid的选择(消去对勾)

选择工具 文本编辑 画正交线 画直线 画弧线 画圆 放大按钮 缩小按钮 窗口尺寸适配 连接点断/通 打开拖动功能 关闭拖动功能

(5)绘制波形操作按钮

选择工具 文本编辑 波形赋值 放大波形 缩小波形 窗口尺寸适配 赋低电平 赋高电平 赋不定值X 赋高阻Z 赋相反值 时钟信号赋值 周期信号赋值 总线赋值 状态机赋值

消去这里的勾, 以便方便设置 输入电平

改变仿真区域 坐标到合适位置

点击‘1’,使拖黑 的电平为高电平

(6) 波形文件存盘

步骤8: 仿真测试和波形分析 (1)运行仿真器

菜单MAX+plusII项 -> Simulator

调出仿真器

运行仿真器

(2) 观察分析半加器仿真波形

(3) 为了精确测量半加器输入与输出波形间的延时量, 可打开时序分析器

逻辑表达式:

C=AB

A与 的异或非关系

目标原理图:

输入:a, b 输出:so, co

逻辑门:二输入与门(AND2), 异或非门(XNOR), 非门(NOT)

S = AB + AB = AB + AB

C = AB

步骤2:输入设计项目并且存盘

(1)创建新的输入文件的方法:菜单命令,工具栏快捷按纽

原理图编辑器, 原理图输入方法, 生成 . gdf 文件

调出编译器

编译窗口

网表提取 模块

数据库 建库模块

逻辑综合 模块

逻辑分割 模块

逻辑适配 模块

时序仿真网 表生成模块

装配模块

将已通过逻辑综合的设计映射到所选器件中 用于对设计进行逻辑分割 用于建立描述整个设计的数据库 生成用于器件编程下载的各种文件 用于对设计进行逻辑综合和优化 生成用于时序仿真的各种文件 用于生成设计的网表文件

基于PC的系统:Windows 98 /NT 4.0/2000 /XP 工作站:Sun SPARCstations, HP 9000 Series 700/800, IBM RISC System/6000

2、完全集成化

各功能子模块:设计输入、编辑、综合、仿真完全集成于 可编程逻辑开发工具内

EDA软件系统的构成 (EDA工具的子模块)

1、设计输入编辑器

完成设计的输入、对设计进行编译

2、综合器

实现从高层抽象描述向低层次描述的自动转换

3、仿真器

实现各个层次的仿真验证,包括功能仿真和时序仿真

4、适配器(布局布线器)

完成设计系统在目标器件上的布局布线

5、下载器/编程器

把设计下载至对应的实际器件,实现硬件设计

在编程窗打开 的情况下选择 下载方式设置

选择此项

下载方式

(3) 下 载

下载/配置 成 功!

4. 参数可设置LPM宏功能块应用

LPM : Library of Parameterized Modules, 参数可设置模块库

一、LPM功能块的调用 步骤:

1、启动MAX+plusII,并选择图形输入方式

(2)项目处理操作按钮

新 建 设 计 文 件

打 开 平 面 布 置 编 辑 器

打 开 编 译 器

打 开 仿 真 器

打 开 定 时 分 析 器

打 开 编 程 器

指 定 设 计 项 目 文 件 名

指 定 当 前 文 件 为 设 计 项 目 文 件

打 开 设 计 项 目 顶 层 文 件

存 盘 并 检 查

FGPA : . SOF文件 CPLD : . POF文件

菜单Processing 项— Fitter Settings :