实验六-JK触发器的VHDL设计

VHDL实验报告JK触发器、同步计数器

Verilog HDL实验报告Verilog 实验报告题目:JK触发器、同步计数器系部名称:通信工程专业名称:通信工程班级:班内序号:学生姓名:时间:2010.11.28一、实验内容:用JK触发器构成同步计数器:设计一个同步计数器,其逻辑图和JK触发器的逻辑图所示。

清零信号clear低电平有效,输入数据在时钟信号clock的上升沿被锁存,触发器在clock的下降沿输出,当count_enable信号为低电平时停止计数。

写出同步计数器的verilog描述和激励模块,在激励模块中使用clear和count_enable对计数器进行测试,并显示输出计数Q[3:0]。

二、实验原理图:JK触发器构成同步计数器源代码://主模块module synchronous_counter(clear,clock,count_enable,Q);input clear,clock,count_enable;output [3:0] Q;wire qbar1,qbar2,qbar3,qbar0;wire a,b,c;assign a = Q[0] & count_enable;assign b = a & Q[1];assign c = b & Q[2];JK_flip_flop myJK(count_enable,count_enable,clock,clear,Q[0],qbar0);JK_flip_flop myJK1(a,a,clock,clear,Q[1],qbar1);JK_flip_flop myJK2(b,b,clock,clear,Q[2],qbar2);JK_flip_flop myJK3(c,c,clock,clear,Q[3],qbar3);endmodule//调用的JK触发器模块module JK_flip_flop(j,k,clock,clear,q,qbar);input j,k,clock,clear;output q,qbar;wire a,b,y,ybar,c,cbar,d,q,qbar;assign a = ~ (((qbar & j)& clock) & clear);assign b = ~ ((clock & k) & q);assign y = ~ (a & ybar);assign ybar = ~ ((y & clear) & b);assign c = ~(y & cbar);assign cbar = ~ clock;assign d = ~ (cbar & ybar);assign q = ~ (c & qbar);assign qbar = ~ ((q & clear) & d);endmodule测试文件源代码:module count_test;reg count_enable=1,clock=0,clear=0;wire [3:0]Q;synchronous_counter myCount(clear,clock,count_enable,Q);initial #10 clear=1;always@(negedge clock)begin$monitor($time," clear=%b,count_enable=%b,Q=%b%b%b%b\n",clear,count_enable,Q[3],Q[2],Q[1],Q[0]);endalways clock = #5 ~clock;always count_enable= #170 ~count_enable; endmodule实验结果:波形图:三、实验心得:这次实验比上一次顺利多了,可能是因为有了前一次的铺垫,我对软件的熟悉度有了一定的提高。

数字逻辑实验报告:触发器及其作用

数字逻辑实验报告:触发器及其作用一、实验目的1. 学习触发器的基本概念、类型及其工作原理;2. 掌握触发器的电路实现方法;3. 掌握使用触发器进行时序逻辑设计的方法。

二、实验原理触发器(Flip-flop)是数字逻辑电路中最基本的存储元件。

它可以在电路中实现数据的存储、时序的生成、状态的转移等功能。

触发器从功能上分为两大类:时序逻辑触发器和状态逻辑触发器。

时序逻辑触发器是指根据输入信号的时序变化来激发触发器输出端口状态变化的触发器,常见的有SR触发器、D触发器和JK触发器等。

状态逻辑触发器是指触发器的输出值与输入值中的某些形式的关系有关,常见的有T触发器和R-S触发器等。

此实验主要介绍SR触发器、D触发器、JK触发器的实现及其作用。

1. SR触发器SR触发器也称为RS触发器,它的英文全称是Set-Reset Flip-flop。

SR触发器的输入有两个:S、R。

当S=1,R=0时,Q输出为1;当S=0,R=1时,Q输出为0;当S=R=1时,Q的状态就不确定了。

具有这个不确定状态的原因是因为在SR触发器中,S和R是可以同时为1的,这种情况会导致电路出现失效或过度充电的问题,故SR触发器不常用。

2. D触发器D触发器是指数据存储触发器,它有一个数据输入信号D,其输出信号Q与输入信号D同步,并且保持输出信号状态不变。

当时钟信号CK上升时,D触发器将数据D储存在内部存储器中,当时钟信号CK下降时,存储器中的数据被保持不变。

D触发器还具有一个反相输出信号Q',它与输出信号Q恰好相反。

3. JK触发器JK触发器是指一种利用J和K两个输入信号来控制输出状态的电路。

当J=K=0时,JK触发器不动;当J=1,K=0时,JK触发器转换到置“1”状态;当J=0,K=1时,JK触发器转换到复位“0”状态;当J=K=1时,JK触发器的状态与上一状态相反。

这里需要注意的是,当J=K=1时,JK触发器可以作为一个数字计数器或频率分带器使用。

vhdl课程设计实验报告

湖南科技大学信息与电气工程学院《课程设计报告》题目:电子技术课程设计报告专业:通信工程班级:一班姓名:何家乐学号: 1004040126指导教师:罗朝辉任务书题目《电子技术》课程设计时间安排课程设计时间为10天(2周)。

(1)调研、查资料1天。

(2)总体方案设计2 天。

(3)电路设计2天(画原理图,参数计算)。

(4)实验室完成相应电路的验证。

3天(5)撰写设计说明书 1 天。

(6)验收1 天。

目的:训练学生综合运用学过的电子技术原理的基础知识,独立进行查找资料、选择方案、设计电路、撰写报告,进一步加深对电子电路基本理论的理解,提高运用基本技能的能力,为今后的学习和工作打下坚实的基础。

要求:(1)能正确设计电路,画出线路图,分析电路原理。

(2)按时参加课程设计指导,定期汇报课程设计进展情况。

(3)广泛收集相关技术资料。

(4)独立思考,刻苦钻研,严禁抄袭。

(5)按时完成课程设计任务,认真、正确地书写课程设计报告。

(6)培养实事求是、严谨的工作态度和认真的工作作风。

总体方案实现:(1)明确设计任务,对所要设计的任务进行具体分析,充分了解电路性能、指标内容及要求。

(2)制定设计方案。

(3)迸行具体设计:单元电路的设计;参数计算;器件选择;绘制电路原理图。

(4)撰写课程设计报告(说明书):课程设计报告是对设计全过程的系统总结,也是培养综合科研素质的一个重要环节。

指导教师评语:评分等级:()指导教师签名:课程设计报告1.课题名称:RGB LED Control 原理图及PCB设计2.设计任务及要求⑴任务:完成RGB LED control 的设计,并画出原理图及其PCB设计。

⑵要求:①能正确设计电路,画出线路图,分析电路原理。

②按时参加课程设计指导,定期汇报课程设计进展情况。

③广泛收集相关技术资料。

④独立思考,刻苦钻研,严禁抄袭。

⑤按时完成课程设计任务,认真、正确地书写课程设计报告。

⑥培养实事求是、严谨的工作态度和认真的工作作风。

数字逻辑JK触发器实验报告 (2)

数字逻辑JK触发器实验报告 (2)

实验器材:

1.数字逻辑教学实验箱

2.数字电路预制实验板

3.数字逻辑集成电路:74F74

4.数字万用表

5.接线器

实验原理:

JK触发器是一种常用的触发器,由于它具有输入端J、K可以控制输出端Q翻转的特点,所以被广泛应用于各种计数器、定时器、频率除法器、数据选择器等数字电路中。

在JK触发器中,J\和K\ 可以用来控制状态转换,当J\和K\ 都为0时,JK触发器保持原状态不变;当J\和K\ 都为1时,JK触发器将翻转输出;当J\为1,K\为0时,JK触发器将输出1;当J\为0,K\为1时,JK触发器将输出0。

JK触发器的实现可用SR触发器,D触发器,

T触发器等电路实现,其中最常用的是基于SR触发器实现的JK触发器。

实验步骤:

2.将JK触发器74F74插入数字电路预制实验板中,并拨动开关至合适位置。

3.使用数字万用表测量所需测试点的电压。

4.使用接线器进行接线。

6.通过手动触发或者按键操作时序控制,测试各测试点的逻辑电平,并记录数据。

实验结果:

通过实验可得出以下结论:

1.当J、K均为0时,JK触发器保持原状态不变。

黄红涛-vhdl实验报告-实验3 触发器

学生实验报告实验课名称:VHDL硬件描述语言实验项目名称:触发器专业名称:电子科学与技术班级:32050801学号:3205080134学生姓名:黄红涛教师姓名:程鸿亮_2010__年__11__月__6__日组别_____________________ 同组同学_ 刘增辉实验日期:2011 年11 月6 日实验室名称______ 成绩_____一、实验名称:触发器二、实验目的与要求:设计RS、JK、D、T四种触发器,掌握异步复位置位的方法以及四种触发功能的实现方法,掌握QuartusII软件的使用方法以及GW48型SOPC开发平台中的输入输出模式配置方法。

通过VHDL编程,实现RS、JK、D、T四种触发器,要求四种触发器同时在开发平台上实现,并共享置位、复位端,JK、D、T三种触发器共享时钟信号端,具体接口如下所示:s:所有触发器的置位输入端,低电平有效;r:所有触发器的复位输入端,低电平有效;j:JK触发器可j控制输入端;k:JK触发器的k控制输入端;cp:时钟信号;d:D触发器数据输入端;t:T触发器控制端。

q_rs、qn_rs:RS触发器状态输出端;q_jk、qn_jk:JK触发器状态输出端;q_d、qn_d:D触发器状态输出端;q_t、qn_t:T触发器状态输出端;err[3..0]:无效状态显示输出端。

首先在QuartusII上进行功能和时序仿真,之后通过器件及其端口配置下载程序到SOPC开发平台中。

在硬件实现中,要求:1.用拨动开关实现触发器的控制信号(r、s、t、j、k、d):注:要求使用最右面6个开关。

2.用实验平台的按键实现时钟信号(cp):3.用LED阵列实现状态输出的显示:注:要求用LED3、LED11分别显示RS触发器的q_rs和qn_rs;用LED4、LED12分别显示T触发器的q_t和qn_t;用LED5、LED13分别显示JK触发器的q_jk和qn_jk;用LED6、LED14分别显示D触发器的q_d和qn_d;用LED1、LED9、LED8、LED16同时显示无效状态。

实验六JK触发器的VHDL设计

实验六JK触发器的VHDL设计实验六JK触发器的VHDL设计设计JK触发器,其中prn(置1端)、clrn(清零端)均为⾼电平有效,当prn(置1端)、clrn(清零端)均为低电平时,cp上升沿来临输出q、q_not根据J、K的值有不同的输出。

library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_arith.all;use ieee.std_logic_unsigned.all;entity chufa_JK isport(cp,j,k,prn,clrn:in std_logic;q,q_not: out std_logic);end chufa_JK;architecture arch of chufa_JK issignal qn:std_logic;beginprocess(cp,prn,clrn)beginif clrn='1'and prn='0' then ----------异步(强制)置0qn<='0';elsif prn='1'and clrn='0'then ---------异步(强制)置1qn<='1';elsif cp'event and cp='1' then ---------cp上升沿qn<=(j and not qn) or(not k and qn);end if;end process;q<=qn;q_not<=not qn;end arch;1、波形仿真分析注意:此JK触发器设计中prn(置1端)、clrn(清零端)均为⾼电平有效,当prn(置1端)、clrn(清零端)均为低电平时,cp上升沿来临输出q、q_not根据J、K的值有不同的输出。

注意与课本JK触发器功能表的区分。

JK、D、T触发器(2024版)

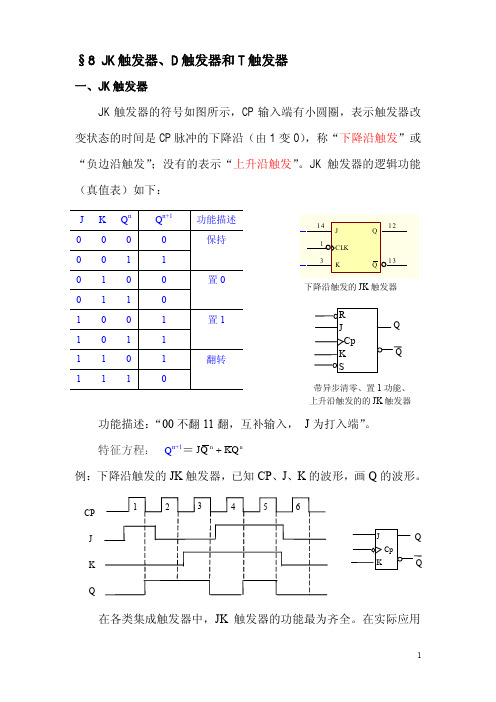

§8 JK 触发器、D 触发器和T 触发器一、JK 触发器JK 触发器的符号如图所示,CP 输入端有小圆圈,表示触发器改变状态的时间是CP 脉冲的下降沿(由1变0),称“下降沿触发”或“负边沿触发”;没有的表示“上升沿触发”。

JK 触发器的逻辑功能(真值表)如下:功能描述:“00不翻11翻,互补输入, J 为打入端”。

特征方程: Q n+1=n n Q K Q J例:下降沿触发的JK 触发器,已知CP 、J 、K 的波形,画Q 的波形。

在各类集成触发器中,JK 触发器的功能最为齐全。

在实际应用J K Q n Q n+1 功能描述 0 0 0 0 保持0 0 1 1 0 1 0 0 置0 0 1 1 0 1 0 0 1 置1 1 0 1 1 1 1 0 1 翻转 1 1 1CP J K Q123456J Cp KQ QRJ Cp K SQ Q带异步清零、置1功能、 上升沿触发的的JK 触发器CLK 1J 14K3Q13Q12T下降沿触发的JK 触发器中,它不仅有很强的通用性,而且能灵活地转换成其他类型的触发器。

二、D 触发器 1.电路组成:用JK 触发器能很方便地构成D 触发器:a )用JK 触发器构成D 触发器 b) D 触发器的逻辑符号2.逻辑功能: 1) 真值表:描述:每来一个CP 脉冲,就把D 端的数据送到Q 端。

因此D 触发器又称“数据锁存器”,D (Data )端是数据输入端。

2) 特征方程:Q n+1=D例题:下降沿触发的D 触发器,初态为0态。

根据图示的CP 和D 的波形,画Q 和Q 反的波形。

QQCP D Q Q三、T 触发器 1.电路组成把JK 触发器的两个输入端J 、K 连在一起,作为一个输入端T ,就构成T 触发器。

如下图:2.逻辑功能:因为T=J=K ,所以当T=0,CP 脉冲来后触发器维持原状太不变;当T=1,每来一个CP 脉冲触发器状态翻转一次。

特征方程:Q n+1=n n n QT Q T Q T ⊕=+ 例:根据T 触发器的CP 、T信号画Q 和Q 反:常用集成触发器介绍74LS74 (Dual D-type FF (pre, clr)) 74LS112(Dual JK FF(-edge, pre, clr))CP T Q Q51234Q Q74LS379 (Quad D-type FF w/en)CC4027(CD4027)(Dual JK FF (+edge, pre, clr))触发器应用举例(演示)1.触发器构成的数据锁存器2.触发器构成的移位寄存器 3 .触发器构成的计数器。

VHDL触发器

三、串入/并出移位寄存器(2) 四位串入/并出移位寄存器的逻辑电路图:

三、串入/并出移位寄存器(3) VHDL语言描述:

LIBRARY IEEE; USE IEEE.std_logic_1164.ALL; USE WORK.example.ALL; ENTITY shift_reg IS PORT (d1 : IN std_logic; cp : IN std_logic; q : OUT std_logic_vector(3 DOWNTO 0)); END shift_reg; ARCHITECTURE structure_arc OF shift_reg IS

二、串入/串出移位寄存器(1) 移位功能的定义:指寄存器里面存储的代码能 够在时钟的作用下进行依次左移或者是右移。 移位寄存器的定义:通常把具有存储和移位功 能的寄存器称为移位寄存器。 移位寄存器的分类:串入/串出移位寄存器、串 入/并出移位寄存器和循环移位寄存器等。

二、串入/串出移位寄存器(2) 串入/串出移位寄存器的定义: 所谓串入/串出移位寄存器是指它的第一 个触发器的输入端口用来接收外来的输入信号, 而其余的每一个触发器的输入端口均与前面一 个触发器的Q端相连。这样,移位寄存器输入 端口的数据将在时钟边沿的作用下逐级向后移 动,然后从输出端口串行输出。例如前面第六 章中介绍过的串入/串出四位移位寄存器。

同步复位的D触发器(1) 电路符号和功能表:

同步复位的D触发器(2) VHDL语言描述:

ARCHITECTURE rtl_arc OF sync_rdff IS BEGIN PROCESS (clk) BEGIN IF (clk’event AND clk =’1’) THEN IF (reset =’0’) THEN q <= ’0’; qb <= ’1’; ELSE q <= d; qb <= NOT d; END IF; END IF; END PROCESS; END rtl_arc;

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

实验六JK触发器的VHDL设计

设计JK触发器,其中prn(置1端)、clrn(清零端)均为高电平有效,当prn(置1端)、clrn(清零端)均为低电平时,cp上升沿来临输出q、q_not 根据J、K的值有不同的输出。

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

use ieee.std_logic_unsigned.all;

entity chufa_JK is

port

(

cp,j,k,prn,clrn:in std_logic; q,q_not: out std_logic

);

end chufa_JK;

architecture arch of chufa_JK is

signal qn:std_logic;

begin

process(cp,prn,clrn)

begin

if clrn='1'and prn='0' then

----------异步(强制)置0

qn<='0';

elsif prn='1'and clrn='0'then

---------异步(强制)置1

qn<='1';

elsif cp'event and cp='1' then ---------cp上升沿

qn<=(j and not qn) or(not k and qn);

end if;

end process;

q<=qn;

q_not<=not qn;

end arch;

1、波形仿真分析

prn(置1端)

clrn

(清零

端)

cp J K Q Q_not

01x x x01

10x x x10

00上升

沿

00保持保持

00上升

沿

0101

00上升

沿

1010

00上升

沿

11翻转翻转

注意:此JK触发器设计中prn(置1端)、clrn(清零端)均为高电平有效,当prn(置1端)、clrn(清零端)均为低电平时,cp上升沿来临输出q、q_not

根据J、K的值有不同的输出。

注意与课本JK触发器功能表的区分。

2、延时仿真分析

输出信号(q、q_not)较cp上升沿延时约10.9ns

实验六报告格式要求:

实验名: JK触发器的VHDL设计

一、实验目的:

JK触发器的VHDL设计

二、实验要求

Max+Plus II开发环境

三、源程序代码

JK触发器的VHDL设计:

……………

…………….

…………………

四、波形仿真

(1)波形仿真图

(2)波形仿真分析

五、延时仿真

(1)延时仿真图

(2)延时仿真分析

六、实验总结。