清华大学数字集成电路作业一

清华大学数字集成电路作业四

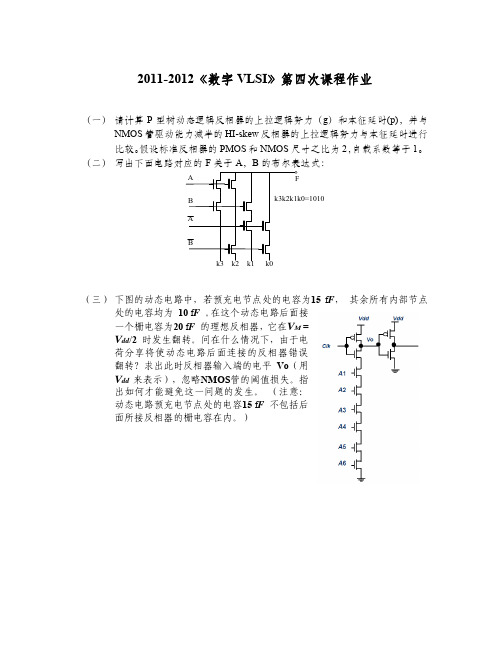

2011-2012《数字VLSI 》第四次课程作业

(一) 请计算P 型树动态逻辑反相器的上拉逻辑努力(g )和本征延时(p),并与

NMOS 管驱动能力减半的HI-skew 反相器的上拉逻辑努力与本征延时进行比较。

假设标准反相器的PMOS 和NMOS 尺寸之比为2,自载系数等于1。

(二) 写出下面电路对应的F 关于A ,B 的布尔表达式:

(三) 下图的动态电路中,若预充电节点处的电容为15 f F , 其余所有内部节点

处的电容均为 10 f F 。

在这个动态电路后面接

一个栅电容为20 f F 的理想反相器,它在V M =

V dd /2 时发生翻转。

问在什么情况下,由于电

荷分享将使动态电路后面连接的反相器错误

翻转?求出此时反相器输入端的电平 Vo (用

V dd 来表示),忽略NMOS 管的阈值损失。

指

出如何才能避免这一问题的发生。

(注意:

动态电路预充电节点处的电容15 f F 不包括后

面所接反相器的栅电容在内。

)。

数字集成电路习题答案

W / L 1 根据VGS和VDS确定其处于线性、饱和还是截止状态,并求 I D

的值。

解: (1)nm os:

VGT VGS VT 0 2.5 0.43 2.07 VDS

nm os 处于饱和区 ,Vmin VGT 2.07

2 W V ' I D kn ( )(VGT Vmin min )(1 VDS ) L 2 2 2 . 07 115 (2.072 )(1 0.06 2.5) 2 283.3A

VT0(V)

NMOS PMOS 0.43 -0.4

(V0.5)

0.4 -0.4

VDSAT(V)

0.63 -1

k’(A/V2)

115×10-6 -30×10-6

(V-1)

0.06 -0.1

1.假设设计一个通用0.25m CMOS工艺的反相器,其中PMOS晶体管的 最小尺寸为(W=0.75m,L=0.25m,即W/L=0.75/0.25) , NMOS晶体管 的最小尺寸为(W=0.375m,L=0.25m,即W/L=0.375/0.25) 求出g,VIL,VIH,NML,NMH

( R1 R2 R5 )C5

DCLK 3 R1C1 R1C2 ( R1 R3 )C3 R1C4 R1C5

(b)

DCLK 1 R1C1 ( R1 R2 )C2 R1C3 ( R1 R2 R4 )C4 ( R1 R2 )C5

9 RC

DCLK 2 R1C1 ( R1 R2 )C2 R1C3 ( R1 R2 )C4

( R1 R2 R5 )C5 9 RC

DCLK 3 R1C1 R1C2 ( R1 R3 )C3 R1C4 R1C5

清华大学数字电路汇总题库

清华大学数字电路题库一、填空题 : (每空1分,共10分)1. (30.25) 10 = ( ) 2 = ( ) 16 。

2 . 逻辑函数L = + A+ B+ C +D = 。

3 . 三态门输出的三种状态分别为:、和。

4 . 主从型JK触发器的特性方程= 。

5 . 用4个触发器可以存储位二进制数。

6 . 存储容量为4K×8位的RAM存储器,其地址线为条、数据线为条。

二、选择题: (选择一个正确的答案填入括号内,每题3分,共30分 )1.设下图中所有触发器的初始状态皆为0,找出图中触发器在时钟信号作用下,输出电压波形恒为0的是:()图。

2.下列几种TTL电路中,输出端可实现线与功能的电路是()。

A、或非门B、与非门C、异或门D、OC门3.对CMOS与非门电路,其多余输入端正确的处理方法是()。

A、通过大电阻接地(>1.5KΩ)B、悬空C、通过小电阻接地(<1KΩ)B、 D、通过电阻接V CC4.图2所示电路为由555定时器构成的()。

A、施密特触发器B、多谐振荡器C、单稳态触发器D、T触发器5.请判断以下哪个电路不是时序逻辑电路()。

A、计数器B、寄存器C、译码器D、触发器6.下列几种A/D转换器中,转换速度最快的是()。

A、并行A/D转换器B、计数型A/D转换器C、逐次渐进型A/D转换器B、 D、双积分A/D转换器7.某电路的输入波形 u I 和输出波形 u O 如下图所示,则该电路为()。

A、施密特触发器B、反相器C、单稳态触发器D、JK触发器8.要将方波脉冲的周期扩展10倍,可采用()。

A、10级施密特触发器B、10位二进制计数器C、十进制计数器B、D、10位D/A转换器9、已知逻辑函数与其相等的函数为()。

A、 B、 C、 D、10、一个数据选择器的地址输入端有3个时,最多可以有()个数据信号输出。

A、4B、6C、8D、16三、逻辑函数化简(每题5分,共10分)1、用代数法化简为最简与或式Y= A +2、用卡诺图法化简为最简或与式Y= + C +A D,约束条件:A C + A CD+AB=0四、分析下列电路。

试题标准答案模版A4-数字集成电路设计A答案[1]

![试题标准答案模版A4-数字集成电路设计A答案[1]](https://img.taocdn.com/s3/m/b1c5702d0b1c59eef9c7b432.png)

3考虑图3,

a.下面的CMOS晶体管网络实现什么逻辑功能?反相器的NMOS W/L=4,

PMOS W/L=8时输出电阻相同,根据这个确定该网络中各个器件尺寸。

b.最初的输入模式是什么,必须采用哪一种输入才能取得最大传输延时?

考虑在内部节点中的电容的影响。(给出分析过程)

图3

b. 放电——>充电;为了使延时最小,放电过程要求所有的内部电容全部放电,因此ABCDE=10101;充电过程要求所有的内部电容充电,因此ABCDE=10100;

5简述静态CMOS电路的优缺点。

答:静态CMOS电路在电源的两条轨线之间电压的摆幅,即VOH=VDD,VOL=GND。由于上拉和下拉网络是互斥网络,因此电路没有静态功耗。但存在有两个主要问题:一是有N个输入的门uyao晶体管数目为2N个,大大增加了它的实现面积;二是静态CMOS门的传播延时随扇入数的增加而迅速增加。

解:1)

2.将每道大题得分和总分填入得分栏中。

R=30kΩ,

假设晶体管处于线性区。

证明该晶体管处于线性区。

四、设计题(共30分,每题10分)

1.使用互补CMOS电路实现逻辑表达式 ,当反相器的NMOS W/L=2, PMOS W/L=4时输出电阻相同,根据这个确定该网络中各个器件尺寸。

三、计算题(共25分,第一题10分,第二题15分)

1.已知集成电路中Al1层参数如下:单位长度电容120aF/um;单位长度电阻0.065Ω/um。计算在该层长为12cm的导线传播延时。为减小此导线的传播延时将此导线3等分并插入2个传播延时为80ps的反相器,计算在这种情况下各层上整个导线的传播延时。

共页第页

说明:1。标准答案务必要正确无误。

络为对偶网络。

清华大学微电子专业_数字大规模集成电路_第六次作业

《数字VLSI 》第6次作业(一)如右图所示4×4的ROM 单元阵列,请问:1、当WL [0:3]为何值时表示WL [1]被选中?2、阵列中所存储的数据是多少?3、请列举该种存储结构的缺点。

(二)使用OR ROM 阵列构造8×2查找表,实现一个全加器的功能。

只需要画出OR ROM 的核心存储电路(类似上题图),并说明其工作原理。

(三)设计一个容量为2048×8 bit 的嵌入式SRAM ,1、如果物理布局上希望把该SRAM 设计成正方形,那么行、列译码器的输入分别为多少位?2、使用面积为1.3um×1.3um 的单比特SRAM 存储电路单位实现该SRAM ,并假设所需外围电路面积是SRAM 核心存储电路面积的10%,那么该SRAM 阵列的总面积是多少?(四)两级Buffer 用于驱动1cm 长的金属线,如下图所示。

第一个反相器是最小尺寸反相器,其输入电容为Ci =10fF ,本征传播延时(不带外部负载)为tp0=175ps ,工艺参数γ=1。

金属线宽度为3.6um ,金属方块电阻为0.08Ω/□,电容值为0.03fF/um 2,边缘场电容为0.04fF/um 。

1、求金属线的本征传播延时tw 。

2、求使得路径传输延时达到最小的第二级反相器尺寸,以及该电路的最小传播延时。

(五)关于数字芯片设计,1、Pad 的作用是什么?什么叫“Pad limited ”?2、现在很多数字芯片设计都是“Pad limited ”或“IO limited ”。

造成这种现象的深层次原因是什么?3、很多数字芯片都带有多个VDD 和GND 的Pad,为什么? C i V inV out。

数字集成系统第一次作业

Assignment1郭星宇2015E8000961083高能物理研究所电子学院9312班1.Give a formal or descriptive definition for each of the following terms.●ITRS:International technology Roadmap for Semiconductor国际半导体技术规划。

●System-level synthesis:系统级综合。

将自然语言(如英语)转化成算法表示的过程。

●Gate-Equivalent:等效门,用于衡量数字电路的复杂程度的基本单位,基于为完成一个电路功能而互独立的逻辑门数量。

●Logic synthesis:逻辑级综合。

从数据流表示转换到结构逻辑表示。

●Technology Nodes:技术结点。

用于描述半导体器件的尺寸,单位为纳米。

●Layout synthesis:版图综合。

指从逻辑门表示转换到版图表示。

●Feature size:特征尺寸。

COMS中表示工艺尺寸的参数,等于晶体管长度的一半。

●Partial design tree:设计树,包括自顶向下设计和自底向上设计两个概念。

●IC design complexity sources:集成电路设计复杂性的来源。

●Design window:设计窗口,它是指设计树中设计者所使用的层次的范围。

●Behavioral representation:行为描述。

通过定义的输入输出响应来描述的方式。

●Digital design space:数字设计空间,包括cost、speed、power dissipation。

●Abstraction hierarchy:A set of interrelation representation levels that allow a system to be represented in varying amounts of detail。

电子技术相关 《数字集成电路基础》作业答案

《数字集成电路基础》作业答案第一次作业1、查询典型的TTL与CMOS系列标准电路各自的VIH、VIL、VOH和VOL,注明资料出处。

2、简述摩尔定律的内涵,如何引领国际半导体工艺的发展。

第二次作业1、说明CMOS电路的Latch Up效应;请画出示意图并简要说明其产生原因;并简述消除“Latch-up”效应的方法。

答:在单阱工艺的MOS器件中(P阱为例),由于NMOS管源与衬底组成PN结,而PMOS 管的源与衬底也构成一个PN结,两个PN结串联组成PNPN结构,即两个寄生三极管(NPN 和PNP),一旦有因素使得寄生三极管有一个微弱导通,两者的正反馈使得电流积聚增加,产生自锁现象。

影响:产生自锁后,如果电源能提供足够大的电流,则由于电流过大,电路将被烧毁。

消除“Latch-up”效应的方法:版图设计时:为减小寄生电阻Rs和Rw,版图设计时采用双阱工艺、多增加电源和地接触孔数目,加粗电源线和地线,对接触进行合理规划布局,减小有害的电位梯度;工艺设计时:降低寄生三极管的电流放大倍数:以N阱CMOS为例,为降低两晶体管的放大倍数,有效提高抗自锁的能力,注意扩散浓度的控制。

为减小寄生PNP管的寄生电阻Rs,可在高浓度硅上外延低浓度硅作为衬底,抑制自锁效应。

工艺上采用深阱扩散增加基区宽度可以有效降低寄生NPN管的放大倍数;具体应用时:使用时尽量避免各种串扰的引入,注意输出电流不易过大。

2、什么是器件的亚阈值特性,对器件有什么影响?答:器件的亚阈值特性是指在分析MOSFET时,当Vgs<Vth时MOS器件仍然有一个弱的反型层存在,漏源电流Id并非是无限小,而是与Vgs呈现指数关系,这种效应称作亚阈值效应。

影响:亚阈值导电会导致较大的功率损耗,在大型电路中,如内存中,其信息能量损耗可能使存储信息改变,使电路不能正常工作。

3、什么叫做亚阈值导电效应?并简单画出logI D-V GS特性曲线。

答:GS在分析MOSFET时,我们一直假设:当V GS下降到低于V TH时器件会突然关断。

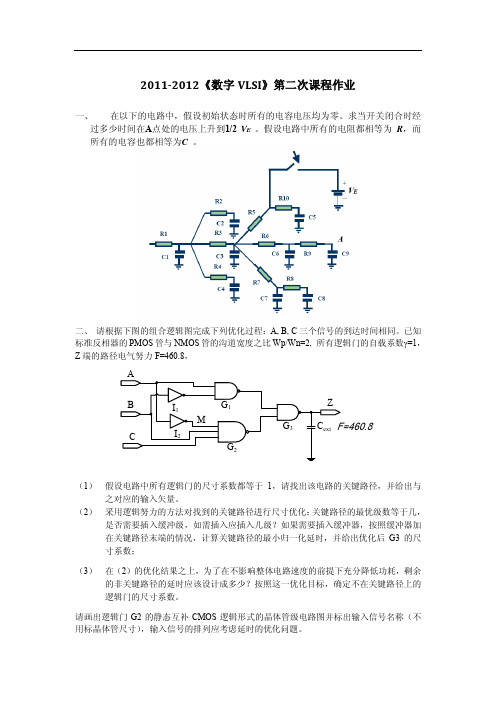

清华大学数字集成电路作业二

2011-2012《数字VLSI》第二次课程作业

一、在以下的电路中,假设初始状态时所有的电容电压均为零。

求当开关闭合时经

过多少时间在A点处的电压上升到1/2 V E 。

假设电路中所有的电阻都相等为R,而所有的电容也都相等为C 。

二、请根据下图的组合逻辑图完成下列优化过程:A, B, C三个信号的到达时间相同。

已知标准反相器的PMOS管与NMOS管的沟道宽度之比Wp/Wn=2, 所有逻辑门的自载系数 =1,

Z端的路径电气努力F=460.8,

(1)假设电路中所有逻辑门的尺寸系数都等于1,请找出该电路的关键路径,并给出与之对应的输入矢量。

(2)采用逻辑努力的方法对找到的关键路径进行尺寸优化:关键路径的最优级数等于几,

是否需要插入缓冲级,如需插入应插入几级?如果需要插入缓冲器,按照缓冲器加

在关键路径末端的情况,计算关键路径的最小归一化延时,并给出优化后G3的尺

寸系数;

(3)在(2)的优化结果之上,为了在不影响整体电路速度的前提下充分降低功耗,剩余

的非关键路径的延时应该设计成多少?按照这一优化目标,确定不在关键路径上的

逻辑门的尺寸系数。

请画出逻辑门G2的静态互补CMOS逻辑形式的晶体管级电路图并标出输入信号名称(不

用标晶体管尺寸),输入信号的排列应考虑延时的优化问题。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

2011-2012《数字VLSI》第一次课程作业

(一) 考虑图一的静态互补CMOS逻辑门, 写出它的布尔表达式,并画出下拉网络的结构。

(二)图二中假设所有NMOS器件的衬底均接地,电源电压为2.5V。

设输入 IN 的摆幅为 0V 至 2.5V,NMOS管的V T0 = 0.54V,|ΦF|=0.32V。

考虑静态情形,并忽略寄生电容。

(1)设衬偏系数γ=0,晶体管M2工作在什么模式(线性?饱和?截止?) (2)设衬偏系数γ=0,当IN = 0V 时,OUT = ?

(3)设衬偏系数γ=0.5,求节点X 处的电压。

(三) 如图三所示电路,已知M1的V T0=0.43V,V DSAT=0.63V,k’=115×10‐6A/V2,沟道尺寸如图所示,单位沟道长度的覆盖电容Cgso=Cgdo=0.31fF/μm,单位面积的氧化层电容Cox=6 fF/μm2。

请计算(忽略体效应和沟道长度调制效应):

(1) 当Vin = 2.5 V时Vout 的稳态电压(记为VOL)是多少?M1管处在什么工作区? (2) 如果Vin从0V上升到 2.5 V,而Vout的初始电压等于2.5V,那么从In端变化开始到Vout达到稳态这个过程中由In端注入的总净电荷量等于多少?

图 一

图 二

图 三。