ch2_1 单片机芯片的硬件结构(part 1 80C51)

80C51单片机的硬件结构

(2)电源线

1.封装:80C51系列单片机常用的两种封装为 双列直插式DIP40,方形封装LCC44

2020/9/25

2.80C51系列单片机外部引脚

2020/9/25

3.80C51单片机逻辑符号

2020/9/25

4.80C51系列单片机外部引脚说明

• 重要性:引脚表现出单片机的外部特性或硬 件特性,通过引脚连接和组建系统。

2020/9/25

2.2 80C51单片机内部结构

运算器

控 制 PC加1 器 寄存器

2020/9/25

2.控制器 (1) 程序计数器PC:存放下一条要执行的指令的地址, 16位程序地址寄存器 (2) 堆栈指针SP:“先进后出”原则存取数据的,开机 复位后,单片机栈底地址为07H (3) 指令寄存器IR : (4) 数据指针DPTR :可用于寻址程序存储器或数据存 储单元

微机控制技术

• 主讲: 张 勤 工学博士 副教授

教材:单片机基础,航空航天大学出版

2020/9/25

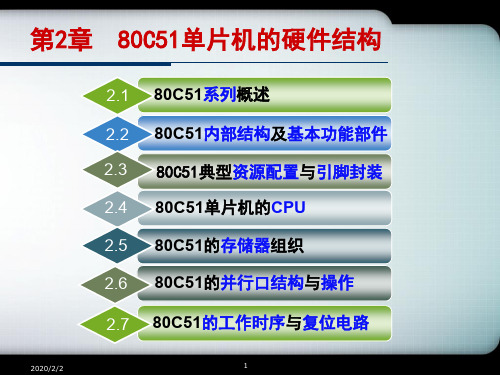

第2章 80C51单片机的硬件结构

• 2.1 单片机的概念及系列 • 2.2 80C51单片机内部结构 • 2.3 80C51系列单片机外引脚功能 • 2.4 80C51单片机的内部存储器 • 2.5 80C51单片机的并行I/O口 • 2.6 80C51单片机的时钟与定时 • 2.7 80C51单片机系统的复位

2020/9/25

80C51单片机逻辑符号

2020/9/25

端口线

• P3.7~P3.0:第一功能和其余三个端口的第一 功能相同。第二功能为控制功能。参阅P23, 表2.1

2020/9/25

P3口的第二功能:

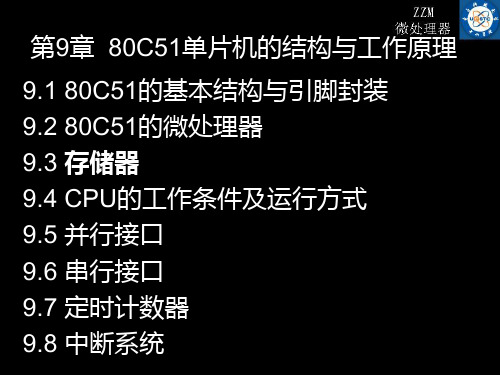

第9章 80C51单片机的结构与工作原理PPT课件

◆利用独立型仿真器开发

RS-232C 仿真器

仿真头 目标系统

15

◆利用非独立型仿真器开发

RS-232C 仿真器

仿真头 目标系统

16

单片机开发方式的发展

利用FLASH存储器,能够实现在系统编程 (ISP)和在应用编程(IAP)功能。首先 在PC机上完成应用程序的编辑、汇编(或 编译)、模拟运行,然后实现目标程序的 串行下载。运行验证。

17

四. 80C51的基本结构

MCS-51是Intel公司生产的一个单片机系 列名称。采取HMOS工艺或CHMOS工艺。 基本型: 8051/8751/8031(HMOS) 80C51/87C51/80C31/89C51(CHMOS) 增强型: 8052/8752/8032 80C52/87C52/80C32/89C52

3

哈佛体系结构计算机的存储结构

4

哈佛体系结构的计算机主要具有以下特点: 1、程序存储器与数据存储器在物理上是分开的。通过不 同的程序总线和数据总线(可以是多条)与CPU连接, 对程序指令的读取和对数据的存取可以同时进行,提高 了数据吞吐率。 2、控制器多采用硬布线技术实现,控制速度快,实时性 好。 3、该体系结构的处理器具有简单的指令集,其指令系统 多为RISC(精简指令集结构)结构体系。指令周期较短 且大多数指令执行周期相同,可实现流水线操作。 4、具有灵活的功能扩展特性。通过系统总线,可以对存 储器及功能模块进行扩展,以提高存储空间,改变系统 存储器类型或增加系统附加功能。

6

◆非80C51结构单片机新品不断推出, 给用户提供了更为广泛的选择空间 , 近年来推出的非80C51系列的主要产 品有:

﹡Intel的MCS-96系列16位单片机 ; ﹡Microchip的PIC系列RISC单片机 ; ﹡TI的MSP430F系列16位低功耗单片机 。

第2章80C51单片机的硬件结构.ppt

8

P2口结构

P2作通用I/O口(未扩片外存储器,或虽扩RAM但采用“MOVX @Ri”

传送时C=0)

P2作通用 I/O时为: 准双向口!

P2作地 址总线高 8位(C=1)

读锁存器 内部总线 写锁存器

地址

控制C

VCCCC R

D

Q

P2.X

锁存器 CL

1 1

0 MUX

T

P2.X 引脚

读引脚

2020/2/2

2020/2/2

6

P0作地址数据总线(当EA=1或“MOVX”类传送时C=1)

输出时,地 址/数据信息 分时出现在输

出引脚。

输入时,先 输出地址,然 后自动向锁存 器写1,再读 引脚。此时为 真正双向口。

读锁存器 内部总线 写锁存器 读引脚

地址/数据 1

控制C

VCC

& T1

D

Q

P0.X

锁存器

CL

Q

执行指令的操作码和操作数。 指令执行阶段,对指令操作码进行译码,以产生一系列控

制信号完成指令的执行。 晶振周期,S状态,机器周期和指令周期均是单片机时序

单位。机器周期常用做其他时间的基本单位。如晶振频率 为12MHZ,机器周期为1us,指令周期为1~4个机器周期, 即1~4us。

2020/2/2

2020/2/2

25

2.如果系统不能工作,也应查一查复位电路,有无复位信号,

如果RST持续为高电平,单片机就处于循环复位状态,PC 总为0,不会执行程序 。

如果复位电路有问题, PC不会置初始值0,而是其他随 机值,而该地址没有程序,或者是乱码,也不会正常执 行程序。因此,用户主程序必须从 0 地址开始存放。后 面我们将看到汇编语言程序的第1句是:

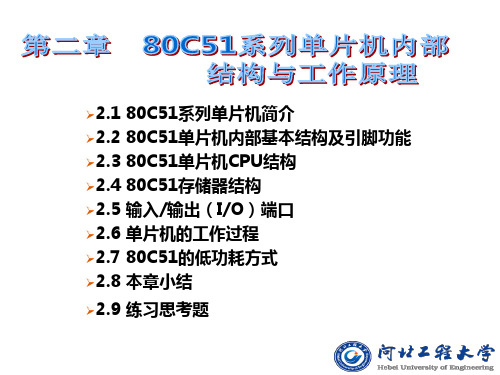

单片机 第二章 80C51系列单片机内部结构与工作原理

主要内容:介绍51系列单片机主要功能特点;然

后从硬件设计和程序设计的角度来分析单片机的基本 组成、工作原理;引脚功能和结构框图,并详细介绍 80C51的CPU及CPU外围电路结构和应用原理;存储器结 构和地址空间;位处理器;单片机的工作方式等。

要求: 1、掌握51系列单片机的主要功能特点; 2、熟悉51系列单片机的内部结构; 3、掌握各引脚功能;

2.2 80C51单片机内部基本结构及引脚功能

图2-1 80C51单片机内部结构

2.2 80C51单片机内部基本结构及引脚功能

1、CPU系统(核心)

组成:包括CPU、时钟系统、总线控制逻辑。

(1)CPU:是专门为面向测控对象、嵌入式应用特 点而设计的,有突出控制功能的指令系统。 (2)时钟系统:主要满足CPU及片内各单元电路对 时钟的要求,对80C51单片机还要满足功耗管理对时钟 系统电路的可控要求。 (3)总线控制逻辑:主要用于管理外部并行总线的 时序以及系统复位控制。

说明: 1、Intel公司将MCS-51系列单片机实行技术开放 政策后,许多公司,如Philips、Dallas、Siemens、 ATMEL、华邦、LG等都以MCS-51中的基础结构8051为

2.1 80C51系列单片机简介

基核推出了许多各具特色、各具优越性能的单片机。

2、该课件后面提到的80C51不是专指MaskROM供货 状态的型号,而是泛指80C51系列中的基础结构。 80C51系列则是在8051基础结构通过不同资源配置而推 出的一系列CHMOS单片机。

内部寄存器 ACC B PSW

初始状态 00H 00H 00H

内部寄存器 TCON TMOD TH0

初始状态 00H 00H 00H

SP

80C51单片机的内部结构

80C51单片机的内部结构广告单片机按存储结构可分为二类:一类是哈佛结构,另一类是普林斯顿结构。

①哈佛结构所谓哈佛结构是指程序存储器地址空间与数据存储器地址空间分开的单片机结构,如80C51单片机采用哈佛结构,所以80C51单片机的程序存储器地址空间与数据存储器地址空间是分开的,各有64K存储空间。

②普林斯顿结构所谓普林斯顿结构是指程序存储器地址空间与数据存储器地址空间合并的单片机结构,如MCS-96单片机采用普林斯顿结构,所以MCS-96单片机的程序存储器地址空间与数据存储器地址空间是合并的,共有64K存储空间。

1.单片机的CPU图1是80C51单片机的内部结构框图。

若除去图中的存储器电路和I/O部件,剩下的便是CPU。

它可以分为运算器和控制器两部分。

运算器功能部件包括算术逻辑运算单元ALU、累加器ACC、寄存器B、暂存寄存器TMP1、TMP2、程序状态字寄存器PSW等。

控制器功能部件包括程序计数器PC、指令寄存器IR、指令译码器ID、定时控制逻辑电路CU、数据指针寄存器DPTR、堆栈指针SP及时钟电路等。

(1)运算器①算术逻辑运算单元ALU(Arithmetic Logical Unit)ALU可以进行算术、逻辑运算。

算术运算有:加、减、乘、除,逻辑运算有:与、或、异或等。

②累加器ACC累加器ACC的主要功能是在运算前存放一个操作数,运算后存放一个操作结果。

80C51系列单片机虽然在结构上仍然以累加器A作为重要部件。

但由于内部电路采取了措施,使得累加器A在数据传送、逻辑操作等方面的核心作用有所削弱。

数据可以在片内直接/间接地址的存储器之间直接传送,而不必经过累加器A。

但,加、减、乘、除算术运算指令的运算结果都存放在累加器A或AB寄存器对中。

③暂存器TMP1、TMP2由图1可知,ALU进行算术逻辑运算前的两个操作数来自暂存器TMP1、TMP2,所以暂存器TMP1、TMP2用于存放运算前的两个操作数。

ch2_3 单片机芯片的硬件结构(part 1 80C51)

(1)单字节单周期指令(如 INC A) 只需进行一次读指令操作。当第二个ALE有效时,由于PC没有 加1,所以读出的还是原指令。 (2)双字节单周期指令(如 ADD A,#data) ALE的两次读操作都是有效的,第一次是读指令操作码,第二 次是读指令第二字节#data。 (3)单字节双周期指令(如 INC DPTR) 两个机器周期共进行四次读指令的操作,但其中后三次的读操 作全是无效的。 (4) 单字节双周期指令(如MOVX)

22μF C1 Vcc RST 80C51 R1 1KΩ Vcc

22μF C1

Vcc RST RST

80C51 R2 200Ω R1 1KΩ C 1 C2 22μF

80C51

R1 R2 1KΩ

(a)上电复位电路

(b)按键电平复位电路

(c)按键脉冲复位电路

图 几种复位电路

2.5.2 程序执行方式

程序执行方式是单片机的基本工作方式。由于复位后 PC=0000H,因此程序执行总是从0000H开始的。一般在 0000H开始的单元中存放一条无条件转移指令,以便跳转 到实际主程序的入口去执行。

ห้องสมุดไป่ตู้

2.访问外部RAM的时序

S1

S2

S3

S4

S5

S6

S1

S2

S3

S4

S5

S6

ALE

PSEN

RD

P2 PCH 输出

PCH 输出

DPH 输出或 P 2 输出 DPH输出/P2输出

PCH 输出

P0 PCL输出 指令输入 地址输出 数据输入 PCL输出 指令输入

图 访问外部RAM的时序

2.5 80C51单片机的工作方式

比如:

80C51单片机的基本结构是由中央处理器CPU

80C51单片机的基本结构是由中央处理器CPU、存储器、输入/输出接口电路(I/O口)、定时和中断电路组成。

80C51的组成:微处理器、存储器、外部输入/输出接口电路(I/O接口)、中断系统、时钟电路、系统总线、80C51的存储器内部数据存储器:实际上80C51芯片中共有256个RAM单元,但其中后128单元被专用寄存器占用,供用户使用的只是前128单元,用于存放可读写的数据。

内部程序存储器:内部程序存储器是指ROM(4KB×8)。

80C51共有4 KB掩膜ROM,用存放程序和原始数据。

因此称之为程序存储器,简称“内部ROM”。

I/O口电路:80C51单片机共有4个8位的I/0口(P0-P3),以实现数据的并行输入输出。

还有一个可编程全双工的串行口,它功能强大,可做异步通信收发器使用,也可用作同步移位器使用。

中断系统:80C51单片机的中断功能较强,以满足控制应用的需要。

80C51共有5个中断源。

即外部中断2个,定时/计数中断2个,串行中断1个。

全部中断分为高优先级和低优先级共两级。

时钟电路:80C51单片机的内部具有时钟电路,但石英晶体振荡器和微调电容需外接。

总线:上述这些部件都是通过总线连接起来,才能构成一个完整的单片机系统。

总线结构减少了单片机的连线和引脚,提高了集成度和可靠性。

主电源引脚Uss和Ucc :Vss(20脚):接地Vcc(40脚):正常操作、对EPROM编程和验证时为+5V电源。

外接晶振引脚XTALl和XTAL2 XTALl(19脚):内部振荡电路反相放大器的输入端,是外接晶体的一个引脚。

当使用外部时钟时,对于HMOS单片机,该引脚必须接地;对于CHMOS单片机,该引脚作为驱动端。

XTAL2(18脚):内部振荡电路反相放大器的输出端,是外接晶体的另一端。

若使用外部时钟时,对于HMOS单片机,该引脚输入外部时钟脉冲;对于CHMOS单片机,此引脚应悬浮。

控制和其它电源复用引脚RST/VPD(9脚):复位信号输入引脚/备用电源输入引脚。

单片机原理与接口技术 80C51 单片机的硬件结构

(2)控制器电路 控制器电路包括程序计数器PC、PC加1寄存器、指令

寄存器、指令译码器、数据指针DPTR、堆栈指针SP、 缓冲器以及定时与控制电路等。控制电路完成指挥控制 工作,协调单片机各部分正常工作。

2. 存储器 80C51单片机的存储器包括数据存储器和程序存储

任一时刻,cpu只能使用其中的一组寄存器,称为当 前工作寄存器组,由程序状态字寄存器PSW中的RS1, RS0位的组合来决定。没有选中的单元也可作为一般的 数寄据存缓器存:使用。系统上电复位时,默认选中第0组寄存器。 1、可用8位地址寻址; 2、在指令中既可用名称表示,也可以使用单元地址表示。

docin/sundae_meng

串行通信接口,可以同时发送和接收数据。

docin/sundae_meng

6. 中断控制系统

80C51共有5个中断源,即外中断2个,定时/计数中断2个, 串行中断1个。

7. 时钟电路

80C51芯片内部有时钟电路,但晶体振荡器和微调电容 必须外接。时钟电路为单片机产生时钟脉冲序列,振荡器的 频率范围为1.2MHz~33MHz,典型取值为6MHz。

器装备、飞机导航系统。 (6)计算机外部设备及电器方面:打印机、硬盘驱动器、

彩色与黑白复印机、磁带机等。 (7)多机分布式系统:可用单片机构成分布式测控系统,

它使单片机应用进入了一个全新的阶段。 (测控系统,智能仪表,智能玩具,计算机外设)

docin/sundae_meng

4.典型单片机产品简介 (1) MCS-51单片机系列

2、位寻址区 在工作寄存器后的16个数据单元(20H~2FH),它

们既可以作为一般的数据单元使用,又可以按位对每个单 元进行操作,因此这16个数据单元又称作位寻址区。位寻 址区共计128位,其位地址为00H~7FH。

单片机第2章80C51的结构与原理课件

通信。

并行通信接口的构成和使用

1

并行传输

2

接口标准

3

应用举例

同时发送和接收多个数据

定义了数据传输的电气和

并行通信接口常用于图形

位,适用于高速数据传输

逻辑特性,如PIO、DDR、

显示、高速数据采集、并

和快速响应的应用。

USB等。

行计算等。

3

寄存器

用于存储临时数据和控制单元的状态信息。

80C51的存储系统:ROM与RAM的区别

ROM

RA M

只读存储器,用于存储程序和常量数据。

随机存储器,用于存储变量和临时数据。

片内I/O口的构成和使用

引脚接口

输入模式

通过引脚连接外部设备和单片机。

接收外部信号并将其转换为数字信号。

输出模式

通信接口

将数字信号转换为外部的模拟或数字信号。

80C51芯片在各个行业中

的特点,提供了出色的性

RAM,使得80C51非常灵

得到广泛应用,包括消费

能表现,适用于各种领域

活,能够适应不同的应用

电子、通信、汽车电子、

的嵌入式应用。

需求。

医疗设备等领域。

单片机中的CPU结构和工作原理

1

控制单元

负责指令解码和控制单片机的操作。

2

运算单元

执行算术和逻辑运算,以及位操作等基本操作。

单片机第2章80C51的结

构与原理课件

本课件将详细介绍单片机80C51的结构和原理。包括单片机的基本结构与分

类、80C51芯片的特点与应用、CPU结构和工作原理、ROM与RAM的区别等内

容。

80C51芯片:特点与应用

1

80C51单片机的基本结构和工作原理(课堂PPT)

27

(1) 程序存储器 程序存储器内部结构参见图2-8,程序存储器就是

用来存放编好的程序和表格常数,它以程序计数器PC作地 址指针。由于80C51单片机采用16位的程序计数器和16位 的地址总线,因此,可寻址的地址空间为64 KB,且这 64K地址是片内外连续、统一的。

7

2.2 80C51单片机内部结构 和引脚功能

2.2.1 80C51的内部结构

80C51单片机的内部结构如图2-2所示。它主要由以 下几个部分组成:1个8位的中央处理器;4KB的 EPROM/ROM;128B的RAM;32条I/O线;2个定时器/计 数器;1个具有5个中断源、2个优先级的中断嵌套结构; 用于多处理机通讯、I/O口扩展或全双工通用异步接收发 器(UART);特殊功能寄存器(SFR);1个片内振荡器 和时钟电路。这些部件通过内部总线连接起来,构成一个 完整的微型计算机。

2

3

图2-1 80C51单片机的基本组成框图

①程序存储器(ROM)

程序存储器用来存放程序和始终要保留的常数。常

用的有片内掩膜ROM、可编程ROM(PROM)、可擦除 可编程ROM(EPROM)、电可擦除可编程型ROM (E2PROM)

8031片内没有程序存储器

8051内部设有4KB的掩模ROM程序存储器

8751是将8051片内的ROM换成EPROM

89C51则换成4KB的闪速EEPROM

89S51结构同89C51,4KB的闪速EEPROM可在线编程

增强型52、54、58系列的存储容量为普通型分别为

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

7. 中断系统 80C51单片机的中断功能较强,具有内、外共五个 中断源,即外中断两个,定时/计数中断2个,串行中断1 个。全部中断分为高级和低级二个中断优先级。 8.定时电路及元件 . 计算机的整个工作是在时钟信号的驱动下,按照严格 的时序有规律地一个节拍一个节拍地执行各种操作。单 片机内部设计有定时电路,只需外接振荡元件即可工作。 外接振荡元件一般选用晶体振荡器,或用价廉的RC振荡 器,也可用外部时钟源,作为振荡元件。近来有的单片 机将振荡元件也集成在芯片内部。

定时 和 控制 逻辑

指 令 寄 存 器

指 令 译 码 器

PSW

PCON SCON TMOD TCON TH0 TL0 TH1 TL1 SBUF(TX/RX) IE IP 中断、串行口和定时器逻辑

PC递增器 程序计数器PC

DPTR指针 通道1锁存器 通道1驱动器 通道3锁存器 通道3驱动器

振荡器

XTAL1

2.1.2 80C51单片机的内部结构

P0.0~P0.7

P2.0~P2.7

通道0驱动器 VCC (+5V) RAM地址 锁存器

通道2驱动器

RAM

通道0锁 存器

通道2锁 存器

ROM/ EPROM 程序地址寄存器

GND

B寄存器

ACC TMP2 ALU TMP1

堆栈指针SP

缓冲器

PSEN ALE RST EA

以80C51为例,单片机系统结构框图(或见教材图2.1)。 (1)一个8位微处理器CPU。 (2)数据存储器RAM和特殊功能寄存器SFR(128B)。 (3)内部程序存储器ROM(4KB)。 (4)两个定时/计数器T0和 T1 ,用以对外部事件进行计数,也可 用作定时器。 (5)四个8位可编程的I/O(输入/输出)并行端口P0~P3,每个端 口既可做输入,也可做输出。 (6)一个串行端口,用于数据的串行通信。 (7)中断控制系统。 (8)内部时钟电路。

由于AT89C2051的IO线很少,导致它无法外加RAM和程序ROM,片内 Flash存储器也少,但它的体积比AT89C51小很多,在开发工作中可根据实 际需要来选用。它们各有其特点,但其核心是一样的。

按引脚的功能可分为三部分 : 1. 电源和晶振: 电源和晶振 ·Vcc——运行和程序校验时接电源正端。 ·Vss——接地。 ·XTAL1——片内振荡器的反相放大器输入端 。 ·XTAL2——片内振荡器的反相放大器输出端。 对于80C51,使用外部振荡器 外部振荡器时,外部振荡信号应直 外部振荡器 内部方式时,时钟发生器 接加到XTAL1,而XTAL2悬空。内部方式 内部方式 对振荡脉冲二分频 脉冲二分频,如晶振为12MHz,时钟频率就为6MHz。 脉冲二分频 晶振的频率可以在1MHz-24MHz内选择。微调电容取30PF 左右(见图所示)。

(1)运算器电路 ) 运算电路是单片机的运算部件,用于实现算术和逻辑运算。 运算器电路包括:ALU(Arithmetic Logic Unit)、ACC(累加器)、 B寄存器、程序状态字PSW(Program Status Word)、TEMP1和TEMP2 两个暂存器等。 运算电路以ALU为核心,基本的算术和逻辑运算均在其中进行, 运算和操作的状态由PSW状态寄存器保存。 (2)控制器电路 ) 控制电路是单片机的指挥控制部件,保证单片机各部分能自动 而协调地工作。 控制器电路包括:PC(Program Counter)、PC递增器、指令寄存 器、指令译码器、定时与控制逻辑等。 单片机执行指令是在控制电路的控制下进行的。 执行一条指令的大致过程:读出指令->指令寄存器->指令译码器 (译码)->定时与控制逻辑电路(由控制定时逻辑电路产生各种定时信 和控制信号,然后送往系统各部件去进行相应的操作)。

5. 串行 口 串行I/O口 目前高档8位单片机均设置了全双工串行 全双工串行I/O口 ,用以 口 全双工串行 实现与某些终端设备进行串行通信,或者和一些特殊功能 的器件相连接的能力,甚至用多个单片机相连构成多机系 统。随着应用的拓宽,有些型号的单片机内部还包含有二 个串行I/O口。 6. 定时器 计数器 定时器/计数器 在单片机的实际应用中,往往需要精确的定时,或者需 对外部事件进行计数。为了减少软件开销和提高单片机的 实时控制能力,因而均在单片机内部设置定时器/计数器 电路。80C51共有二个 位的定时器/计数器 共有二个16位的定时器 计数器,80C52则有 有 共有二个 位的定时器 计数器 三个16位的定时器 计数器。 位的定时器/计数器 三个 位的定时器 计数器。

XTAL2

P1.0~P1.7

P3.0~P3.7

图 2.2 80C51的内部结构框图

80C51单片机的内部结构框图如图 2.2 所示(或见教材 P12), 主要包括中央处理器CPU (算术逻辑部件 ALU、 控制器等) 、只读存储器 ROM、 随机存取存储器RAM、 定时器/计数器 计数器、并行 串行口、中断系统 定时器 计数器 并行 I/O口 P0~P3、串行口 中断系统 口 串行口 以及定时控制逻辑 定时控制逻辑电路等。 定时控制逻辑 这些部件通过内部总线连接起来,基本结构仍然是 通用CPU加上外围芯片的结构模式,但功能单元上的控 制与先前相比有重大变化,采用了特殊功能寄存器 (SFR:Special Function Registers) 进行集中控制 集中控制的方法。 集中控制 1.中央处理器 中央处理器 单片机中的中央处理器(CPU)是单片机的核心,主要 完成运算和控制功能,又增设了“面向控制”的处理功 能,增强了实时性。 按其功能,中央处理器包括运算器和控制器两部分电 路。

在单片机中,常把寄存器(如工作寄存器、特殊功能 寄存器、堆栈等)在逻辑上划分在片内RAM空间中,所 以可将单片机内部RAM看成是寄存器堆,有利于提高运 行速度。 当内部RAM容量不够时,还可通过串行总线或并行 总线外扩数据存储器。 4. 并行 口 并行I/O口 单片机往往提供了许多功能强、使用灵活的并行输入 /输出引脚,用于检测与控制。有些I/O引脚还具有多种功 能,比如可以作为数据总线的数据线、地址总线的地址线、 控制总线的控制线等。单片机I/O引脚的驱动能力也逐渐 增大,甚至可以直接驱动外扩的LED显示器。 80C51有四个 位的I/O口(P0、P1、P2、P3) ,以实 有四个8位的 口 有四个 位的 现数据的并行输入输出。 现数据的并行输入输出。

图 80C51的振荡器方式

2. I/O: 共4个口,32根I/O线。 · P0——8位、漏极开路的双向I/O口。 当使用片外存储器(ROM及RAM)时,作低八位地 址和数据总线分时复用。 P0口(作为总线时)能驱动 8个 LSTTL负载。 ·P1——8位、准双向I/O 口。 在编程/校验期间,用做输入低位字节地址。 P1口可以驱动 4个 LSTTL负载。

表 2-1 P3口的第二功能表

I/O口 第二功能 注 释 串行口数据接收端 串行口数据发送端

P3.0 P3.1 P3.2 P3.3 P3.4 P3.5 P3.6 P3.7

RXD

TXD

/INT0 /INT1 T0 T1 /WR

外部中断请求0 外部中断请求1 定时/计数器0外部输入

我们要从计算机五个基本组成部分的观点来理解 单片机的系统结构。微型计算机的基本组成可概括为 三个部分,即中央处理器 中央处理器CPU (通常包括运算器和控制 中央处理器 器)+存储器 输入 输出 (I/O) 接口 存储器+输入 接口。若将组成计算机的 存储器 输入/输出 基本部件集成在一块芯片上,则俗称为单片机 单片机/MCU。 单片机

2.1.3 80C51单片机的信号引脚及其功能 单片机的信号引脚及其功能

80C51 有 40 引 脚 双 列 直 插 ( DIP ) 、 44 引 脚 (PLCC) 和 44 引 脚 ( PQFP/TQFP ) 封 装 形 式 。 80C51/80C52的封装及逻辑图如图2.3a所示(或见 教材P15图2.3)。 在某些场合,不需通过并行总线扩展芯片,这 时常采用20引脚双列直插(DIP)甚至仅14引脚的单 片机,如ATMEL公司的1051/2051/4051单片机等, பைடு நூலகம்PHILIPS公司的P87LPC764单片机。它们的封 装及引脚见图2.3b。

·P2——8位、准双向I/O口。 当使用片外存储器(ROM及RAM)时,输出高8 位地址。 在编程/校验期间,接收高位字节地址。 P2口可以驱动4个LSTTL负载。 · ——8 ·P3——8位、准双向I/O口,具有内部上拉电路。 I/O P3提供了各种替代的第二功能。在提供这些功能时, 其输出锁存器应由程序置 1。P3口可以输入/输出4个 LSTTL负载。 P3口第二功能(实际使用时,总是按需要优先选择 第二功能,剩下不用的才作口线使用),P3口第二功能 见表2-1所示(或见教材P16)。

2. 程序存储器

根据内部是否带有程序存储器而形成三种型号:内部没有程序存储 器的称80C31,内部带ROM的称80C51,内部以EPROM代替ROM的称 87C51。 目前单片机的程序存储器有以下几种结构形式: ⑴ 片内只读存储器 片内掩膜ROM的特点是程序必须在制作单片机时写入。 ⑵ 片内可编程的 片内可编程的ROM 可直接由用户进行编程。 ·紫外线可擦除型ROM-EPROM型单片机 (如87C51)。EPROM需用 紫外线擦除,必须脱机固化,不能在线改写。 · 电 可 擦 除 型 ROM——EEPROM , 称 为 Flash 单 片 机 ( 如 89C51) 。 EPROM和EEPROM都是可以多次擦除和编程的,或称MTP的ROM (MTP:Multiple Time Programmable)。

·OTP的 ROM,仅允许用户一次编程(OTP:Only Time Programmable)。 ⑶ 片外只读存储器 利用单片机的并行扩展技术可以外扩片外只读存储 器。 3. 数据存储器(RAM) 数据存储器( ) 在单片机中,用随机存取存储器(RAM)来存储程 序在运行期间的工作变量和数据,所以称为数据存储器。 一般在单片机内部设置一定容量(64B至384B)的RAM。 这样,小容量的数据存储器以高速RAM的形式集成在单 片机内,以加快单片机运行的速度,还可以使存储器的功 耗下降很多。