1 微处理器及总线(2)

《微型计算机原理与接口技术》习题及答案

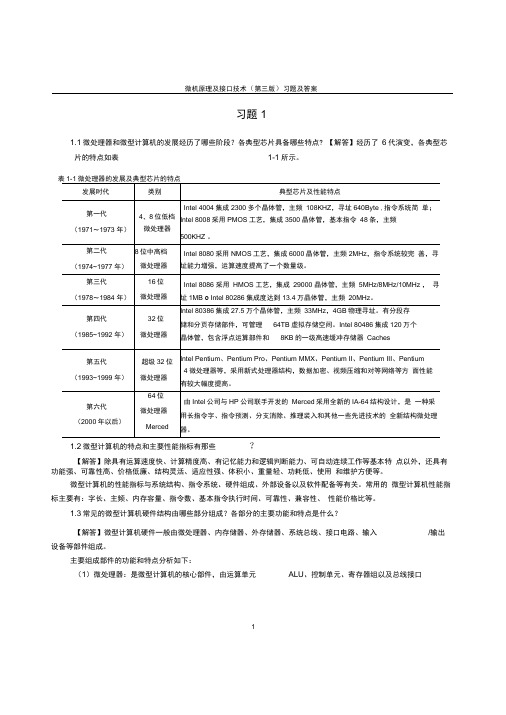

微机原理及接口技术(第三版)习题及答案习题11.1微处理器和微型计算机的发展经历了哪些阶段?各典型芯片具备哪些特点? 【解答】经历了6代演变,各典型芯片的特点如表1-1所示。

1.2微型计算机的特点和主要性能指标有那些?【解答】除具有运算速度快、计算精度高、有记忆能力和逻辑判断能力、可自动连续工作等基本特点以外,还具有功能强、可靠性高、价格低廉、结构灵活、适应性强、体积小、重量轻、功耗低、使用和维护方便等。

微型计算机的性能指标与系统结构、指令系统、硬件组成、外部设备以及软件配备等有关。

常用的微型计算机性能指标主要有:字长、主频、内存容量、指令数、基本指令执行时间、可靠性、兼容性、性能价格比等。

1.3常见的微型计算机硬件结构由哪些部分组成?各部分的主要功能和特点是什么?【解答】微型计算机硬件一般由微处理器、内存储器、外存储器、系统总线、接口电路、输入/输出设备等部件组成。

主要组成部件的功能和特点分析如下:(1)微处理器:是微型计算机的核心部件,由运算单元ALU、控制单元、寄存器组以及总线接口1微机原理及接口技术习题及答案部件等组成,其功能是负责统一协调、管理和控制系统中的各个部件有机地工作。

(2)内存储器:用来存放计算机工作过程中需要的操作数据和程序。

可分为随机存储器RAM和只读存储器ROM。

RAM存放当前参与运行的各种程序和数据,特点是信息可读可写,存取方便,但信息断电后会丢失;ROM用于存放各种固定的程序和数据,特点是信息固定不变,关机后原存储的信息不会丢失会丢^(3)系统总线:是CPU与其它部件之间传送数据、地址和控制信息的公共通道。

可分成数据总线DB、地址总线AB、控制总线CB。

(4)输入/输出接口电路:完成微型计算机与外部设备之间的信息交换。

由寄存器组、专用存储器和控制电路等组成。

(5)主机板:由CPU插座、芯片组、内存插槽、系统BIOS、CMOS、总线扩展槽、串行/并行接口、各种跳线和一些辅助电路等硬件组成。

微处理器的工作原理

微处理器的工作原理

微处理器是计算机的核心组件之一,它具有执行各种计算任务和控制计算机操作的功能。

微处理器的工作原理可以总结为以下几个关键步骤:

1. 取指令:微处理器从内存中读取指令,并将其存储在指令寄存器(IR)中。

2. 解码指令:微处理器解码指令以确定应该执行的操作。

3. 执行操作:根据解码后的指令,微处理器执行相应的操作,如加法、减法、逻辑运算等。

4. 访问存储器:在执行操作的过程中,微处理器可能需要从内存中读取数据或将结果写入内存。

5. 更新寄存器:微处理器利用寄存器来存储临时数据和运算结果。

在执行操作的过程中,微处理器将根据需要更新寄存器中的内容。

6. 控制流程:微处理器根据指令执行的结果来决定下一步应该执行的指令。

这包括跳转指令、条件分支等。

以上是微处理器的基本工作原理。

微处理器通过不断循环这些步骤,可以高效地执行各种计算任务,并控制计算机的运行。

随着技术的发展,微处理器的性能和功能不断提升,使得计算机能够进行更加复杂和高效的计算和操作。

微机原理与接口第3章2—8086微处理器总线周期及引脚资料

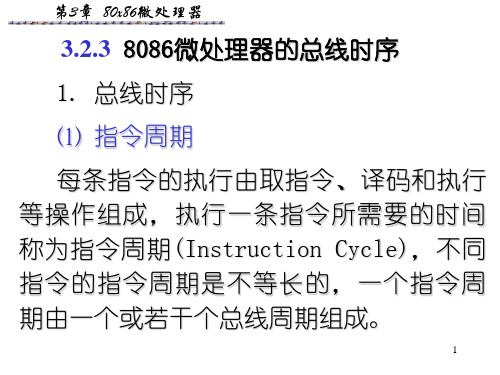

3.2.3 8086微处理器的总线时序 1. 总线时序

⑴ 指令周期

每条指令的执行由取指令、译码和执行 等操作组成,执行一条指令所需要的时间 称为指令周期(Instruction Cycle),不同 指令的指令周期是不等长的,一个指令周 期由一个或若干个总线周期组成。

1

第3章 80x86微处理器

– 4个时钟周期编号为T1、T2、T3和T4 – 总线周期中的时钟周期也被称作“T状态” – 时钟周期的时间长度就是时钟频率的倒数

• 当需要延长总线周期时插入等待状态Tw • CPU进行内部操作,没有对外操作时,其引脚就处

于空闲状态Ti

12

第3章 80x86微处理器

第3章:3.2 8088的总线时序(续3)

(c)

3

第3章 80x86微处理器

⑴ 总线读操作时序

当8086 CPU 进行存储器或I/O端口读操作 时,总线进入读周期。基本的读周期由4个时 钟周期组成:T1、T2、T3和T4。CPU在T3到T4之间 从总线上接收数据。当所选中的存储器和外设 的存取速度较慢时,则在T3和T4之间将插入1个 或几个等待周期TW。图3.3是8086最小方式下的 总线读操作时序图。下面对图中表示的读操作 时序进行说明。

⑵ 总线周期

8086CPU与外部交换信息总是通过总线进行的 。CPU的每一个这种信息输入、输出过程所需要 的时间称为总线周期(BusCycle),一般一个总线 周期由四个时钟周期组成。

⑶ 时钟周期

时钟脉冲的重复周期称为时钟周期 (Clock Cycle)。时钟周期是CPU的时间基准,由计算机 的主频决定。如8086的主频为5MHz,1个时钟周 期就是200ns。

11

第2章8086微处理器1-2

忙碌

1)CPU执行指令时总线处于空闲状态 ) 执行指令时总线处于空闲状态 2)CPU访问存储器 存取数据或指令 时要等待总线操作的完成 访问存储器(存取数据或指令 ) 访问存储器 存取数据或指令)时要等待总线操作的完成 缺点: 缺点:CPU无法全速运行 无法全速运行 解决:总线空闲时预取指令, 解决:总线空闲时预取指令,使CPU需要指令时能立刻得到 需要指令时能立刻得到

6

结论

指令预取队列的存在使EU和 指令预取队列的存在使 和BIU两个部 两个部 分可同时进行工作, 分可同时进行工作,从而 提高了CPU的效率; 降低了对存储器存取速度的要求

7

8088/8086 CPU的特点

采用并行流水线工作方式 对内存空间实行分段管理: 对内存空间实行分段管理:

每段大小为16B~ 每段大小为16B~64KB 16B 用段地址和段内偏移实现对1MB空间的寻址 用段地址和段内偏移实现对1MB空间的寻址 设置地址段寄存器指示段的首地址

支持多处理器系统; 支持多处理器系统; 片内没有浮点运算部件, 片内没有浮点运算部件,浮点运算由数学协处 理器8087支持(也可用软件模拟) 理器 支持(也可用软件模拟) 支持 注:80486DX以后的CPU均将数学协处理 器作为标准部件集成到CPU内部

8

二、8086CPU的内部结构

8086内部由两部分组成: 内部由两部分组成: 内部由两部分组成 执行单元(EU) 执行单元( ) 总线接口单元(BIU) 总线接口单元( )

2

指令预取队列(IPQ)

指令的一般执行过程: 指令的一般执行过程: 取指令 指令译码 读取操作数 执行指令 存放结果

3

串行工作方式:

8086以前的CPU采用串行工作方式: 8086以前的CPU采用串行工作方式: 以前的CPU采用串行工作方式

微机原理一至四章课后习题[1]

![微机原理一至四章课后习题[1]](https://img.taocdn.com/s3/m/88c8ee1f6bd97f192279e9c3.png)

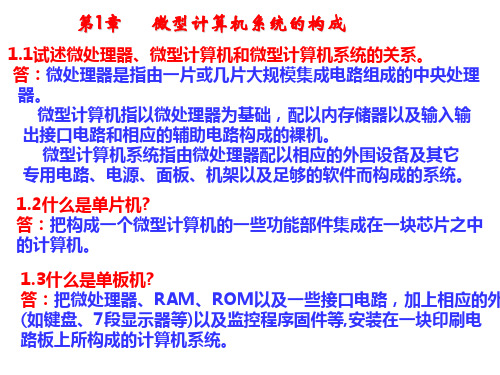

第一章习题1简答:微处理器也叫CPU或中央处理器,包括运算器、控制器、寄存器组和内部总线。

微型计算机包括CPU、内存、I/O接口、系统总线。

微型计算机系统由硬件系统和软件系统共同构成微型机系统,是相辅相成的,缺一不可关系:微型计算机是以微处理器为核心,微型计算机系统是以微型计算机为核心,它们都不能独立工作,只有微型计算机系统才是完整的数据处理系统,才具有实用意义。

2简答:微型计算机由CPU、内存、I/O接口、系统总线组成。

3简答:在CPU内部连接各寄存器及运算部件之间的总线称为微处理器总线,即内部总线。

总线由三类传输线组成:数据线、地址线和控制线。

4答:微型计算机的工作过程就是逐条执行指令序列的过程,也就是不断的取指令和执行指令的过程。

在去指令阶段,把指令的地址赋给程序计数器PC,CPU从内存中读出的内容为指令,把它送入指令寄存器,由指令译码器译码,经控制器发出相应的控制信号。

在执行指令阶段,CPU执行指令所规定的具体操作。

一条指令执行完毕,就转入下一条指令的取指令阶段,这样周而复始的循环直到程序结束。

第二章习题一、填空题1、执行部件EU的组织有:,和。

2、8086CPU从偶地址访问内存1个字时需占用周期,而从奇地址访问内存1个字操作需占用周期。

3、IBM-PC机中的内存是按段存放信息的,一个段最大存贮空间为字节。

4、8086微处理机在最小模式下,用来控制输出地址是访问内存还是访问I/O。

5、一台计算机能执行多少种指令,是在时确定的。

二、单项选择题1、微型计算机的性能主要由来决定。

A、价钱B、CPUC、控制器D、其它2、对微处理器而言,它的每条指令都有一定的时序,其时序关系是A、一个时钟周期包括几个机器周期,一个机器周期包括几个指令周期。

B、一个机器周期包括几个指令周期,一个指令周期包括几个时钟周期。

C、一个指令周期包括几个机器周期,一个机器周期包括几个时钟周期。

D、一个指令周期包括几个时钟周期,一个时钟周期包括几个机器周期。

微机原理的三种总线和CPU的寻址方式完美版

高8位

低8位

CPU 奇存储体

A0~A18

A0~A18

1

0

偶存储体

8、8086与奇偶存储体连接图

低8位数据

高8位数据

① CPU的A1~A19与奇偶存储体的A0~A18对应 相连,同时选通某字对应的高、低字节存储单元;

②A0低电位选中偶存储体,输入/出该字的低8位数据; ③BHE低电位选中奇存储体输入/出该字的高8位数据。

2.3 试说明段寄存器的作用。 答:8086微处理器中的16位寄存器,用来存放对应的存储段的 段基值—段起始地址的高16位。通过段寄存器值和指令中给出 的16位段内偏移量,可得出存储器操作数的物理地址(20位)。

2.4 试说明8086的引脚信号中M/IO、DT/R、RD、WR、ALE和BHE 的作用。 答:8086的引脚信号中 M/IO*的作用是,存储器/I/O选择信号(输出)。用于区分当前 操作是访问存储器还是访问I/O端口。若该引脚输出高电平,表示 访问存储器;若输出低电平,表示访问I/O端口。 DT/R*的作用是,数据发送/接收信号(输出)用于指示数据 传送的方向,高电平表示CPU发送数据,低电平表示CPU接收数据。 该信号常用于数据缓冲器的方向控制。(T) RD*的作用是,读控制信号(三态输出),低电平有效时, 表示CPU正从存储器或I/O端口读取信息。 WR*的作用是,写控制信号(三态、输出),低电平有效。有 效时表示CPU正将信息写入存储器或I/O端口。 ALE的作用是,地址锁存允许,高电平有效。有效时表示地址 线上的地址信息有效。 BHE*的作用是,数据总线高8位输出允许 / 状态S7信号。在 总线周期的T1时刻,为数据总线高8位允许信号BHE,低电平有效, 有效时允许高8位数据在D15—D8总线上传送。

第2章_微型计算机系统基础(2)

2.2.3 存储器

计算机的存储器用来存放程序和数据,其容量的大 小、存取数据速度的快慢将直接影响到微机系统的性能。

随机存储器 RAM

主存储器 (内 存) 只读存储器 ROM 可编程只读存储器 PROM 可改写只读存储器 EPROM

存 储 器

外存储器 (辅助存储 器)

磁盘存储器:软磁盘、硬磁盘 光盘存储器

(3)控制总线(CB):用于传送控制信 息和时序信息。控制信息中,有的是 CPU向内存或CPU向I/O接口电路发出的 信号,如读/写信息、片选信号、中断 响应信号等。控制总线上的信息传送方 向由具体控制信号而定,一般是双向的, 控制总线的位数要根据系统的实际需要 确定。

3.外部总线 外部总线是微型计算机和外部设备 之间的总线,微型计算机作为一种设备, 通过该总线和其他设备进行信息与数据 交换。

内存地址

RAM在实际存储的时候被分成 为许多等长的存储单元,在微机 中一般按照字节存储,即按字节 来分存储单元。比如,如果有内 存1kB,则被分为1024个存储单 元。每个存储单元将被赋予一个 编号即内存地址。 注意区分内存地址和内存 地址中的内容。

FFFFH

0002H

0001H

0000H

2、外存

2.2.7 微型计算机的主要性能指标

性能指标

(分32位、64位等几种字长)

重点

字长:计算机一次可并行处理的二进制数码的位数

运算速度(或时钟频率)——MIPS(每秒百万条指令) 主频,即主时钟频率。 80486:33MHZ~66MHZ之间 Pentium 4:2.4GHZ 频率越高,速度越快。 主(内)存贮器的容量:128MB/256MB/512MB/1GB等 外部设备配置 此外,还有功能指标、可靠性指标、兼容性指标等。

微机原理与接口技术第二章习题解答

微机原理与接口技术(楼顺天第二版)习题解答第2章8086CPU的结构与功能2.1答:微处理器内部结构由四部分组成:(1)算术逻辑运算单元ALU :完成所有的运算操作;(2)工作寄存器:暂存寻址信息和计算过程中的中间结果;(3)控制器:完成指令的读入、寄存和译码,并产生控制信号序列使ALU完成指定操作;(4 )1/0控制逻辑:处理I/O操作。

2.2答:微处理器级总线有三类:(1 )数据总线:传送信息;(2)地址总线:传送地址码;(3 )控制总线传送控制信号。

2.3答:地址码只能由CPU生成。

而数据需要在CPU和存储器之间传输。

2.4答:8086CPU对存储器按20位地址编址,从00000H~FFFFFH ;I0端口按16位编址,从0000H~FFFFH。

为独立编址方式。

统一编址优点为存储器与I/O端口访问指令一致,寻址方式多,缺点是I/O端口地址占用了一定范围的存储器地址;独立编址的优点是存储器与I/O端口有各自的地址,缺点是需要有专门的指令,使得指令系统复杂。

2.5 8086CPU按内部功能可分为BIU和EU两部分。

BIU主要完成取指令、存储数据操作;EU的功能是执行指令规定的操作。

EU和BIU可以独立、并行执行,但相互之间会有协作。

当指令队列中还没有指令时,EU处于等待状态,当EU执行指令需要访问存储器或I/O端口时,BIU应尽快完成存取数据的操作。

2.6答:8086CPU内部有14个16位寄存器,其中8个通用寄存器(4数据寄存器AX、BX、CX、DX,4地址指针/变址寄存器SI、DI、SP、BP),4个段寄存器(CS、DS、ES、SS), 2个控制寄存器(指令指针IP,微处理器状态字PSW)。

应该注意的是:可以在指令中用作为地址指针的寄存器有:SI、DI、BP和BX ;在微处理器状态字PSW中,一共设定了9个标志位,其中6个标志位用于反映ALU前一次操作的结果状态(CF,PF,AF,ZF,SF,OF ),另3个标志位用于控制CPU操作(DF,IF,TF )。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

2. 几种基本时序

本节展开8088CPU最小模式下的最基本的4种 总线周期 存储器读总线周期 存储器写总线周期 I/O读总线周期 I/O写总线周期

存储器写总线周期 CLK

IO/M*

A19/S6 ~ A16/S3 A15 ~ A8

AD7 ~ AD0

ALE WR*

T1

T2

T3

T4

A19 ~ A16 A7 ~ A0

1. 内存数据的存储格式

计算机中信息的单位

二进制位Bit:存储一位二进制数:0或1

字节Byte:8个二进制位,D7~D0 字Word:16位,2个字节,D15~D0 双字DWord:32位,4个字节,D31~D0

最低有效位LSB:数据的最低位,D0位

最高有效位MSB:数据的最高位,对应字节、字、双字分 别指D7、D15、D31位

五. 8088 CPU的工作时序

CPU引脚如何相互配合、控制系统工作—时序 时序(Timing)是指信号高低电平(有效或 无效)变化及相互间的时间顺序关系 CPU时序决定系统各部件间的同步和定时 CPU时序有三级 指令周期 → 总线周期 → 时钟周期

什么是指令、总线和时钟周期?

1.指令周期、总线周期、时钟周期

处理器利用DS:EA存取数据段中的数据

附加段寄存器ES(Extra Segment)

附加段是附加的数据段,也保存数据:

附加段寄存器ES存放附加段的段地址 各种主存寻址方式(有效地址EA)得到存储器 中操作数的偏移地址

处理器利用ES:EA存取附加段中的数据 串操作指令将附加段作为其目的操作数的 存放区域

为减少芯片引线,有许多引线具有双重定义和 功能,分时复用方式,即在不同时刻,这些引 线上的信号是不相同的

8088的引脚图

GND

A14 A13 A12 A11 A10 A9 A8 AD7 AD6 AD5 AD4 AD3 AD2 AD1

AD0 NMI INTR CLK GND

1

40

2

39

3

38

4

37

5

8088有8个8位通用寄存器、8个16位通用 寄存器 8088有6个状态标志和3个控制标志 8088将1MB存储空间分段管理,有4个段寄 存器,对应4种逻辑段 8088有4个段超越前缀指令,用于明确指定 数据所在的逻辑段

熟悉上述内容后,就可以进入下节

8086/8088的地址产生小结

逻辑地址:<段地址,偏移量> 段地址:CS, DS, ES, SS段基址寄存器 偏移量:SP, BP, DI, SI, IP等指针寄存器 上述寄存器都是16位的

存储器读总线周期

T1

T2

T3

T4

CLK

IO/M*

A19/S6 ~ A16/S3 A15 ~ A8

AD7 ~ AD0

A19 ~ A16 A7 ~ A0

S6 ~ S3 A15 ~ A8

输入数据

ALE RD*

READY

(高电平)

T1状态——输出20位存储器地址A19 ~ A0 IO/M*输出低电平,表示存储器操作; ALE输出正脉冲,表示复用总线输出地址 T2状态——输出控制信号RD* T3和Tw状态——检测数据传送是否能够完成 T4状态——前沿读取数据,完成数据传送

堆栈段确定堆栈所在的主存区域

堆栈段寄存器SS存放堆栈段的段地址 堆栈指针寄存器SP指示堆栈栈顶的偏移地址

处理器利用SS:SP操作堆栈顶的数据

数据段寄存器DS(Data Segment)

数据段存放运行程序所用的数据

数据段寄存器DS存放数据段的段地址 各种主存寻址方式(有效地址EA)得到存储器 中操作数的偏移地址

36

6

35

7 8088 34

8

33

9

32

10

31

11

30

12

29

13

28

14

27

15

26

16

25

17

24

18

23

19

22

20

21

VCC

AD15 AD16 / S3 AD17 / S4

AD18 / S5 AD19 / S6 SS0*

(HIGH)

MN / MX*

RD*

HOLD (RQ)*/ GT0*)

HLDA (RQ1* /GT1*)

段地址左移4位 加上偏移地址

14600H 13800H + 100H + F00H

得到物理地址

14700H 14700H

3. 段寄存器

8088有4个16位段寄存器

CS(代码段)指明代码段的起始地址 SS(堆栈段)指明堆栈段的起始地址 DS(数据段)指明数据段的起始地址 ES(附加段)指明附加段的起始地址

你能区别寄存器、存储器(内存)、外存(包 括硬盘、光盘、磁带等存储介质)吗?

答案

寄存器、存储器和外存的区别

寄存器是微处理器(CPU)内部暂存数据的存储 单元,以名称表示,例如:AX,BX..….等 存储器也就是平时所说的主存,也叫内存,可直 接与CPU进行数据交换。主存利用地址区别 外存主要指用来长久保存数据的外部存储介质, 常见的有硬盘、光盘、磁带、U盘等。外存的数据 只能通过主存间接地与CPU交换数据 程序及其数据可以长久存放在外存,在运行需要 时才进入主存

总线周期 IO/M* WR* RD*

存储器读 低

高

低

存储器写 低

低

高

I/O读 I/O写

高

高

低

高

低

高

图:8088的功能结构

通用 寄存器

AH AL BH BL CH CL DH DL

SP BP SI DI

16位

地址 加法 器

20位地址总线 ∑

CS DS SS ES IP 内部寄存器

外 部 总 输入/输出 线

4个时钟周期编号为T1、T2、T3和T4 总线周期中的时钟周期也被称作“T状态” 时钟周期的时间长度就是时钟频率的倒数

当需要延长总线周期时插入等待状态何Tw时有总线周期?

何时有总线周期?

任何指令的取指阶段都需要存储器读总线周期, 读取的内容是指令代码

任何一条以存储单元为源操作数的指令都将引起 存储器读总线周期,任何一条以存储单元为目的 操作数的指令都将引起存储器写总线周期 只 有 执 行 IN 指 令 才 出 现 I/O 读 总 线 周 期 , 执 行 OUT指令才出现I/O写总线周期 CPU响应可屏蔽中断时生成中断响应总线周期

同一个存储器地址可以是字节单元地址、字单 元地址、双字单元地址等等(视具体情况来确定)

80x86处理器采用“低对低、高对

高”的存储形式,被称为“小端方式

Little Endian”。

图示

相 对 应 还 存 在 “ 大 端 方 式 Big

Endian”。

2. 存储器的分段管理

8088CPU访问内存有20条地址线 物理地址

T4状态——完成数据传送

I/O写总线周期 CLK

IO/M*

A19/S6 ~ A16/S3 A15 ~ A8

AD7 ~ AD0 ALE

WR*

T1

T2

T3

T4

0000 A7 ~ A0

S6 ~ S3 A15 ~ A8

输出数据

READY

(高电平)

T1状态——输出16位I/O地址A15 ~ A0 IO/M*输出高电平,表示I/O操作; ALE输出正脉冲,表示复用总线输出地址 T2状态——输出控制信号WR*和数据D7 ~ D0 T3和Tw状态——检测数据传送是否能够完成 T4状态——完成数据传送

每个段寄存器用来确定一个逻辑段的起 始地址,每种逻辑段均有各自的用途

代码段寄存器CS(Code Segment)

代码段用来存放程序的指令序列

代码段寄存器CS存放代码段的段地址 指令指针寄存器IP指示下条指令的偏移地址

处理器利用CS:IP取得下一条要执行的指令

逻辑地址

堆栈段寄存器SS(Stack Segment)

微型计算机基本结构 图: 微型计算机的硬件结构

8088CPU引脚线---外部特性

CPU引脚是系统总线的基本信号 可以分成三类信号

8位数据线:D0 ~ D7 20位地址线:A0 ~ A19 控制线:

ALE、IO/M*、WR*、RD*、READY INTR、INTA*、NMI,HOLD、HLDA RESET、CLK、Vcc、GND

S6 ~ S3 A15 ~ A8

输出数据

READY

(高电平)

T1状态——输出20位存储器地址A19 ~ A0。IO/M*输出低电平,表示存储 器操作;ALE输出正脉冲,表示复用总线输出地址 T2状态——输出控制信号WR*和数据D7 ~ D0 T3和Tw状态——检测数据传送是否能够完成。通过插入Tw等待状态,来 使速度差别较大的两部分保持同步

共 220B=1MB 个 存 储 单 元 , 内 存 地 址 00000H~FFFFFH

8088CPU将1MB空间分成许多段,有4个段寄 存器,对应4种逻辑段

每个段最大限制为64KB 段地址的低4位为0000B

内部寄存器16位如何寻 址20条地址线220=1MB?

物理地址和逻辑地址

一个存储单元具有唯一物理地址(20位, 地址线寻址)、多个逻辑地址(16位,编 程用)

控制电路

ALU数据总线

ALU

执行部分 控制电路

标志寄存器 执行部件 (EU)

功能:负责指令的译码、执行和数据的运算

12 34

指令队列8088:4字节 (8086:6字节)

总线接口部件 (BIU)

功能:管理8088与系统总线的接口 负责CPU对存储器和外设进行访问