微处理器及总线2

微机原理8088的总线与时序

微机原理8088的总线与时序8088是Intel公司于1979年推出的一款16位微处理器。

它主要用于个人计算机IBM PC和互补金属氧化物半导体技术(CMOS)中。

8088的总线结构包括内部总线和外部总线。

内部总线通过内部连接的数据通路在不同的功能部件之间传输数据和控制信号。

外部总线则用于连接8088与外部设备,如内存、输入输出(I/O)设备等。

8088的总线宽度为16位,分为数据总线、地址总线和控制信号总线。

数据总线用于传输数据,宽度为16位,可以同时传输一个字节(8位)或一个字(16位)。

地址总线用于寻址,其宽度为20位,可以寻址1MB空间。

控制信号总线至少包括读(RD)、写(WR)、片选(CS)、内存读(MREQ)、I/O读(IOR)和时钟这些基本信号。

8088的时序包括外设周期、读周期、写周期和I/O周期。

外设周期用于与外部设备进行通信,包括读写外设内容和控制外设。

读周期用于从内存或外设读取数据到寄存器或内部缓冲器中。

写周期用于将内部寄存器或内部缓冲器中的数据写入到内存或外设中。

I/O周期用于从外部设备读取或写入数据。

在时序方面,8088采用了同步时序设计。

时钟信号周期(CLK周期)用于同步各个部件的工作。

时钟信号由外部提供,频率为4.77MHz,即每个时钟周期为210ns。

在一个时钟周期内可以完成一个机器周期的工作。

8088的机器周期分为5个时钟周期,即一个机器周期需要5个时钟周期完成。

根据不同的操作,一个机器周期又可以分为多个时钟周期。

不同的操作需要不同的时钟周期数来完成,包括指令周期、内存周期、I/O周期等。

具体的时序可以通过查阅8088的数据手册得到。

总的来说,8088的总线结构和时序是保证处理器与外部设备通信的关键。

通过总线结构的设计和时序的安排,8088能够快速、准确地与外部设备交互,实现数据、控制信号和地址的传输和处理。

同时,时序的设计也要考虑到时钟频率、数据传输速度等因素,以确保系统的稳定性和可靠性。

第2章-8086微处理器part2

8086 CPU在最小模式中引脚定义

M/#IO:Memory/Input & Output,三态输出

存储器或I/O端口访问信号 。指示8086的访问对象,发 给MEM或I/O接口。 M/# IO为高电平时,表示 当前CPU正在访问存储器;

M/# IO 为低电平时,表 示当前CPU正在访问I/O端 口

数据驱动器数据流向控制信 号,输出,三态。

在8086系统中,通常采用 74LS245、8286或8287作 为数据总线的驱动器,用 DT/#R信号来控制数据驱动 器的数据传送方向。 当DT/#R=1时,进行数据 发送; 当DT/#R=0时,进行数据 接收。

8086 CPU在最小模式中引脚定义

READY:准备就绪信号 由外部输入,高电平有效 ,表示CPU访问的存储器 或I/O端口己准备好传送 数据。 当READY无效时,要求 CPU插入一个或多个等待 周期Tw,直到READY信 号有效为止。

S3 0 1 0 1

当前正在使用的段寄存器 ES SS CS或未使用任何段寄存器 DS

8086 CPU在最小模式中引脚定义

#BHE/S7:高8位总线允许(Bus High Enable)

T1:指示高8位数据总线上的数据 是否有效 (#BHE:AD0)配合:00时读写字 ,01时读写奇地址字节,10时读写 偶地址字节 其他T周期:输出状态信号S7(S7 始终为逻辑1,未定义) DMA方式下,该引脚为高阻态。

最大模式引脚信号(续)

LOCK# :总线封锁(优先权锁定) 三态输出,低电平有效。 LOCK有效时表示CPU不允许其它总线主控者占用 总线。 ห้องสมุดไป่ตู้ 这个信号由软件设置。 • 当在指令前加上LOCK前缀时,则在执行这条 指令期间LOCK保持有效,即在此指令执行期 间,CPU封锁其它主控者使用总线。 在保持响应期间,LOCK#为高阻态。

【教学课件】第2章 8086微处理器

控制 电路

局部总线 接口

SYSB/RESB

1

20

2

19

3

18

4

17

5

8289 16

6

15

7

14

8

13

9

12

10

11

INIT

BCLK BREQ BPRN BPRO BUSY CBRQ

总线仲裁 信号

AEN

V CC S1 S0 CLK

LOCK

CRQLCK ANYRQST

AEN CBRQ BUSY

2021/8/17

DEN CEN

INTA IORC AIOWC IOWC

2021/8/17

23

2.总线仲裁控制器8289

仲裁电路

状态

S2

信号

S1

S0

状态 译码器

多路总线 接口

控制 输入

LOCK CLK

CRQLCK

RESB ANYRQST

IOB

S2 IOB

RESB BCLK INIT BREQ BPRO BPRN

GND

数据总线

2021/8/17

S0

S1

S2

INTR R Q / G T0

R Q / G T1

8288 总线控制器

IN T A

8259A 及有关电路

控制总线 中 断 请 求

22

1.总线控制器8288

状态

S2

信号

S1

S0

状态 译码器

控制 输入

CLK

AEN CEN IOB

控制 电路

命令 信号 发生器

控制信号 发生器

2.3.1 最小模式和最大模式的概念

I2C总线与EEPROM

I2C通信时序

• I2C总线规定了严格的数据通信格式,所有具有I2C总线 接口的器件都必须遵守。

• I2C总线上主机与从机之间一次传送的数据称为一帧, 由起始信号、数据传输部分和停止信号组成。数据传送 的基本单元为一位数据。对比UART的数据帧格式。

空闲状态:I2C总线的SDA和SCL两条信号线同时处于高 电平时,规定为总线的空闲状态。此时各个器件的输出级 场效应管均处在截止状态,即释放总线,由两条信号线各 自的上拉电阻把电平拉高。 起始信号:I2C 通信的起始信号的定义是 SCL 为高电平期 间, SDA 由高电平向低电平变化产生一个下降沿。

/* I2C 总线写操作, dat-待写入字节,返回值-从机应答位的值 *

bit I2CWrite(unsigned char dat) { bit ack; //用于暂存应答位的值 unsigned char mask; //用于探测字节内某一位值的掩码变量 for (mask=0x80; mask!=0; mask>>=1) //从高位到低位依次 { if ((mask&dat) == 0) //该位的值输出到 SDA 上 I2C_SDA = 0; else I2C_SDA = 1; I2CDelay.1 SCL/P1.0

>4.7μ s >4.0μ s

SDA/P1.1 SCL/P1.0

>4.0μ s

>4.7μ s

(a)启动

SDA/P1.1 SDA/P1.1 SCL/P1.0

>4.0μ s

(b)终止

SCL/P1.0

>4.0μ s

(c)发送0/发送应答位

(d)发送1/发送非应答位

I2C简介

• I2C总线支持多主(multi-mastering)和主从(master-slave)两 种工作方式。 • 多主方式下,I2C总线上可以有多个主机。I2C总线需通 过硬件和软件仲裁来确定主机对总线的控制权。 • 主从工作方式时,系统中只有一个主机,总线上的其它 器件均为从机(具有I2C总线接口),只有主机能对从机 进行读写访问,因此,不存在总线的竞争等问题。在主 从方式下,I2C总线的时序可以模拟 ,I2C总线的使用不 受主机是否具有I2C总线接口的制约。80C51 单片机本身 不具有I2C总线接口,可以用其I/O口线模拟I2C总线 。

微型计算机的总线技术原理分析

2021/4/21

20

(6)USB传输线能够提供100mA的电流,而带电源的USB Hub使得每个接口可以提供500 mA的电流。

(7)USB V1.1规范提供全速12Mbps的模式和低速1.5Mbps 的模式,USB V2.0规范提供高达480Mbps的数据传输速 率,可以适应各种不同类型的外设。

8位ISA总线是一种开放式的结构总线,在总线母板上有8个系 统插槽,用于I/O设备和PC机的连接。由于8位ISA总线具有价格 低、可靠性好、使用灵活等特点,并且对插板兼容性好。

8位ISA总线引脚信号总共有62条。通过一个31脚分为A、B两 面的连接插槽来实现,其中,A面为元件面,B面为焊接面。符 合ISA总线标准的接插件可以方便的插入,以便对微型计算机 系统进行功能扩展。

16位ISA总线的前62引脚的信号分布及其功能与8位ISA总线基 本相同,仅有两处作了改动。

16位ISA总线中新增加的36引脚插槽信号扩展了8位数据线、7 位地址线、存储器和I/O设备的读写控制线、中断和DMA控制线 、电源和地线等。

新插槽中的引脚信号分为C(元件面)和D(焊接面)两列。

2021/4/21

2021/4/21

13

4.3 局部总线

4.3.1 VESA总线

VESA(Video Electronics Standards Association 视频电 子标准协会)总线是一种32位接口的局部总线,通 常称为VL总线。

由于EISA总线工作频率是8MHz,而VESA局部总线工 作频率可以达到33MHz。因此,需要高速数据传输 的系统可以采用VESA局部总线。它通常用于视频和 磁盘到基于80486的PC机的接口。

PCI V2.0版本支持32/64位数据总线,总线时钟为25~ 33MHz,数据传输率达132~264MB/s。1995年推出的PCI V2.1版本支持64位数据总线,总线速度为66MHz,最大 数据传输率达528MB/s。这个速度是最初的IBM PC总线的 100倍,是最快的ISA总线的40倍。PCI总线的优良性能使 它成为当前Pentium系列芯片的最佳选择,现在所有 Pentium主板都使用了PCI V2.1和更新版的PCI总线。

微机原理与接口第3章2—8086微处理器总线周期及引脚资料

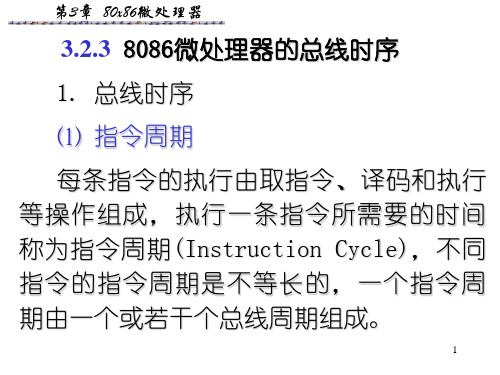

3.2.3 8086微处理器的总线时序 1. 总线时序

⑴ 指令周期

每条指令的执行由取指令、译码和执行 等操作组成,执行一条指令所需要的时间 称为指令周期(Instruction Cycle),不同 指令的指令周期是不等长的,一个指令周 期由一个或若干个总线周期组成。

1

第3章 80x86微处理器

– 4个时钟周期编号为T1、T2、T3和T4 – 总线周期中的时钟周期也被称作“T状态” – 时钟周期的时间长度就是时钟频率的倒数

• 当需要延长总线周期时插入等待状态Tw • CPU进行内部操作,没有对外操作时,其引脚就处

于空闲状态Ti

12

第3章 80x86微处理器

第3章:3.2 8088的总线时序(续3)

(c)

3

第3章 80x86微处理器

⑴ 总线读操作时序

当8086 CPU 进行存储器或I/O端口读操作 时,总线进入读周期。基本的读周期由4个时 钟周期组成:T1、T2、T3和T4。CPU在T3到T4之间 从总线上接收数据。当所选中的存储器和外设 的存取速度较慢时,则在T3和T4之间将插入1个 或几个等待周期TW。图3.3是8086最小方式下的 总线读操作时序图。下面对图中表示的读操作 时序进行说明。

⑵ 总线周期

8086CPU与外部交换信息总是通过总线进行的 。CPU的每一个这种信息输入、输出过程所需要 的时间称为总线周期(BusCycle),一般一个总线 周期由四个时钟周期组成。

⑶ 时钟周期

时钟脉冲的重复周期称为时钟周期 (Clock Cycle)。时钟周期是CPU的时间基准,由计算机 的主频决定。如8086的主频为5MHz,1个时钟周 期就是200ns。

11

在微型计算机秀浓的红两种

在微型计算机秀浓的红两种

微型计算机微处理器红分为以下几种:存储器和I/O接口电路构成。

各部分通过地址总线(AB)、数据总线(DB)和控制总线(CB)相连。

微型计算机有哪两种主要应用形态?微型计算机两种主要应用形态分别为桌面应用和嵌入式应用。

桌面应用:将CPU、存储器和I/O接口电路组装在主板上,通过接口电路与键盘、显示器连接再配上操作系统及应用软件,就形成桌面微型计算机系统。

其主要特点有哪些?在一片集成电路芯片上集成微处理器、存储器、I/O接口电路,从而构成了单芯片微型计算机,即单片机。

单片机的主要特点:控制性能和可靠性高、体积小、价格低、易于产品化;具有良好的性价比。

1、智能仪器仪表。

2、机电一体化产品。

3、实时工业控制。

4、分布系统的前端模块。

5、家用电器。

6、交通与航空航天。

微处理器CPUCPU的内部和外部结构微处理器级总线

数据寄存器Data Register

存放数据

2.4 微处理器的寄存器组织

2.地址指针和变址寄存器(4个)

均

为

SP

地 址

BP

寄

SI

存 器

DI

堆栈指针寄存器Stack Pointer 基址指针寄存器Base Pointer 源变址寄存器Source Index 目的变址寄存器Destination Index

均为16位,也能存放数据

2.4 微处理器的寄存器组织

二.段寄存器

在微机系统的内存中通常存放着三类信息: 代码(指令码) 指示CPU执行何种操作。 数据(数值、字符等) 程序处理的对象或结果。 堆栈信息 被保存的返回地址和中间结果等。

代码段 数据段 堆栈段

2.4 微处理器的寄存器组织

8086/8088CPU有4个段寄存器。

四.控制寄存器(2个)

1.指令指针寄存器(IP:Instruction Pointer )(16位)

指令指针寄存器相当于一般微处理器中的程

序计数器(PC:Program Counter )。

它始终指向CPU下一条要取指令所在存贮器单 元的偏移地址(段地址由CS提供)。

用户不能更改IP的值,只有CPU执行转移指令, 子程序调用指令和子程序返回指令以及中断处理 时,IP才作相应的改变。

2.2 微处理器的内部结构

指令寄存器(IR)

保存从存储器中读入的当前要执行的指令。

指令译码器(ID)

对指令寄存器中保存的指令进行译码分析。

控制逻辑部件

根据ID对指令的译码分析,发出相应的一系 列的节拍脉冲和电位(控制信号),去完成指令 的所有操作。