集成电路制造工艺流程(漫画)PPT课件

合集下载

《集成电路制造工艺》课件

CMOS工艺

适用广泛,消耗低功率,集成 度高

光刻和电子束刻蚀工 艺

芯片制造中影响巨大,直接决 定芯片精度和质量

IC封装技术

通过引线焊接连接芯片与外部 电路

集成电路制造工艺的未来发展方向

量子计算机

利用量子位的并行性,比传统计 算机更快速、更准确

纳米技术

更加精细的芯片制造和量子效应 的应用

3D打印

高质量、低成本的芯片制造和量 产

1 革命性

集成电路是现代科技的基础。无集成电路,无现代智能设备。

2 市场需求

集成电路产业是信息产业的核心,随着通讯和计算机的快速发展,需求量将节节攀升

集成电路制造工艺的发展历程

1

早期阶段

简单的扩散工艺和光刻工艺,可制造简单

集成度提高

2

的逻辑门和模拟器件

计算机辅助设计、离子注入、金属蒸镀等

新技术的应用,集成度不断提高

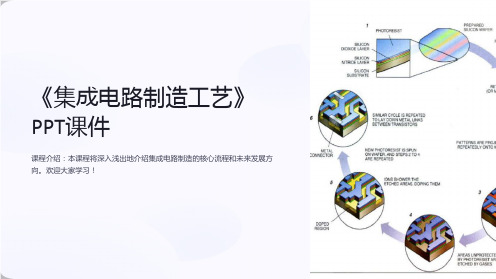

《集成电路制造工艺》 PPT课件

课程介绍:本课程将深入浅出地介绍集成电路制造的核心流程和未来发展方 向。欢迎大家学习!

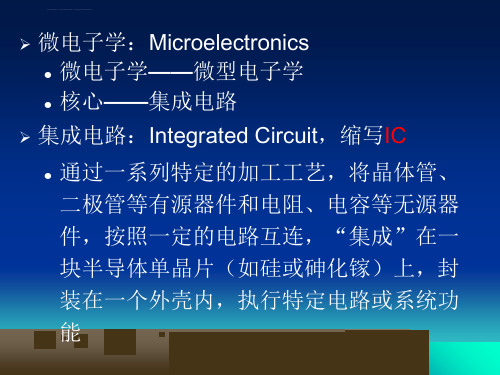

什么是集成电路?

定义

集成电路是由数百万个微小电子元器件组成的电子 电路系统,它可以完成特定的功能。

历史

集成电路的起源可以追溯到20世纪60年代,它是计 算机和通讯技术的重要基础。

为什么集成电路制造工艺如此重要?

3

现代集成电路工艺

光刻、浸没/化学机械抛光、等离子刻蚀 等高级技术的应用,如今我们拥有极复杂 的芯片设计和制造工艺。

集成电路制造工艺的工作流程

芯片设计

设计加工工艺,布图加工

芯片构造

渗透、离子注入、扩散、腐蚀

芯片掩膜制作制作掩Fra bibliotek板、晶圆复制封装测试

《集成电路工艺》课件

集成电路工艺设备

薄膜制备设备

化学气相沉积设备

用于在硅片上沉积各种薄膜,如氧化硅、氮化硅 等。

物理气相沉积设备

用于沉积金属、合金等材料,如蒸发镀膜机。

化学束沉积设备

通过离子束或分子束技术,在硅片上形成高纯度 、高质量的薄膜。

光刻设备

01

02

03

投影式光刻机

将掩膜板上的图形投影到 硅片上,实现图形的复制 。

降低成本

集成电路工艺能够实现大规模生产,降低了单个电子 元件的成本。

促进技术进步

集成电路工艺的发展推动了半导体制造技术的进步, 促进了微电子产业的发展。

02

CATALOGUE

集成电路制造流程

薄膜制备

物理气相沉积(PVD)和化学气相沉积(CVD )是最常用的两种沉积技术。

薄膜的厚度、均匀性和晶体结构等特性对集成电路的 性能和可靠性具有重要影响。

分类

按照制造工艺技术,集成电路可分为 薄膜集成电路和厚膜集成电路;按照 电路功能,集成电路可分为模拟集成 电路和数字集成电路。

集成电路工艺的发展历程

小规模阶段

20世纪60年代,晶体管被集成 在硅片上,形成了小规模集成 电路。

大规模阶段

20世纪80年代,微处理器和内 存被集成在硅片上,形成了大 规模集成电路。

02

它通过化学腐蚀和机械研磨的协同作用,将硅片表面研磨得更

加平滑,减小表面粗糙度。

抛光液的成分、抛光压力和抛光时间等参数对抛光效果具有重

03

要影响。

03

CATALOGUE

集成电路工艺材料

硅片

硅片是集成电路制造中最主要的材料之一,其质量直 接影响集成电路的性能和可靠性。

薄膜制备设备

化学气相沉积设备

用于在硅片上沉积各种薄膜,如氧化硅、氮化硅 等。

物理气相沉积设备

用于沉积金属、合金等材料,如蒸发镀膜机。

化学束沉积设备

通过离子束或分子束技术,在硅片上形成高纯度 、高质量的薄膜。

光刻设备

01

02

03

投影式光刻机

将掩膜板上的图形投影到 硅片上,实现图形的复制 。

降低成本

集成电路工艺能够实现大规模生产,降低了单个电子 元件的成本。

促进技术进步

集成电路工艺的发展推动了半导体制造技术的进步, 促进了微电子产业的发展。

02

CATALOGUE

集成电路制造流程

薄膜制备

物理气相沉积(PVD)和化学气相沉积(CVD )是最常用的两种沉积技术。

薄膜的厚度、均匀性和晶体结构等特性对集成电路的 性能和可靠性具有重要影响。

分类

按照制造工艺技术,集成电路可分为 薄膜集成电路和厚膜集成电路;按照 电路功能,集成电路可分为模拟集成 电路和数字集成电路。

集成电路工艺的发展历程

小规模阶段

20世纪60年代,晶体管被集成 在硅片上,形成了小规模集成 电路。

大规模阶段

20世纪80年代,微处理器和内 存被集成在硅片上,形成了大 规模集成电路。

02

它通过化学腐蚀和机械研磨的协同作用,将硅片表面研磨得更

加平滑,减小表面粗糙度。

抛光液的成分、抛光压力和抛光时间等参数对抛光效果具有重

03

要影响。

03

CATALOGUE

集成电路工艺材料

硅片

硅片是集成电路制造中最主要的材料之一,其质量直 接影响集成电路的性能和可靠性。

集成电路制造工艺PPT课件

掺杂工艺(Doping)

掺杂:将需要的杂质掺入特定的半导体区域 中,以达到改变半导体电学性质,形成PN结 、电阻、欧姆接触。

掺入的杂质主要是: 磷(P)、砷(As) —— N型硅 硼(B) —— P型硅 掺杂工艺主要包括:扩散(diffusion)、离

子注入(ion implantation)。

亮场版和暗场版

曝光的几种方法

接触式光刻:分辨率较高, 但是容易造成掩膜版和光刻 胶膜的损伤。

接近式曝光:在硅片和掩膜 版之间有一个很小的间隙 (10~25mm),可以大大减 小掩膜版的损伤,分辨率较 低。

投影式曝光:利用透镜或反 射镜将掩膜版上的图形投影 到衬底上的曝光方法,目前 用的最多的曝光方式。(特 征尺寸:0.25m)

❖等离子刻蚀(Plasma Etching):利用放电产生的游离 基与材料发生化学反应,形成挥发物,实现刻蚀。选择 性好、对衬底损伤较小,但各向异性较差。

❖反应离子刻蚀(Reactive Ion Etching,简称为RIE): 过活性离子对衬底的物理轰击和化学反应双重作用刻蚀 。具有溅射刻蚀和等离子刻蚀两者的优点,同时兼有各 向异性和选择性好的优点。目前,RIE已成为VLSI工艺 中应用最广泛的主流刻蚀技术。

–激活杂质:使不在晶格位置上的离子运动到晶格 位置,以便具有电活性,产生自由载流子,起到 杂质的作用。

–消除损伤

❖ 退火方式:

–炉退火

–快速退火:脉冲激光法、扫描电子束、连续波激 光、非相干宽带频光源(如卤光灯、电弧灯、石墨 加热器、红外设备等)。

氧化(Oxidation)

❖ 氧化:制备SiO2层 ❖ SiO2 是 一 种 十 分 理 想 的 电 绝 缘 材 料 , 它 的 化 学 性

第三章集成电路制造工艺 ppt课件

23

第三章

制备氧化硅时:

硅烷与氧的反应

SiH4 2O2 SiO2 2H 2O

PPT课件

24

第三章

800-1000℃

102 Pa 产量大,膜厚均匀 600-700℃

射频电场,200-400℃

PPT课件

25

第三章

PPT课件

26

第三章

3. SiO2薄膜的要求和检测方法

SiO2薄膜的要求 表面:表面厚度均匀、表面致密、无斑点、无白雾

PPT课件

12

第三章

SiO2 的基本性质

晶体结构: 结晶型(石英玻璃) 非晶态

半导体器件生产所用的SiO2 薄膜属于非晶态结构。

物理性质 惰性材料,在室温相当宽的范围内,性能十分稳定;

电阻率非常高,热氧化的SiO2 薄膜为 10 15 欧姆·厘米, 是很好的绝缘材料,高介电常数。

PPT课件

13

第三章

薄膜质量好,纯度高。

PPT课件

21

第三章

高压氧化

PPT课件

22

第三章

化学汽相沉积法 CVD

把一种(几种)元素的气体共给基片,利用某种方式激活后, 在衬底表面处发生化学反应,沉积所需的固体薄膜。

激活方式:加热、等离子体、紫外光、激光等产生高温 多晶硅、氮化硅、氧化物、碳化物等多种无机薄膜

PPT课件

PPT课件

11

第三章

一. SiO2 薄膜在集成电路中的作用 对扩散杂质起掩蔽作用

可作为MOS器件的绝缘层,栅极氧化层

用作集成电路中的隔离介质和绝缘介质。

作为集成电路中的电容器介质。

对器件表面起保护钝化作用。因半导体表面态对器 件的影响非常大,采用氧化层保护可防止环境对器 件的污染。

第一章集成电路的基本制造工艺ppt课件

➢ 由于SOC(系统芯片)的出现,给IC设计者提出了 更高的要求,也面临着新的挑战:设计者不仅要懂系 统、电路,也要懂工艺、制造。

经营者提供商品或者服务有欺诈行为 的,应 当按照 消费者 的要求 增加赔 偿其受 到的损 失,增 加赔偿 的金额 为消费 者购买 商品的 价款或 接受服 务的费 用

半导体材料:硅

扩散

➢ 替位式扩散:杂质离子占据硅原子的位:

Ⅲ、Ⅴ族元素

一般要在很高的温度(950~1280℃)下进行 磷、硼、砷等在二氧化硅层中的扩散系数

均远小于在硅中的扩散系数,可以利用氧 化层作为杂质扩散的掩蔽层。

➢ 间隙式扩散:杂质离子位于晶格间隙:

Na、K、Fe、Cu、Au 等元素 扩散系数要比替位式扩散大6~7个数量级

2(Dt) 2

其中,NT:预淀积后硅片表面浅层的P原子浓度

N T311 0 5 (1cm )

D:P的扩散系数 t :扩散时间 x:扩散深度

只要控制NT 、T、t 三个因素就可以决定扩散深度及浓度。

经营者提供商品或者服务有欺诈行为 的,应 当按照 消费者 的要求 增加赔 偿其受 到的损 失,增 加赔偿 的金额 为消费 者购买 商品的 价款或 接受服 务的费 用

集成电路芯片的显微照片

经营者提供商品或者服务有欺诈行为 的,应 当按照 消费者 的要求 增加赔 偿其受 到的损 失,增 加赔偿 的金额 为消费 者购买 商品的 价款或 接受服 务的费 用

V ss

p o ly 栅

V dd 布 线 通 道 参考孔

N+

P+

有源区

集成电路的内部单元(俯视图)

经营者提供商品或者服务有欺诈行为 的,应 当按照 消费者 的要求 增加赔 偿其受 到的损 失,增 加赔偿 的金额 为消费 者购买 商品的 价款或 接受服 务的费 用

经营者提供商品或者服务有欺诈行为 的,应 当按照 消费者 的要求 增加赔 偿其受 到的损 失,增 加赔偿 的金额 为消费 者购买 商品的 价款或 接受服 务的费 用

半导体材料:硅

扩散

➢ 替位式扩散:杂质离子占据硅原子的位:

Ⅲ、Ⅴ族元素

一般要在很高的温度(950~1280℃)下进行 磷、硼、砷等在二氧化硅层中的扩散系数

均远小于在硅中的扩散系数,可以利用氧 化层作为杂质扩散的掩蔽层。

➢ 间隙式扩散:杂质离子位于晶格间隙:

Na、K、Fe、Cu、Au 等元素 扩散系数要比替位式扩散大6~7个数量级

2(Dt) 2

其中,NT:预淀积后硅片表面浅层的P原子浓度

N T311 0 5 (1cm )

D:P的扩散系数 t :扩散时间 x:扩散深度

只要控制NT 、T、t 三个因素就可以决定扩散深度及浓度。

经营者提供商品或者服务有欺诈行为 的,应 当按照 消费者 的要求 增加赔 偿其受 到的损 失,增 加赔偿 的金额 为消费 者购买 商品的 价款或 接受服 务的费 用

集成电路芯片的显微照片

经营者提供商品或者服务有欺诈行为 的,应 当按照 消费者 的要求 增加赔 偿其受 到的损 失,增 加赔偿 的金额 为消费 者购买 商品的 价款或 接受服 务的费 用

V ss

p o ly 栅

V dd 布 线 通 道 参考孔

N+

P+

有源区

集成电路的内部单元(俯视图)

经营者提供商品或者服务有欺诈行为 的,应 当按照 消费者 的要求 增加赔 偿其受 到的损 失,增 加赔偿 的金额 为消费 者购买 商品的 价款或 接受服 务的费 用

集成电路工艺制程1PPT课件

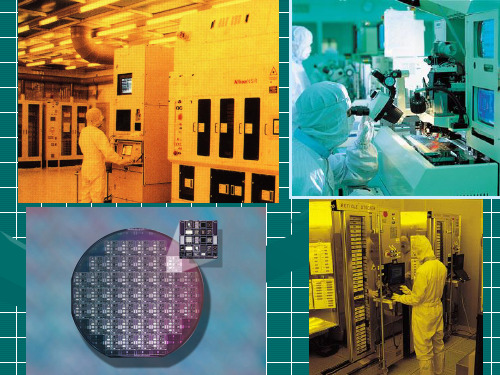

集成电路生产的3个阶段

✓图显示集成电路从晶 圆的 (a)拉晶; (b)制造; (c)切割; (d)封装; 完成的简易流程; ✓图(e)为单一晶粒的 集成电路放大图标

集成电路生产的3个阶段

硅晶片(wafer)的制造

集成电路的制作

集成电路的封装(Package)

习惯以线路制造的最小线宽、晶片直径及DRAM(动态随机存储 器)所储存的容量来评断集成电路的发展状况。

物理气相沉积

电致迁移(Electro migration)

解决:加入适量Cu, 0.5%~4% 为了预防“尖峰”、“电移”,使用含Si与Cu的AL合金做 导线。

阻障C层u缺(点Ba:rr不ie易r L形ay成er挥)发—物Ti,N 不及易Ti蚀W刻。 如图所示,可避免铝—硅界面的尖峰

现象,提升附著能力。

1)增大距离; 2)包好衬底; 或采用Epi substrate, SOL等。

总结:随着IC集成度提高,出现“短沟效应”,引发了“热电子 效应”。采用LDD结构无法解决集成度提高衍生出的能量耗损及 散热问题,因此出现低能耗高集成度的CMOS,而且现已成为 VLSI主要结构,但成本提高,出现双载流子现象所衍生出的latchup问题。

半导体元件的制程

沉积理论

薄膜的沉积,是一连串涉及吸附原子的吸附、吸附原子 在表面的扩散及在适当的位置下聚结,以渐渐形成薄膜 并成长的过程。

半导体元件的制程

分类及详述

物理气相沉积(Physical Vapor Deposition)——PVD

○ 蒸 镀(Evaporation) 利用被蒸镀物在高温(近熔点)时,具备饱和蒸汽压,来沉积薄膜 的过程。 ○ 溅 镀(Sputtering) 利用离子对溅镀物体电极(Electrode)的轰击(Bombardment)使 气相中具有被镀物的粒子(如原子),再来沉积薄膜。

集成电路设计与制造的主要流程ppt

激光扫描阵列:特殊的门阵列设计方法

对于一个特殊结构的门阵列母片,片上晶体管和 逻辑门之间都有电学连接,用专门的激光扫描光 刻设备切断不需要连接处的连线,实现ASIC功能。

只需一步刻铝工艺,加工周期短;

采用激光扫描曝光,省去了常规门阵列方法中的 制版工艺。但制备时间较长。

一般用于小批量(200~2000块)ASIC的制造

版图设计

功能描述与逻辑描述

功能图 逻辑图 电路图 符号式版图 , 版图

举例:x=a’b+ab’;CMOS与非门;CMOS反相器版图

什么是版图?一组相互套合的图形,各层版图相 应于不同的工艺步骤,每一层版图用不同的图案 来表示。

版图与所采用的制备工艺紧密相关

设计流程

理想的设计流程(自顶向下:TOP-DOWN)

元件 门

元胞

宏单元(功能块)

基于单元库的描述:层次描述

单元库可由厂家提供,可由用户自行建立

B. 模拟电路:尚无良好的综合软件

RTL级仿真通过后,根据设计经验进行电路设计

原理图输入

电路模拟与验证

模拟单元库

逻辑和电路设计的输出:网表(元件及其连接关系)或逻

辑图、电路图

软件支持:逻辑综合、逻辑模拟、电路模拟、时序分析等软

设计的基本过程 (举例)

功能设计 逻辑和电路设计 版图设计

集成电路设计的最终输出是掩膜版图,通过制版 和工艺流片可以得到所需的集成电路。 设计与制备之间的接口:版图

主要内容

IC设计特点及设计信息描述 典型设计流程 典型的布图设计方法及可测性设计技术

设计特点和设计信息描述

没有单元库支持:对各单元进行电路设计,通过电

路模拟与分析,预测电路的直流、交流、瞬态等特性, 之后再根据模拟结果反复修改器件参数,直到获得满 意的结果。由此可形成用户自己的单元库

《集成电路制造》课件

详细描述

新材料的应用能够提高集成电路的集成度和运算 速度,同时降低能耗,延长设备的使用寿命。

新设备的应用

总结词

新设备的应用是推动集成电路制造技术进步的重要因素。

总结词

新设备的应用将促进集成电路制造的规模化和精细化。

详细描述

随着光刻、刻蚀等关键设备技术的不断突破,新一代的设 备如EUV光刻机、纳米压印设备等将进一步提高集成电路 的制造精度和效率。

2023-2026

ONE

KEEP VIEW

《集成电路制造》 PPT课件

REPORTING

CATALOGUE

目 录

• 集成电路制造概述 • 集成电路制造材料 • 集成电路制造设备 • 集成电路制造工艺 • 集成电路制造中的问题与对策 • 集成电路制造的未来发展

PART 01

集成电路制造概述

集成电路制造的定义

热处理设备种类

包括快速热处理、退火炉、氧化炉等。

热处理设备的作用

优化材料性能,提高集成电路的稳定性和可 靠性。

光刻设备

光刻设备

用于将设计好的电路图形转移到硅片 表面,是集成电路制造中的关键设备 之一。

光刻设备种类

包括接触式光刻机、接近式光刻机、 投影式光刻机等。

光刻原理

利用光敏材料和光的干涉、衍射等作 用,将电路图形从掩膜版转移到硅片 表面。

效益。

PART 06

集成电路制造的未来发展

新材料的应用

总结词

新材料的应用是集成电路制造未来发展的关键之 一。

总结词

新材料的应用有助于提高集成电路的性能和降低 能耗。

详细描述

随着科技的不断发展,新型半导体材料如碳纳米 管、二维材料等逐渐崭露头角,它们具有更高的 电子迁移率、更强的耐热性等特点,为集成电路 制造带来了新的可能性。

新材料的应用能够提高集成电路的集成度和运算 速度,同时降低能耗,延长设备的使用寿命。

新设备的应用

总结词

新设备的应用是推动集成电路制造技术进步的重要因素。

总结词

新设备的应用将促进集成电路制造的规模化和精细化。

详细描述

随着光刻、刻蚀等关键设备技术的不断突破,新一代的设 备如EUV光刻机、纳米压印设备等将进一步提高集成电路 的制造精度和效率。

2023-2026

ONE

KEEP VIEW

《集成电路制造》 PPT课件

REPORTING

CATALOGUE

目 录

• 集成电路制造概述 • 集成电路制造材料 • 集成电路制造设备 • 集成电路制造工艺 • 集成电路制造中的问题与对策 • 集成电路制造的未来发展

PART 01

集成电路制造概述

集成电路制造的定义

热处理设备种类

包括快速热处理、退火炉、氧化炉等。

热处理设备的作用

优化材料性能,提高集成电路的稳定性和可 靠性。

光刻设备

光刻设备

用于将设计好的电路图形转移到硅片 表面,是集成电路制造中的关键设备 之一。

光刻设备种类

包括接触式光刻机、接近式光刻机、 投影式光刻机等。

光刻原理

利用光敏材料和光的干涉、衍射等作 用,将电路图形从掩膜版转移到硅片 表面。

效益。

PART 06

集成电路制造的未来发展

新材料的应用

总结词

新材料的应用是集成电路制造未来发展的关键之 一。

总结词

新材料的应用有助于提高集成电路的性能和降低 能耗。

详细描述

随着科技的不断发展,新型半导体材料如碳纳米 管、二维材料等逐渐崭露头角,它们具有更高的 电子迁移率、更强的耐热性等特点,为集成电路 制造带来了新的可能性。