4Bit超前进位加法器门级电路设计与仿真

EDA课程设计报告--四位加法器设计

《EDA》课程设计题目:四位加法器设计学号: 200906024245姓名:梁晓群班级:机自094指导老师:韩晓燕2011年12月28日—2011年12月30日目录摘要----------------------------------3EDA简介---------------------------3概述----------------------------------4 1.1目的与要求-------------------4 1.2实验前预习-------------------41.3设计环境----------------------5四位全加器的设计过程----------52.1 半加器的设计-----------------62.2一位全加器的设计-----------92.3四位全加器的设计----------11收获与心得体会----------------13摘要本文主要介绍了关于EDA技术的基本概念及应用,EDA设计使用的软件Quartus7.2的基本操作及使用方法,以及半加器、1位全加器和四位全加器的设计及仿真过程。

EDA简介EDA的概念EDA技术就是以计算机为工具,设计者在EDA软件平台上,用硬件描述语言HDL完成设计文件,然后由计算机自动地完成逻辑编译、化简、分割、综合、优化、布局、布线和仿真,直至对于特定目标芯片的适配编译、逻辑映射和编程下载等工作.EDA是电子设计自动化(Electronic Design Automation)的缩写,在20世纪90年代初从计算机辅助设计(CAD)、计算机辅助制造(CAM)、计算机辅助测试(CAT)和计算机辅助工程(CAE)的概念发展而来的。

EDA代表了当今电子设计技术的最新发展方向,它的基本特征是:设计人员按照“自顶向下”的设计方法,对整个系统进行方案设计和功能划分,系统的关键电路用一片或几片专用集成电路(ASIC)实现,然后采用硬件描述语言(HDL)完成系统行为级设计,最后通过综合器和适配器生成最终的目标器件,这样的设计方法被称为高层次的电子设计方法。

4bits超前加法进位器的全定制设计_微电子卓越班数字集成电路课程设计报告

数字集成电路课程设计题目:4 bits超前加法进位器地全定制设计姓名:席高照学号: 111000833学院:物理与信息工程学院专业:微电子(卓越班)年级: 2010级指导教师:陈群超(签名)2013 年 6 月 3 日目录第1章概述 01.1课程设计目地.......................................... 错误!未定义书签。

1.2课程设计地主要内容.................................... 错误!未定义书签。

1.2.1设计题目.......................................... 错误!未定义书签。

1.2.2设计内容.......................................... 错误!未定义书签。

第2章功能分析及逻辑分析 (2)2.1功能分析 (2)2.2推荐工作条件 (3)2.3电性能 (7)2.4真值表 ................................................ 错误!未定义书签。

2.5表达式 (6)2.6电路图...................................................................... 错误!未定义书签。

第3章电路设计与器件参数设计83.1性能指标: ............................................ 错误!未定义书签。

3.2模块划分 (7)3.2.1输出级电路设计 (7)3.2.2内部反相器 (9)3.2.3内部电路等效 (8)3.2.4输入级电路 (10)3.2.5输出缓冲级电路 (10)3.2.6输入、输出保护电路 (10)3.3本章小结 (10)第4章电路模拟与仿真................................................................................................... 错误!未定义书签。

实验九新四位全加器的设计

课题:全加器实验【课时安排】2学时【实验要求】1.掌握Max+Plus II的使用流程2.学习并掌握全加器的设计【实验内容】设计四位加法器并进行仿真。

具体要求:一个带进位输入、输出的4位全加器端口:A、B为加数,CIN为进位输入,SUM为加和,COUT为进位输出1.编号1-15单号的同学设计四位超前进位加法器(参考教材P139)2.编号1-15双号的同学参考ALU运算模块的设计(教材P144),使用加法运算符设计3.编号16-29单号的同学用生成语句描述对4位全加法器程序。

(参考教材P89例3-26)4.编号16-29双号的同学用结构体的结构化语句描述二输入的4位全加法器程序(参考教材P89例3-35及P65例3-12)以上设计均需进行仿真,实验完成后提交电子文档(内含对应的VHDL程序及仿真结果的截图),提交实验报告,在实验报告中只需写清楚本次实验的设计原理和设计过程(如1号只写超前进位的实现过程,16号只写生成语句描述对4位全加法器程序的实现过程)。

【实验原理介绍】一、一位全加器1.设计原理加法器是最基本的算术运算单元。

加法器中最基本的单元是全加器。

全加器中有两个输入数据a和b,一个进位输入Ci,一个和输出sum和一个进位输出Cout2.一位全加器的VHDL设计实现根据全加器的工作原理,用VHDL描述源程序如下:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY full_adder ISPORT (a, b, ci: IN STD_LOGIC;sum, cout: OUT STD_LOGIC);END full_adder;ARCHITECTURE rtl OF full_adder ISBEGINsum <= a XOR b XOR ci;cout <= (a AND b) OR (a AND ci ) OR ( b AND ci);END rtl;二、4位串行进位加法器设计【实验重要步骤】略。

BCD-7段译码器、四位超前进位加法器、四位数值比较器

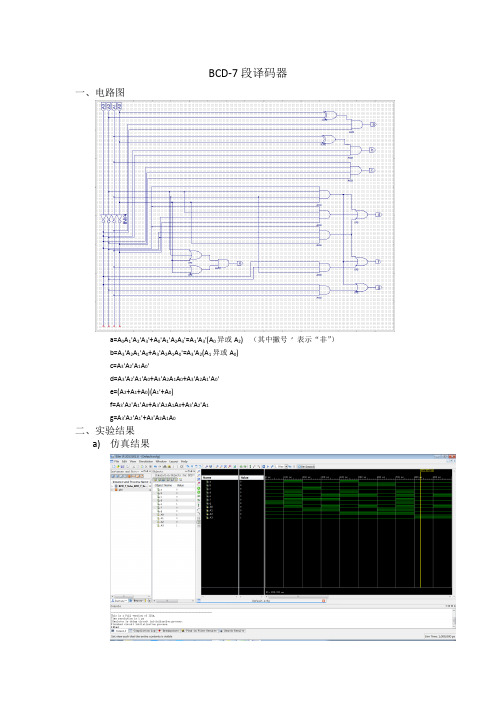

BCD-7段译码器一、电路图a=A0A1'A2'A3'+A0'A1'A2A3'=A1'A3'(A0异或A2) (其中撇号’表示“非”)b=A3'A2A1'A0+A3'A2A1A0'=A3'A2(A1异或A0)c=A3'A2'A1A0'd=A3'A2'A1'A0+A3'A2A1A0+A3'A2A1'A0'e=(A2+A1+A0)(A1'+A0)f=A3'A2'A1'A0+A3'A2A1A0+A3'A2'A1g=A3'A2'A1'+A3'A2A1A0二、实验结果a)仿真结果{A3,A2,A1,A0}取遍0000,0001,0010,0011,0100,0101,0110,0111,1000,1001,结果均符合要求。

b)在实际FPGA中实验结果:符合要求。

三、结果分析a)输入值范围在0000-1001之间时,可以实现BCD码转7段显示码功能。

但在输入值超出范围时将显示乱码。

若不允许乱码出现,可将卡诺图中的不确定性项d全部改为需要的值,以提示输入错误或不显示任何内容。

但这将使电路规模大幅增加。

b)关键路径含3级门。

其中a,b使用了异或门,但异或门的输入均为原变量。

通过异或门的路径最多只需通过2级逻辑门。

若全部改用与门、或门,则必须有反变量输入,使a,b的关键路径仍然含有3级门,因此不能提升速度,但每个函数必需的带宽都将从4增加为8。

如果与门、或门过剩,异或门不足,且带宽不是制造过程中的制约因素,则更适宜使用与门、或门。

由以上可知,使用异或门可以避免反变量输入,节约1级非门的相应时间,节约带宽。

d函数在卡诺图的分布导致其无法很好化简,因此将占用较多带宽。

实验二 加法器的设计与仿真实验报告

实验二加法器的设计与仿真一、实验目的:实现加法器的设计与仿真。

二、实验内容1.用逻辑图和VHDL语言设计全加器;2.利用设计的全加器组成串行加法器;3.用逻辑图和VHDL语言设计并行加法器。

三、实验步骤。

(一)、全加器、串行加法器和并行加法器的逻辑图。

1.全加器:2.串行加法器:3.74283:4位先行进位全加器逻辑框图:逻辑图:(二)、全加器、串行加法器和并行加法器的VHDL。

1.全加器:LIBRARY ieee;USE ieee.std_logic_1164.all;LIBRARY work;ENTITY quanjiaqi ISPORT(X : IN STD_LOGIC;Y : IN STD_LOGIC;CIN : IN STD_LOGIC;S : OUT STD_LOGIC;COUT : OUT STD_LOGIC);END quanjiaqi;ARCHITECTURE bdf_type OF quanjiaqi ISSIGNAL SYNTHESIZED_WIRE_0 : STD_LOGIC;SIGNAL SYNTHESIZED_WIRE_1 : STD_LOGIC;SIGNAL SYNTHESIZED_WIRE_2 : STD_LOGIC;SIGNAL SYNTHESIZED_WIRE_3 : STD_LOGIC;BEGINSYNTHESIZED_WIRE_2 <= Y AND X;SYNTHESIZED_WIRE_1 <= CIN AND Y;SYNTHESIZED_WIRE_3 <= CIN AND X;SYNTHESIZED_WIRE_0 <= X XOR Y;S <= SYNTHESIZED_WIRE_0 XOR CIN;COUT <= SYNTHESIZED_WIRE_1 OR SYNTHESIZED_WIRE_2 OR SYNTHESIZED_WIRE_3; END bdf_type;2.串行加法器:LIBRARY ieee;USE ieee.std_logic_1164.all;LIBRARY work;ENTITY chuanxingjiafaqi ISPORT(x0 : IN STD_LOGIC;y0 : IN STD_LOGIC;cin : IN STD_LOGIC;x1 : IN STD_LOGIC;x2 : IN STD_LOGIC;y2 : IN STD_LOGIC;x3 : IN STD_LOGIC;y3 : IN STD_LOGIC;y1 : IN STD_LOGIC;s0 : OUT STD_LOGIC;s1 : OUT STD_LOGIC;s2 : OUT STD_LOGIC;s3 : OUT STD_LOGIC;cout : OUT STD_LOGIC);END chuanxingjiafaqi;ARCHITECTURE bdf_type OF chuanxingjiafaqi ISCOMPONENT quanjiaqiPORT(X : IN STD_LOGIC;Y : IN STD_LOGIC;CIN : IN STD_LOGIC;S : OUT STD_LOGIC;COUT : OUT STD_LOGIC);END COMPONENT;SIGNAL SYNTHESIZED_WIRE_0 : STD_LOGIC; SIGNAL SYNTHESIZED_WIRE_1 : STD_LOGIC; SIGNAL SYNTHESIZED_WIRE_2 : STD_LOGIC;BEGINb2v_inst : quanjiaqiPORT MAP(X => x0,Y => y0,CIN => cin,S => s0,COUT => SYNTHESIZED_WIRE_0); b2v_inst1 : quanjiaqiPORT MAP(X => x1,Y => y1,CIN => SYNTHESIZED_WIRE_0,S => s1,COUT => SYNTHESIZED_WIRE_1); b2v_inst2 : quanjiaqiPORT MAP(X => x2,Y => y2,CIN => SYNTHESIZED_WIRE_1,S => s2,COUT => SYNTHESIZED_WIRE_2); b2v_inst3 : quanjiaqiPORT MAP(X => x3,Y => y3,CIN => SYNTHESIZED_WIRE_2,S => s3,COUT => cout);END bdf_type;3.74283:4位先行进位全加器LIBRARY ieee;USE ieee.std_logic_1164.all;LIBRARY work;ENTITY 74283_0 ISPORT(CIN : IN STD_LOGIC;A1 : IN STD_LOGIC;A2 : IN STD_LOGIC;B2 : IN STD_LOGIC;A3 : IN STD_LOGIC;A4 : IN STD_LOGIC;B4 : IN STD_LOGIC;B1 : IN STD_LOGIC;B3 : IN STD_LOGIC;SUM4 : OUT STD_LOGIC;COUT : OUT STD_LOGIC;SUM1 : OUT STD_LOGIC;SUM2 : OUT STD_LOGIC;SUM3 : OUT STD_LOGIC );END 74283_0;ARCHITECTURE bdf_type OF 74283_0 IS BEGIN-- instantiate macrofunctionb2v_inst : 74283PORT MAP(CIN => CIN,A1 => A1,A2 => A2,B2 => B2,A3 => A3,A4 => A4,B4 => B4,B1 => B1,B3 => B3,SUM4 => SUM4,COUT => COUT,SUM1 => SUM1,SUM2 => SUM2,SUM3 => SUM3);END bdf_type;四、实验仿真结果。

4bits超前加法进位器的全定制设计微电子卓越班数字集成电路课程设计报告

数字集成电路课程设计题目:4 bits超前加法进位器的全定制设计姓名:席高照学号:111000833学院:物理与信息工程学院专业:微电子(卓越班)年级:2010级指导教师:群超(签名)2013 年 6 月 3 日目录第1章概述 (1)1.1课程设计目的 (1)1.2课程设计的主要容 (1)1.2.1设计题目 (1)1.2.2设计容 (1)第2章功能分析及逻辑分析 (2)2.1功能分析 (2)2.2推荐工作条件 (3)2.3电性能 (3)2.4真值表 (6)2.5表达式 (6)2.6电路图 (7)第3章电路设计与器件参数设计 (8)3.1性能指标: (8)3.2模块划分 (8)3.2.1输出级电路设计 (8)3.2.2部反相器 (9)3.2.3部电路等效 (9)3.2.4输入级电路 (10)3.2.5输出缓冲级电路 (10)3.2.6输入、输出保护电路 (10)3.3本章小结 (11)第4章电路模拟与仿真 (12)4.1电路搭建 (12)4.1.1建立新库 (12)4.1.2建立SCHEMATIC VIEW (13)4.1.3建立SYMBOL (14)4.1.4建立总体电路SCHEMATIC VIEW (14)4.1.5建立总体SYMBOL (15)4.1.6测试电路 (16)4.2功能仿真 (16)4.3功耗仿真 (18)4.4仿真结果分析 (18)4.5本章小结 (18)5.2反相器版图 (19)5.3输入级 (20)5.4输出级 (20)5.5输出缓冲 (20)5.6异或门 (21)5.7或非门 (23)5.8与非门 (24)5.9整体版图 (25)5.10本章小结 (25)心得 (26)参考文献 (27)附录 (28)附录174LS283中文资料 (28)第1章概述1.1 课程设计目的•综合应用已掌握的知识•熟悉集成电路设计流程•熟悉集成电路设计主流工具•强化学生的实际动手能力•培养学生的工程意识和系统观念•培养学生的团队协作能力1.2 课程设计的主要容1.2.1 设计题目4bits超前进位加法器全定制设计1.2.2 设计要求Vdd=1.8V,VoH=4.6V,Vol=0.4V可驱动10个LSTTL电路(相对于15pf电容负载)1.2.3 设计容•功能分析及逻辑分析•电路设计及器件参数设计•估算功耗与延时•电路模拟与仿真•版图设计•版图数据提交及考核,课程设计总结第2章功能分析及逻辑分析2.1功能分析74283为4为超前进位加法器,不同于普通串行进位加法器由低到高逐级进位,超前进位加法器所有位数的进位大多数情况下同时产生,运算速度快,电路结构复杂。

4bits超前进位加法器全定制设计实验报告

TPLH

Propagation Delay Time

A1~A4,B1~B4到C4

3

ns

TPHL

3

tT

2.5

tP

2.5

Av Power

4

Layout Area

150*180

2.5真值表

2.6逻辑图

工艺的主要参数(smic18工艺)

参数

参数定义

PMOS数值

NMOS数值

U0

迁移率

8.661m

34m

Vth

-0.4

mA

IOL

Low Level OutputVoltage

8

mA

2.3直流特性

Symbol

Parameter

Test Condition

Value

Units

TA=25°C

Min

Typ

Max

VOH

High Level OutputVoltage

VCC=Min,IOH=Max

VIL=Max,VIH=Min

mA

C0

-0.4

II

InputCurrent @ Max Input Voltage

VCC=Max

VI=7.2V

A,B

0.2

mA

C0

0.1

ICC

Supply Current

VCC=Maxl

Parameter

From (Input )to (Ouput)

Test Condition

(2)点选LM视窗上面的工具列File→New→Library;

(3)会产生New Library画面;

(4)在框内填入库名;

四位加法器

四位加法器一、实验要求掌握组合逻辑电路的基本分析和设计方法;理解半加器和全加器的工作原理,用硬件描述语言实现半加器和全加器的门级设计,并使用自己设计的半加器组件构建全加器;学会利用软件仿真和远程实验系统实现对数字电路的逻辑功能进行验证和分析。

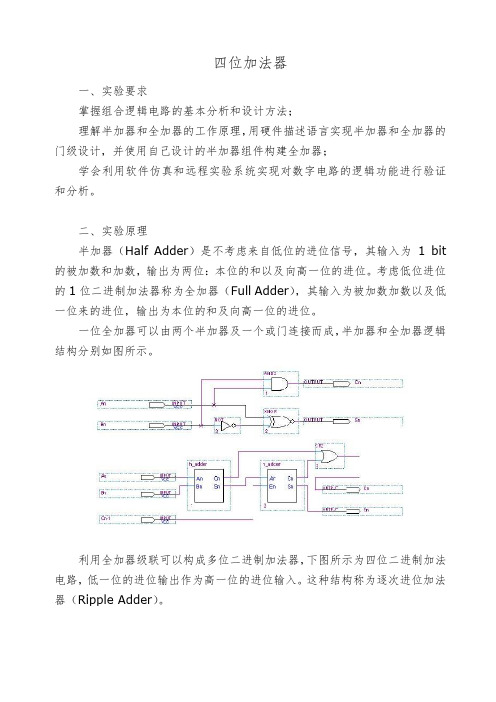

二、实验原理半加器(Half Adder)是不考虑来自低位的进位信号,其输入为 1 bit 的被加数和加数,输出为两位:本位的和以及向高一位的进位。

考虑低位进位的1位二进制加法器称为全加器(Full Adder),其输入为被加数加数以及低一位来的进位,输出为本位的和及向高一位的进位。

一位全加器可以由两个半加器及一个或门连接而成,半加器和全加器逻辑结构分别如图所示。

利用全加器级联可以构成多位二进制加法器,下图所示为四位二进制加法电路,低一位的进位输出作为高一位的进位输入。

这种结构称为逐次进位加法器(Ripple Adder)。

由于逐次进位加法器的进位信号是在各级间逐级传递的,所以高位的输出必须等低位的进位输入稳定后才有效,这就使得逐次进位加法器的延时比较大,速度比较慢。

为了提高加法器的运算速度,需要对加法器的结构进行改进。

引入进位传递信号和进位产生信号的概念,有{P n=A n⊕B n G n=A n B n利用这两个信号,可以把和信号与进位输出信号表示为{S n=P n⊕C n−1 C n=P n C n−1+G n根据上面给出的进位输出表达式,可得C0=G0+ P0C−1C1=G1+ P1C0=G1+ P1G0+P1P0C−1C2=G2+ P2C1=G2+ P2G1+P2P1G0+ P2P1P0C−1C3=G3+ P3C2=G3+ P3G2+P3P2G1+ P3P2P1G0+ P3P2P1P0C−1由于各级的进位传递信号和进位产生信号是同时生成的,所以各级的进位输出信号不再需要等待低一位的进位输入信号,从而大大减小了整个电路的延时,提高的加法器的运算速度。