[学位论文]高速数据采集与存储系统的设计与实现

高速数据采集系统设计论文论文

毕目录第一章绪论 (3)1.1发展前景及研究意义 (3)第二章系统硬件设计 (4)2.1系统设计原理框图 (4)2.2设计基本思想 (5)2.3.1AT89C51简介 (5)2.3.2FIFO存储器件IDT72V2113简介 (8)2.3.3FPGA芯片简介 (11)2.3.4AD转换芯片TLC5510的简介 (13)2.3.5串口RS232的简介 (17)第三章系统设计原理及工作原理 (16)3.1AD转换工作原理 (17)3.2关于FPGA的简介 (18)3.2.1FPGA的概述 (18)3.3FPGA实现硬件采样的原理 (19)3.4显示电路的工作原理 (20)3.4.1七段显示器的原理 (20)3.4.2静态显示接口 (22)第四章数据采集软件设计 (23)4.1数据处理 (24)第五章结束语 (25)第六章附录 (26)6.1系统设计总体流程图 (26)6.2系统设计程序 (28)6.3系统总体电路图 (29)6.4参考文献: (30)第一章绪论1.1发展前景及研究意义现代工业生产和科学研究对数据采集的要求日益提高。

计算机技术的发展为现代大工业的发展提供了硬件保障。

工业应用系统对作为控制的计算机也提出了新的要求。

一方面要求主控机处理的数据更多,速度也更快;另一方面由于应用系统复杂程度不断提高,控制单元种类很多,速度有快有慢,要求主控机有较强的适应性。

总线技术的发展为各种系统的设计提供了很大方便,提高了系统运行的速度,用户可以进行各种组合。

PC机总线通常联接到PC微机的扩展槽再经插槽为外设提供I/O通道,速度和可靠性都很高。

主机板通过扩展槽这种开放式的总线体系与各种外围设备进行信息交换。

IBM的16位工业标准ISA总线是在工业生产中广为使用的工控机系统总线,这种总线的技术已经很成熟并被广泛采用。

目前不同性能指标的通用或专用的数据采集系统,在各种领域中随处可见。

但是,由于成本或技术开发等众多因素的影响,一般的数据采集系统其速度和通道数不能满足一些特殊领域的测试要求,或者满足这些要求的系统又由于成本相当高而市场推广的难度加大。

基于FPGA的高速数据采集系统的设计与实现

基于FPGA的高速数据采集系统的设计与实现近年来,随着科技的飞速发展,数据采集技术也得到了越来越广泛的应用。

作为物联网和智能化工业的重要组成部分,高速数据采集系统的研发也越来越受到人们的关注。

而基于FPGA的高速数据采集系统,以其可编程性、高速性、低功耗等优点,成为当前数据采集系统的研究热点之一。

一、基于FPGA的高速数据采集系统的原理FPGA(Field Programmable Gate Array)是一种可编程逻辑芯片,它可以通过用户的编程实现各种数字逻辑电路的功能。

在高速数据采集系统中,FPGA可以实现数据的缓存、预处理、调节和处理等功能。

基于FPGA的高速数据采集系统,由硬件和软件两部分组成,其中硬件部分主要指FPGA芯片和外部控制电路,而软件部分则主要指FPGA编程和数据采集软件。

在这个系统中,数据采集器会将采集到的原始数据传输到FPGA中进行处理。

FPGA通过可编程的逻辑电路将原始数据缓存、预处理和调整,并将处理结果传输到接口电路中,最终形成符合要求的数字信号输出。

这些数字信号经过AD转换器转化为模拟信号,再通过后级电路处理后送往计算机或其他设备,实现数据的转化和处理。

二、基于FPGA的高速数据采集系统的设计与实现1、硬件设计在基于FPGA的高速数据采集系统中,硬件设计主要包括模拟电路设计、数字电路设计、数据采集和数据传输电路设计等多个方面。

其中模拟电路的设计主要涉及信号放大、滤波、匹配等问题,目的是将多种模拟信号转化为数字信号,并保证信号的稳定性和准确性。

数字电路的设计则主要包括时钟、计数器、寄存器等部分。

时钟电路主要起到同步采样的作用,使采集数据达到稳定和准确的效果,计数器和寄存器则主要用于处理采集到的数据。

数据采集电路和数据传输电路是整个系统的核心。

数据采集电路负责将采集到的原始数据传输到FPGA中,并通过预处理模块对数据进行处理。

而数据传输电路则主要用于传送处理后的数据到后端设备中。

基于CPLD的高速数据采集系统的设计与实现

基于CPLD的高速数据采集系统的设计与实现摘要:高速数据采集系统在信息科学的各个领域中应用越来越广泛,而基于单片机、ARM的数据采集技术已经很成熟,在对速度要求越来越苛刻的当代社会,这些技术已经显得有些力不从心,我们必须开发新的更高速的数据采集系统才能跟上信息产业发展的脚步,而随着可编程逻辑器件这些年来的迅猛发展,它以其极高的集成度,稳定的性能以及高速、易用的特点,在信息科学的各个领域都得到了广泛的应用,本文提出了一种基于CPLD的高速数据采集系统的设计方法。

关键词:基于CPLD;高速数据;采集系统;设计与实现1、前言数据采集技术是数字系统的重要部分,它与传感器技术、信号处理技术、计算机技术一起构成了现代检测技术的基础。

目前数据采集系统已经被广泛的应用。

在很多实际应用中,传统的采集系统已经不能满足采集要求,需要采样速度很高的甚至是超高采集系统。

本文提出了一种基于CPLD的高速数据采集系统的设计方法。

通过CPLD控制数据连续采集、缓冲,然后通过MCU(C8051F430)读取缓存在SRAM中数据,并且通过USB2.0将缓冲区数据转移到硬盘管理卡,由硬盘管理卡将数据存入海量硬盘。

再利用PC机的强大数据处理功能,MicrosoftVisualC++6.0的MFC类库,设计出一套集数据采集、处理和分析的高速数据采集的可视化系统。

2、系统结构设计本文设计的高速数据采集系统主要由数据采集、数据显示处理和数据传输接口三部分组成。

数据采集系统要解决的问题主要是数据的采集和传输问题。

为了增强设计的灵活性和可扩展性,系统采用CPLD来实现对AD转换器、数据缓存器SRAM、时钟、数据传输的控制逻辑。

系统功能框图如图1。

图1如上图所示,数据采集方案采用的是:带USB2.0控制器的高速单片机+USB传输的方式,目前有一款非常好的自带USB2.0控制器,并且具有51内核的高效率单片机C8051F340,这款单片机的执行速度可达到25MHz,且不用分频,故选用它可高速传输数据到PC机的同时,还可以对RAM进行读取控制。

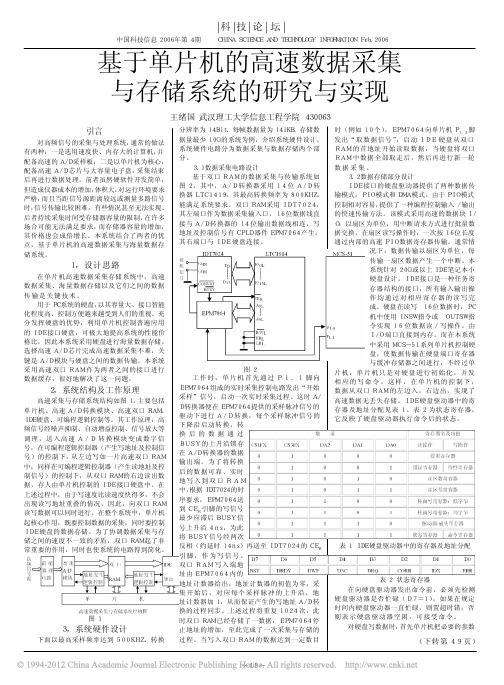

基于单片机的高速数据采集与存储系统的研究与实现

中国科技信息2006年第4期 CHINA SCIENCE AND TECHNOLOGY INFORMATION Feb.2006引言对高频信号的采集与处理系统,通常的做法有两种:一是选用速度快、内存大的计算机,并配备高速的A/D采样板;二是以单片机为核心,配备高速A/D芯片与大容量电子盘,采集结束后再进行数据处理。

前者虽然硬软件开发简单,但造成仪器成本的增加,体积大,对运行环境要求严格,而且当距信号源距离较远或测量多路信号时,信号传输比较困难,有些情况甚至无法实现。

后者持续采集时间受存储器容量的限制,在许多场合可能无法满足要求,而存储器容量的增加,其价格也会成倍增长。

本系统结合了两者的优点,基于单片机的高速数据采集与海量数据存储系统。

1,设计思路在单片机高速数据采集存储系统中,高速数据采集、海量数据存储以及它们之间的数据传输是关键技术。

用于PC系统的硬盘,以其容量大、接口智能化程度高、控制方便越来越受到人们的重视。

充分发挥硬盘的优势,利用单片机控制普遍应用的IDE接口硬盘,可极大地提高系统的性能价格比,因此本系统采用硬盘进行海量数据存储。

选择高速A/D芯片完成高速数据采集不难,关键是A/D模块与硬盘之间的数据传输。

本系统采用高速双口RAM作为两者之间的接口进行数据缓存,很好地解决了这一问题。

2,系统结构及工作原理高速采集与存储系统结构如图1,主要包括单片机、高速A/D转换模块、高速双口RAM、IDE硬盘、可编程逻辑控制等。

其工作原理:高频信号经噪声抑制、自动增益控制、信号放大等调理,送入高速A/D转换模块变成数字信号,在可编程逻辑控制器(产生写地址及控制信号)的控制下,从左边写如一片高速双口RAM中,同样在可编程逻辑控制器(产生读地址及控制信号)的控制下,从双口RAM的右边读出数据,存人由单片机控制的IDE接口硬盘中。

在上述过程中,由于写速度比读速度快得多,不会出现读写地址重叠的情况,因此,向双口RAM读写数据可以同时进行。

高速数据存储系统的设计与应用

华中科技大学硕士学位论文高速数据存储系统的设计与应用姓名:黄寅申请学位级别:硕士专业:通信与信息系统指导教师:马洪20090501华中科技大学硕士学位论文摘要在现代雷达、无线电通信、遥测遥感等各个领域,需要处理各种大量、高速、实时性强的数据。

因此,数据采集和存储技术是数字信号处理系统中非常重要的运用,目前以高性能FPGA为控制核心,结合大容量SDRAM存储器的数字系统成为研究的热点。

本文以Xilinx公司的Virtex_4 FPGA为处理平台,1Gbit DDR SDRAM为存储介质,USB控制器实现数据传输,进行高速大容量存储系统的设计,为完成复杂信号处理算法的实现提供了可靠的支持。

在对DDR SDRAM存储结构、控制原理、接口时序进行深入理解的基础上,利用开源化的IP核实现DDR控制器,通过对控制器进行模块划分与仿真验证,确定了控制器逻辑功能的正确性。

在实现DDR控制器的基础上,进一步确立了高速数据存储系统的设计要求与模块组成,提出了基于FIFO 的高速数据缓存方案和利于性能优化的系统测试方案。

通过ISE 10.1开发平台和Verilog HDL设计输入方式,对每个模块进行了详细的逻辑设计和分析说明,并借助ModelSim仿真工具完成了各模块以及整个系统的功能仿真和验证,达到设计要求。

最后利用实际硬件环境对所设计的系统进行测试,通过系统资源分析,系统实时性分析和实际运行结果分析,证明了所设计的高速大容量数据存储系统符合应用需求,可进一步应用于信号处理算法的实现过程中。

论文的最后在基于复杂信号处理算法实现的应用上,对算法中涉及的数据传输和关键的运算处理进行需求分析,提出了对两种存储器资源的分配与调度策略,完成了可行性论证。

关键词:数据存储,FPGA,DDR SDRAM,FIFO,信号处理华中科技大学硕士学位论文AbstractIn the fields of radar, radio communications, remote sensing, etc. It is necessary to process mass, high speed and real-time data. So the technology of data acquisition and data storage is very important in the digital signal processing system. It is popular to use high-performance FPGA (Field Programmable Gate Array) which acts as the control core, and mass storage SDRAM (Synchronous Dynamic Random Access Memory) to design the digital system.This dissertation utilized Xilinx's Virtex_4 FPGA as the platform and 1Gbit DDR(Double Data Rate) SDRAM as the storage medium, through USB controller implementing data transmission to design the high-speed mass data storage system, and the design provide a basis for the implementation of complex signal processing algorithms. After a deeply research on the structure, principle and interface timing of DDR SDRAM, the DDR controller are designed out by means of IP core. What's more, the function of the controller is proved by the simulation. Based on the implementation of DDR controller, the design requirements and modules makeup of the high-speed mass data storage system are made certain, and the dissertation bring out two schemes, one is to storage data using FIFO(First In First Out), the other is to optimize the performance through system test bench. Through the development platform of ISE 10.1 and language using Verilog HDL, the logic design of every module is accomplished, and the performance of the system is simulated and tested by simulation tool software ModelSim. At last, it is proved that the design of high-speed mass data storage system is valid and feasible by the hardware system operation, and it meets the needs of application.At the end of the dissertation, based on implementation of the complex signal processing algorithms, this paper brings forward the strategy about distribution and schedule of the two memories, as well as fulfills the feasibility study.Keywords: Data storage, FPGA, DDR SDRAM, FIFO, Signal processing独创性声明本人声明所呈交的学位论文是我个人在导师指导下进行的研究工作及取得的研究成果。

实时高速数据采集与存储系统的一种实现方法

冲区的数据存入 SCSI 硬盘; 当数据采集线程把数据写 入第二缓冲区时, 数据存储线程把第一缓冲区的数据 存入 SCSI 硬盘; 如 此循环。另外 通过实际实 验测试 Adaptec19160 Ultra160- SCSI 硬盘控制器, 配合希捷公 司出品的 ST3146707LC SCSI 硬盘, 持续写入速率能达 到 80Mbytes/sec。远大于 45 Mbytes/sec 的采集速率。所 以当数据采集线程写满其中一个缓冲区之前, 数据存 储线程已 经把另一个 缓冲区里的 数据存储入 SCSI 硬 盘。所以这种方法能保证数据的实时 性、完整性和 连 续性。其程序流程图如图 1。

新

在搭建硬件平台的过程中有些问题是必须注意

的, 否则系统不能正常工作。首先, PCI- 7300A_RevB

卡虽然采用分散/聚拢方式的 DMA, 但它对 CPU 资源

的占用率是非常高的。经过实验证明, 要保证整个数

据采集与存储系统正常工作, 只能使用奔四 1.7G 以上

的计算机系统。其次, Windows 系统允许多个设备共享

3.2 板卡驱动设置及注意的问题 对板卡驱动的深刻理解是编写好数据采集于存

技 储程序的前提。在连续数据输入模式下, 板卡驱动程 术 序需要在系统内存里开辟一块缓冲区做为二级缓存,

用户可以设置该缓冲区的大小 。方法是: 从菜单开始/

创 程序/PCI- DASK/NuDAQ PCI configuration Utility 打开 DASK2000 Device Driver Configuration 对话框, 从 Card

//开 辟 块 缓 冲 区 。 FILE *fp; //存储数据的目录。 UINT SampleThreadProc (LPVOID pParam) {BOOLEAN HalfReady=0;//缓冲被写满标志 do {HalfReady=0; do (DI_AsyncMultiBufferNextReady (card,&Half- Ready,&viewidx))://等待驱动程序报告缓

高速数据采集与存储系统的设计及实现

翅片,实现较好的散热效果。综合重量等因素考虑,当翅片 在重要区域布置间距为 5mm,非重要区域不布翅片时,方案 为最佳方案,模型和模块温度分布满足设计要求。

参考文献

[1] 李波 , 李科群 , 俞丹海 .Flotherm 软件在电子设备热 设计中的应用 [J]. 电子机械工程 ,2008(3):11-13. [2] 夏显忠 , 陶光勇 , 夏利锋 . 基于 CFD 的 FLOTHERM 在 机载液晶显示器热分析的应用 [J]. 电子机械工程 ,2007(3):7-10. [3] 李明东 . 利用 CFD 数值仿真技术确定电子设备风道 特性 [J]. 安全与电磁兼容 ,2003(3):16-18.

2016 年第 5 期

信息与电脑 China Computer&Communication

软件开发与应用

高速数据采集与存储系统的设计及实现

向 琛 陈翠云

(中国兵器装备集团 ( 成都 ) 火控技术中心,四川 成都 611731)

摘 要:随着信息技术的不断发展,促使数据采集系统在人们日常生产和生活中的应用越来越广泛。在实际工作当中, 有效利用数据采集系统可以采集、监控并记录生产现场的工艺参数信息,进而起到降低企业实际生产成本与全面提高产 品质量的作用,从而为开展具体工作提供重要数据参照。笔者首先对数据采集技术的基本情况进行了介绍,再对数据采 集单元电路的设计进行了阐述与分析,最后对如何设计存储系统的 FPGA 程序进行了探索与研究,以期能够提高该系统实 际应用效率。 关键词:数据采集;存储系统;设计;实现 中图分类号:TP274.2 文献标识码:A 文章编号:1003-9767(2016)05-085-02

采取高速数据采集与存储系统可以在实际科研工作中获 取到海量的有效信息,因此,其是研究瞬间物理的重要工具。 高速数据采集与存储系统当前主要应用在气象预报、预测地 震等领域,而且现场信号还具有一些较为突出的特点,如运 算量较大、实时性较强等。因此,受到相关工作人员的高度 重视 。

高速数据采集与实时处理系统的设计与实现

高速数据采集与实时处理系统的设计与实现随着科技不断发展,数据在我们生活中的地位越来越重要。

特别是在工业自动化领域中,高速数据采集和实时处理系统的需求越来越大。

本文将介绍高速数据采集与实时处理系统的设计与实现。

本文主要包括以下几个方面:1. 高速数据采集系统的设计与实现2. 实时数据处理系统的设计与实现3. 系统的测试和性能优化1. 高速数据采集系统的设计与实现高速数据采集是指突破常用采集速度,进行数据采集和传输的一种技术。

在工业自动化控制中,电子元器件的响应速度非常快,因此需要实时采集数据才能更好地对工控设备进行控制和实现数据分析。

以下是高速数据采集系统的设计和实现步骤:1.1 选型硬件和软件首先需要选定采集设备和软件。

在选定硬件时需考虑采集速度、采集量、输入接口以及多通道采集等因素。

对于实时控制系统,应选用高速、稳定且可靠的硬件设备。

软件方面,根据硬件的选择,选用适当的驱动程序。

1.2 电路设计由于需要保证采集器的稳定性和可靠性,因此电路设计十分重要。

在设计电路时,需要特别注意信号放大放大电路的设计和噪声干扰的屏蔽。

在信号传输过程中,信号放大电路应具有高增益,同时应能有效地屏蔽来自外部线路的噪声干扰。

1.3 布线设计由于布线和绝缘的设计将直接影响采集数据的稳定性和准确性,因此需要采用专业的设计技术和规范,确保系统数据的稳定。

1.4 系统调试系统调试是整个设计过程中最重要的环节之一。

在进行系统调试时,应逐一对硬件设备和软件进行测试和校准。

检查系统的分辨率是否满足要求,数据采集是否准确和稳定,软件编程是否准确等等。

只有经过严格的测试和校准,才能确保实时数据采集的准确性和稳定性。

2. 实时数据处理系统的设计与实现2.1 数据处理系统的选择在设计实时数据处理系统时,选择合适的数据处理系统非常重要。

根据实际需要,选择处理器和软件。

处理器的性能要足够强大,以处理高速实时数据。

软件也要适应处理器,为系统提供有效、快速和准确的数据处理。