高速ADC DAC测试原理及测试方法

高速ADC和DAC测试方案 (2)

PG

16800/900 Logic Analyzer

N bits data (Digital in)

DA Converter

Analog SignБайду номын сангаасl

DMM MXA/PSA

LAN

Agilent VEE

GP-IB PC(GP-IB)

安捷伦高速ADC和DAC测试解决方案 ---高速DAC分析软件

来自AEO的高速DAC分析软件

来自日本的 高速ADC自动测试软件

安捷伦高速ADC和DAC测试解决方案 ---高速DAC测试方案

方案配置:

81130A

1.81130A 81131A 2.16800/900 具有码型发生器 3.万用表 4. 频谱分析仪 5.分析软件 或自动测试软件

Sampling Clock Sampling Clock ( For DUT DAC)

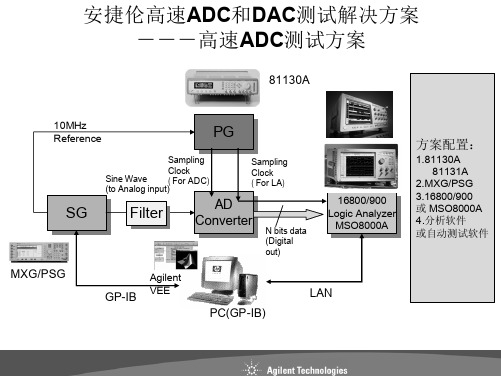

安捷伦高速ADC和DAC测试解决方案 ---高速ADC测试方案

81130A

10MHz Reference

Sampling Clock Sine Wave ( For ADC) (to Analog input)

PG

Sampling Clock ( For LA)

方案配置:

1.81130A 81131A 2.MXG/PSG 3.16800/900 或 MSO8000A 4.分析软件 或自动测试软件

SG

Filter

AD Converter

N bits data (Digital out)

16800/900 Logic Analyzer MSO8000A

MXG/PSG GP-IB

Agilent VEE

LAN PC(GP-IB)

高速ADC、DAC测试原理及测试方法

高速ADC/DAC测试原理及测试方法随着数字信号处理技术和数字电路工作速度的提高,以及对于系统灵敏度等要求的不断提高,对于高速、高精度的ADC、DAC的指标都提出了很高的要求。

比如在移动通信、图像采集等应用领域中,一方面要求ADC有比较高的采样率以采集高带宽的输入信号,另一方面又要有比较高的位数以分辨细微的变化。

因此,保证ADC/DAC在高速采样情况下的精度是一个很关键的问题。

ADC/DAC芯片的性能测试是由芯片生产厂家完成的,需要借助昂贵的半导体测试仪器,但是对于板级和系统级的设计人员来说,更重要的是如何验证芯片在板级或系统级应用上的真正性能指标。

一、ADC的主要参数ADC的主要指标分为静态指标和动态指标2大类。

静态指标主要有:•Differential Non-Linearity (DNL)•Integral Non-Linearity (INL)•Offset Error•Full Scale Gain Error动态指标主要有:•Total harmonic distortion (THD)•Signal-to-noise plus distortion (SINAD)•Effective Number of Bits (ENOB)•Signal-to-noise ratio (SNR)•Spurious free dynamic range (SFDR)二、ADC的测试方案要进行ADC这些众多指标的验证,基本的方法是给ADC的输入端输入一个理想的信号,然后对ADC转换以后的数据进行采集和分析,因此,ADC的性能测试需要多台仪器的配合并用软件对测试结果进行分析。

下图是一个典型的ADC测试方案:如图所示,由Agilent 的ESG 或PSG 做为信号源产生高精度、高纯净度的正弦波信号送给被测的ADC 做为基准信号,ADC 会在采样时钟的控制下对这个正弦波进行采样,变换后的结果用逻辑分析仪采集下来。

DAC与ADC测试实验报告

本科实验报告实验名称:DAC与ADC测试实验一、实验目的1、掌据ADC和DAC在软件无线电设计中的作用。

2、学习DAC驱动和ADC采样程序的设计方法。

二、实验原理ADC采样利用AD9430芯片完成。

通过FPGA给ADC提供一个采样时钟 ADC_CLK,则ADC会输出该采样率的采样数据,包括2路数据(ADC_IN1 与ADC IN2) 和一个随路时钟信号(ADC_DCO),每路数据的速率为采样率的一半。

FPGA在ADC_DCO为1时,采样ADC_IN1,为0时采样ADC_IN2,得到1路合并后的采样数据。

在ADC的模拟输入端输入个单载波信号,在FPGA内通过Chipscope观察采样得到的数字信号波形,分析其波形与频率是否与输入信号一致。

DAC驱动利用AD9755芯片完成。

首先在FPGA内生成一个数字单载波信号,再输出给DAC芯片完成数模转换,通过示波器测量输出模拟信号的波形和频率,分析DAC驱动是否正常。

在FPGA内生成数字单载波信号时采用查表法来实现,通过相位累加器在每个时钟周期累加一次频率字,用相位累加器的高位作为地址去查正弦表,即可得到数字单载波信号。

由频率字f w和采样率f s可以计算得到输出的频率f0值∗f sf0=f w232AD9755芯片的采样率为所给采样时钟的2倍,因此一方面通过 FPGA给DAC 提供一个采样时钟DAC_CLK,另一方面需要给DAC提供2路速率都为采样时钟的数据(DAC_OUT1和DAC_OUT2).相位紧加器年个时钟周期累加f w,,而通过井行2路分支相位累加器,计算得到每个支路的相位值,再由该相位值去查每个支路的正弦表,得到2路正弦数字信号。

三、实验仪器和材料1、基于FPGA的软件无线电平台;2、FPGA下载线;3、射频电缆;4、20MHz双踪示波器;5、台式计算机。

四、实验步骤1、检查板子上有无异物或短路现象,正常后,将电源插上,板子上电源指示灯应亮;2、利用ISE新建一个工程,用VDHL语言编写DAC驱动程序,生成一个正弦波输出,正弦波的频率为12.5MHz,系统工作时钟频率为1001MHz,DAC采样率为时钟的2倍,即200MHz。

【高速中频采样和数字下变频的研究】第七章高速高精度ADC的测试结果

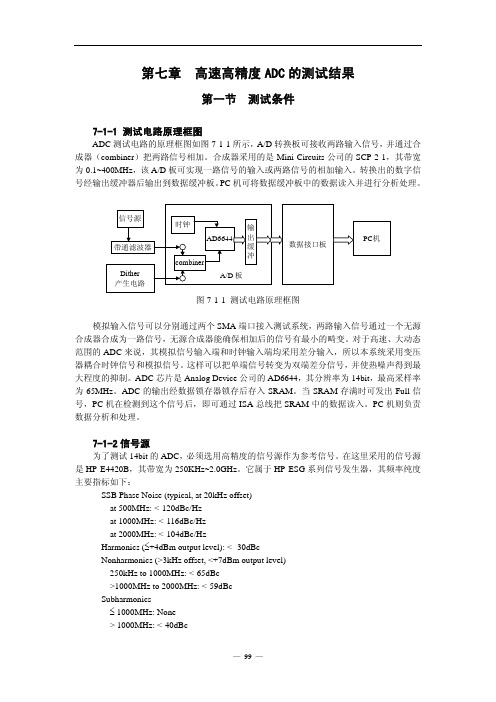

第七章 高速高精度ADC的测试结果第一节测试条件7-1-1 测试电路原理框图ADC测试电路的原理框图如图7-1-1所示,A/D转换板可接收两路输入信号,并通过合成器(combiner)把两路信号相加。

合成器采用的是Mini-Circuits公司的SCP-2-1,其带宽为0.1~400MHz,该A/D板可实现一路信号的输入或两路信号的相加输入。

转换出的数字信号经输出缓冲器后输出到数据缓冲板。

PC机可将数据缓冲板中的数据读入并进行分析处理。

图7-1-1 测试电路原理框图模拟输入信号可以分别通过两个SMA端口接入测试系统,两路输入信号通过一个无源合成器合成为一路信号,无源合成器能确保相加后的信号有最小的畸变。

对于高速、大动态范围的ADC来说,其模拟信号输入端和时钟输入端均采用差分输入,所以本系统采用变压器耦合时钟信号和模拟信号。

这样可以把单端信号转变为双端差分信号,并使热噪声得到最大程度的抑制。

ADC芯片是Analog Device公司的AD6644,其分辨率为14bit,最高采样率为65MHz。

ADC的输出经数据锁存器锁存后存入SRAM。

当SRAM存满时可发出Full信号,PC机在检测到这个信号后,即可通过ISA总线把SRAM中的数据读入。

PC机则负责数据分析和处理。

7-1-2信号源为了测试14bit的ADC,必须选用高精度的信号源作为参考信号。

在这里采用的信号源是HP E4420B,其带宽为250KHz~2.0GHz。

它属于HP ESG系列信号发生器,其频率纯度主要指标如下:SSB Phase Noise (typical, at 20kHz offset)at 500MHz: <-120dBc/Hzat 1000MHz: <-116dBc/Hzat 2000MHz: <-104dBc/HzHarmonics (≤+4dBm output level): < -30dBcNonharmonics (>3kHz offset, <+7dBm output level)250kHz to 1000MHz: <-65dBc>1000MHz to 2000MHz: <-59dBcSubharmonics≤ 1000MHz: None> 1000MHz: <-40dBc从以上指标来看,信号源的谐波分量还比较大(< -30dBc),必须用滤波器将其滤除。

经典:ADC与DAC-动态性能测试

食品安全管理制度清单及其操作流程食品安全管理制度清单:一、从业人员健康管理制度1.食品生产经营者应建立并执行从业人员健康管理制度。

2.从事接触直接入口食品工作的食品生产经营人员应每年进行健康检查,取得健康证明后方可上岗工作。

3.患有国务院卫生行政部门规定的有碍食品安全疾病的人员,不得从事接触直接入口食品的工作。

二、食品安全自查制度1.食品生产经营者应建立食品安全自查制度,定期对食品安全状况进行检查评价。

2.生产经营条件发生变化,不再符合食品安全要求的,食品生产经营者应立即采取整改措施。

3.有发生食品安全事故潜在风险的,应立即停止食品生产经营活动,并向所在地县级人民政府食品药品监督管理部门报告。

三、食品原料、食品添加剂、食品相关产品进货查验制度1.食品生产经营者应建立食品原料、食品添加剂、食品相关产品进货查验制度。

2.对采购的食品原料、食品添加剂、食品相关产品的名称、规格、数量、生产批号、保质期、供货者名称及联系方式、进货日期等内容进行登记,建立台帐。

四、食品出厂检验记录制度1.食品生产经营者应建立食品出厂检验记录制度。

2.对出厂的食品的名称、规格、数量、生产批号、保质期、检验日期等内容进行记录。

五、食品添加剂出厂检验记录制度1.食品生产经营者应建立食品添加剂出厂检验记录制度。

2.对出厂的食品添加剂的名称、规格、数量、生产批号、保质期、检验日期等内容进行记录。

六、食品安全追溯体系1.食品生产经营者应建立食品安全追溯体系,保证食品可追溯。

2.对食品的生产、流通、消费等环节进行记录,确保食品来源可查、去向可追。

七、不合格食品处置制度1.食品生产经营者应建立不合格食品处置制度。

2.对检测不合格的食品进行标记、隔离,并及时采取整改、召回等措施。

八、食品安全突发事件应急处置方案1.食品生产经营者应制定食品安全突发事件应急处置方案。

2.在发生食品安全突发事件时,立即启动应急预案,采取控制、处理措施,并及时报告。

高速高精度ADC的测试方法

http://www.cicmag.com(总第238期)2019·3·图2微分非线性误差DNL图1理想器件1前言随着高速数字电路的发展,高速ADC 在航天国防、数字通信、卫星通信、图像处理等众多领域得到了非常广泛的应用。

ADC 的采样率和垂直分辨率越来越高,对ADC 指标的测试也提出了更高要求。

2测试参数2.1静态参数ADC 的测试指标和参数主要分为静态参数和动态参数两类。

其中静态参数又称线性参数,反映的是器件内部电路的误差。

对ADC 来说,这些内部误差包括器件的增益、偏移、微分非线性(DNL )和积分非线性(INL )误差,这些参数说明了静止的模拟信号转换成数字信号的情况,主要关注具体电平与相应数字编码之间的关系。

测试ADC 静态性能时,要考虑两个重要因素:第一,不仅要给一个既定的模拟电压,电压精度要高,还必须考虑模拟电压的范围以及代码间的转换特性;第二,静态测试是一个交互性过程,要在不同输入信号下测试实际输出。

静态测试的主要项目有:微分非线性误差、积分非线性误差、偏移与增益误差。

1.微分非线性误差(DNL ,Differential nonlin-earity )理想ADC 器件,相邻两个数据刻度之间,对应模拟电压的差值(步距)都是一样的。

但实际上,相邻两刻度之间的间距不可能都是相等的。

所以,ADC 相邻两刻度之间最大的差异与理想步距的差值,就叫微分非线性DNL ,也称为差分非线性,以LSB 为单位(LSB ,最低有效位,即理论上的最小可分辨模拟电压值,比如1.024V 基准电压,10bit 的ADC ,其LSB 为0.001V )。

理想器件,DNL 都应该为0LSB ,如图1。

而实际器件,如图2,DNL =(2.2-1)LSB =1.2LSB 。

高速高精度ADC 的测试方法孙承志(是德科技)69http://www.cicmag.com(总第238期)2019·3·图4频谱分析方法2.积分非线性误差(INL ,Integral nonlinearity )积分非线性表示了ADC 器件在所有的数值点上对应的模拟值和真实值之间误差最大的那一点的误差值,也就是输出数值偏离线性最大的距离。

高速adda的原理

高速adda的原理高速ADC(Analog-to-Digital Converter,模数转换器)是一种将模拟信号转换成数字信号的电子设备。

在高速通信、图像处理、雷达系统以及许多其他领域中,对于高速数据采集和处理的需求越来越高。

高速ADC的原理主要包括采样、量化和编码三个过程。

首先,采样是指将连续的模拟信号离散化成一系列的采样点。

在高速ADC中,常用的采样方式是周期性采样,即以固定的时间间隔对模拟信号进行采样。

采样定理指出,在对连续的带限信号进行采样时,采样频率必须高于信号中最高频率的两倍,才能保证采样信号的完整重构。

因此,高速ADC需要具备高采样速度和广带宽特性,以满足高速信号的采样需求。

其次,量化是指将连续的采样点映射为离散的量化级别。

在高速ADC中,量化的精度通常由位宽表示,例如12位或14位。

量化过程是将模拟信号映射为一系列离散的数字值,以表示信号的幅度。

量化的原则是将连续的模拟信号划分为若干个等间隔的区间,每个区间对应一个离散的量化级别。

常见的有两种量化方式,分别是线性量化和非线性量化。

线性量化通常采用均匀量化,即将每个量化级别之间的间隔保持相等。

而非线性量化则采用更加灵活的非均匀量化,以提高对信号细节的重构性能。

最后,编码是将量化后的离散值转换为数字信号的二进制表示。

在高速ADC中,常用的编码方式包括二进制编码和余弦编码。

二进制编码是将量化值转换为二进制数字的编码方式,每个量化级别对应一个二进制码字。

余弦编码利用余弦函数的周期性特性,将量化值转换为一系列脉冲的编码方式。

编码过程是将连续的量化值转换为离散的数字信号,以便后续数字处理器进行进一步处理和分析。

在高速ADC中,为了实现高速采样和高分辨率的要求,通常使用并行采样和分时采样两种方式。

并行采样是指同时对多个采样点进行采样,以提高采样速度。

分时采样则是将采样点分为多个时刻进行采样,以降低采样速度要求。

此外,高速ADC还需要通过射频前端模块,进行放大、滤波、混频等处理,以适应不同频率范围和信号类型的采样要求。

高速ADC的性能测试

高速ADC的性能测试 文章作者:王卫江 陶 然 摘要:针对某信号处理机中的高速A/D转换器(ADC)的应用,利用数字信号处理机的硬件平台,采用纯正弦信号作为输入信号,用数字信号处理器(DSP)控制采样,并将A/D转换后的数据存储,进行FFT变换,进而来分析ADC的信噪比及有效位数。

该测试方法具有全数字、可编程、精确度高等优点,是较为先进的测试方法。

关键词:AD转换器 信噪比 有效位数 FFT DSP 目前的实时信号处理机要求ADC尽量靠近视频、中频甚至射频,以获取尽可能多的目标信息。

因而,ADC的性能好坏直接影响整个系统指标的高低和性能好坏,从而使得ADC的性能测试变得十分重要。

ADC静态测试的方法已研究多年,国际上已有标准的测试方法,但静态测试不能反映ADC的动态特性,因此有必要研究动态测试方法。

动态特性包括很多,如信噪比(SNR)、信号与噪声+失真之比(SINAD)、总谐波失真(THD)、无杂散动态范围(SFDR)、双音互调失真(TTIMD)等。

本文讨论了利用数字方法对ADC的信噪比进行测试,计算出有效位数,并通过测试证明了提高采样频率能改善SNR,相当于提高了ADC的有效位数。

在本系统中使用了AD9224,它是12bit、40MSPS、单5V供电的流水线型低功耗ADC。

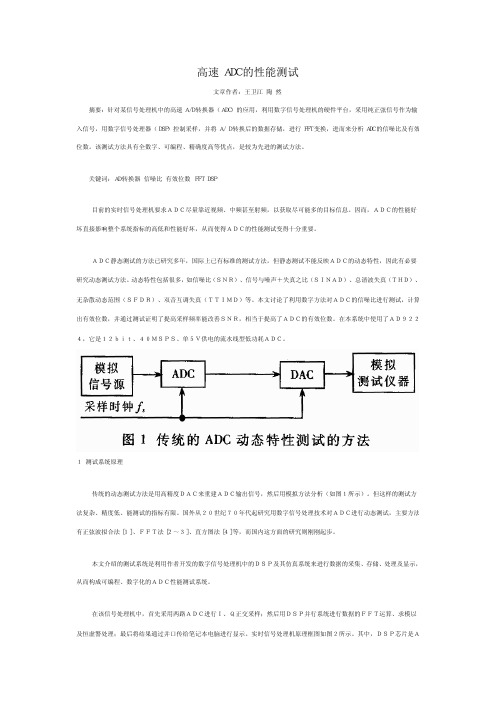

1 测试系统原理 传统的动态测试方法是用高精度DAC来重建ADC输出信号,然后用模拟方法分析(如图1所示)。

但这样的测试方法复杂、精度低、能测试的指标有限。

国外从20世纪70年代起研究用数字信号处理技术对ADC进行动态测试,主要方法有正弦波拟合法[1]、FFT法[2~3]、直方图法[4]等,而国内这方面的研究则刚刚起步。

本文介绍的测试系统是利用作者开发的数字信号处理机中的DSP及其仿真系统来进行数据的采集、存储、处理及显示,从而构成可编程、数字化的ADC性能测试系统。

在该信号处理机中,首先采用两路ADC进行I、Q正交采样;然后用DSP并行系统进行数据的FFT运算、求模以及恒虚警处理;最后将结果通过并口传给笔记本电脑进行显示。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

高速ADC/DAC测试原理及测试方法随着数字信号处理技术和数字电路工作速度的提高,以及对于系统灵敏度等要求的不断提高,对于高速、高精度的ADC、DAC的指标都提出了很高的要求。

比如在移动通信、图像采集等应用领域中,一方面要求ADC有比较高的采样率以采集高带宽的输入信号,另一方面又要有比较高的位数以分辨细微的变化。

因此,保证ADC/DAC在高速采样情况下的精度是一个很关键的问题。

ADC/DAC芯片的性能测试是由芯片生产厂家完成的,需要借助昂贵的半导体测试仪器,但是对于板级和系统级的设计人员来说,更重要的是如何验证芯片在板级或系统级应用上的真正性能指标。

一、ADC的主要参数ADC的主要指标分为静态指标和动态指标2大类。

静态指标主要有:•Differential Non-Linearity (DNL)•Integral Non-Linearity (INL)•Offset Error•Full Scale Gain Error动态指标主要有:•Total harmonic distortion (THD)•Signal-to-noise plus distortion (SINAD)•Effective Number of Bits (ENOB)•Signal-to-noise ratio (SNR)•Spurious free dynamic range (SFDR)二、ADC的测试方案要进行ADC这些众多指标的验证,基本的方法是给ADC的输入端输入一个理想的信号,然后对ADC转换以后的数据进行采集和分析,因此,ADC的性能测试需要多台仪器的配合并用软件对测试结果进行分析。

下图是一个典型的ADC测试方案:如图所示,由Agilent 的ESG 或PSG 做为信号源产生高精度、高纯净度的正弦波信号送给被测的ADC 做为基准信号,ADC 会在采样时钟的控制下对这个正弦波进行采样,变换后的结果用逻辑分析仪采集下来。

ESG 或PSG 是非常纯净的模拟源,其相噪特性非常优异,因此可以产成非常纯净的正弦波,以下是PSG 的相噪特性:对于高精度ADC 的测试来说,测试中需要对ESG 或PSG 产生的信号进行进一步的滤波以滤去谐波和杂散信号,滤波器的参数要根据用户实际使用的信号频率范围选择。

对于高精度的ADC 来说,采样时钟的抖动对于测试结果的影响非常大,因此测试中还需要高质量的码型发生器或信号发生器来产生ADC 的采样时钟。

采用码型发生器的好处是可以直接输出差分的方波信号,和ADC 芯片接口比较方便。

以下是8113X 码型发生器的主要时钟指标:Sine Wave PC(with GPIB)AgilentVEE16900 series码型发生器由于是数字源,其时钟抖动很难控制到1ps以下,因此对于有12bit或更高精度的测试要求时,需要使用ESG或PSG作为时钟源,ESG或PSG 是高质量的模拟源,所以其相噪指标非常好.抖动相当于相噪的积分,因此PSG 产生的时钟抖动可以<1ps。

但由于ESG/PSG只能产生单端正弦波信号,所以和ADC接口时有时需要相应的转换电路,这个可参考芯片厂家的参考设计。

由于ADC的模拟部分对于数字噪声非常敏感,因此ADC的供电要模拟和数字部分分开,PCB板上还要对模拟部分电源做充分滤波。

测试中需要采用高质量的线性电源供电,Agilent的E363X或E364X系列都可以满足要求。

ADC转换后的结果要通过逻辑分析仪采集下来,逻辑分析仪工作在状态采样模式,需要使用的通道数取决于ADC的位数,状态采样率取决于ADC的采样率,存储深度取决于采样率和要分析的频率分辨率,同时逻辑分析仪还要能在高速数据传输率下提供可靠灵活的连接。

Agilent的16900系列逻辑分析仪配合高性能的16950B采集模块和SoftTouch探头是一个很好的选择。

三、ADC测试结果的分析ADC的静态指标是对正弦波的采样数据进行幅度分布的直方图统计间接计算得到,如下图所示,理想正想波的幅度分布应该是左面的形状,由于非线性等的影响,分布可能会变成右边的形状,通过对直方图分析可以得出静态参数的指标。

以下是DNL和INL的计算公式:ADC的动态指标是对正弦波的采样数据进行FFT频谱分析间接计算得到。

一个理想的正弦波经A/D采样再做频谱分析可能会变成如下图的形状,除了主要的正弦波分量以外还产生了很多噪声、谐波和杂散,通过对这些分量的运算,可以得到ADC的动态参数。

下面是动态参数的计算公式:ADC产生的测试数据被逻辑分析仪捕获下来送到测试软件进行分析,这要求逻辑分析仪有比较高的状态采样率和一定的存储深度并能和被测板进行可靠的信号连接。

测试软件是基于Agilent的VEE编程环境,实现的功能是对整个测试系统进行控制并对测试结果分析。

下图是静态参数的分析结果举例:下图是一个ADC动态参数测量的结果举例:四、ADC测试的配置方案以下是一个推荐的ADC测试系统配置,列出了测试中需要的主要仪器。

l正弦信号源:E8257D with UNX option;l正弦时钟源:E4438C with UNJ option;l逻辑分析仪:16901A+16950B+探头(E5390A、E5382A);l电源:E3631A;l软件: ADC测试软件l其它:GPIB电缆、82357等根据不同的测试精度、频率、采样率需求,这个配置可能会有相应变化,也有可能会有不同的选件。

测试中的ADC测试板、滤波器、时钟变换电路、电缆等附件未包括在内。

五、DAC的主要参数DAC的作用是和ADC相反,是把数字量转换成模拟量,虽然有模拟和数字的区别,但是DAC要测试的主要指标与ADC类似,也分为静态指标和动态指标2大类。

静态指标主要有:•Differential Non-Linearity (DNL)•Integral Non-Linearity (INL)•Offset Error•Full Scale Gain Error•Conversion Rate•Settling Time•Rising/Falling Time动态指标主要有:•Total harmonic distortion (THD)•Signal-to-noise plus distortion (SINAD)•Effective Number of Bits (ENOB)•Signal-to-noise ratio (SNR)•Spurious free dynamic range (SFDR)六、DAC的测试方案对于DAC来说,测试方法正好和ADC相反,是在输入端加数字激励信号,在模拟输出端测试其输出性能的指标。

下图是一个DAC的测试方案:测试中使用16800或16900逻辑分析的码型发生功能产生需要的测试码型,16800或16900逻辑分析的码型发生器最多可以产生48路并行的码型激励,其数据速率最大300Mb/s,最大码型深度可以达到16M,因此可以产生非常复杂的高速并行码型,其支持的逻辑电平主要有TTL/CMOS/ECL/PECL/LVDS等。

下图是16901A逻辑分析仪和码型发生模块16720A。

当需要更高速率的码型时,可以使用Agilent的高速并行误码仪ParBert81250提供的高速多通道的数字码型。

81250是基于VXI机箱的多通道误码仪,利用其码型发生功能最多可以同时产生132路675Mb/S以下的数字信号,或最多66路3.35Gb/S以下的数字信号,或最多30路13.5Gb/S以下的数字信号。

下图是81250的外观。

测试中用81130码型发生器产生逻辑分析仪和DAC需要的转换时钟。

当需要高质量的时钟源时,也可用正弦波信号源代替码型发生器。

码型发生器发出的并行数据经DAC转换成模拟量后送给测试仪器做分析,根据测试项目的不同,需要的测试仪器也不同。

对于静态参数的测量用的是万用表和示波器,对于动态参数的测量用的是频谱仪。

仪器采集到DAC输出的数据后把测试数据送到测试软件中进行分析,给出测试结果。

测试软件同时还完成整个测试系统的控制。

七、DAC测试结果的分析对于DAC来说,测试不同参数码型发生器发出的数据是不同的,所用的分析仪器也不同。

1、用码型发生器发出数值顺序从0至(2^n-1)的阶梯波,每增加一个数值,用万用表测量一下相应DAC输出端的电压。

测量出每个数字输入值对应的真实模拟输出量后就可以得出INL、DNL、Gain Error、Offset Error等信息。

测量中使用的仪器是万用表,Agilent的34411万用表具有6位半(十进制)的分辨率、很好的精度及很快的测量速度,因此可以很好地用于12位以下DAC 的测量。

对于更高精度的测量,可以选择8位半的数字表3458A。

以下是3458A 不同电压量程下的测量精度。

2、用码型发生器产生数值从0至(2^n-1)来回跳变的三角波,逐渐增加码型发出速度,直至模拟输出低于刚才的满量程范围1LSB。

通过这种方法可以判断DAC的Conversion Rate。

3、用码型发生器产生数值从0至(2^n-1)的阶跃脉冲,用示波器测量输出波形的Settling Time、Rising/Falling Time等参数。

对于建立时间和上升/下降时间的测量需要用到的是示波器,对于仪器的要求是足够的带宽、较低的噪声和比较平坦的频响特性。

对于高速DAC芯片的测试,推荐的是Agilent的80000系列示波器,其在2G~13G的带宽范围内提供了非常优异的频响特性和最低的本底噪声,因此可以进行准确的参数测量。

具体的带宽需求可以根据下面公式计算:4、对于动态参数的测试,是预先在码型发生器里放入一组正弦波的数字波形,然后送给DAC转换成真正的模拟正弦波信号,用频谱仪对波形的谐波失真、杂散、噪声等做分析。

以下是各参数的计算公式。

动态参数的测量仪器是频谱仪,对于仪器的要求是要有比较高的频率、幅度测量精度、低的本底噪声和足够的动态范围。

Agilent的MXA/PSA系列频谱分析仪是一个很好的选择。

5、测试软件可以帮助完成仪器设置和参数的分析。

以下是基于AgilentVEE 编程环境的DAC软件提供的DAC测量结果。

静态参数:动态参数:八、DAC测试的配置方案以下是一个推荐的DAC测试系统配置,列出了测试中需要的主要仪器。

l逻辑分析仪:16901A+16720A码型模块+电平转换接头(16720A -011~052 option);l码型发生器:81130A+2*81132Al万用表:3458A with 002 option;l示波器: DSO90254A+探头l频谱仪:E4443Al电源:E3631A;l软件:DAC测试软件l其它:GPIB电缆、82357等对于300M~3.35G速率的8~14bitDAC测试,可以使用如下配置:l并行误码仪81250(with 013、148 option)+Software E4875A-ATO+E4808A clock module + 8* E4861B data module + 16*E4862B;l万用表:3458A with 002 option;l示波器: DSO90604A+探头l频谱仪:E4443Al电源:E3631A;l软件:DAC测试软件l其它:GPIB电缆、82357等根据不同的测试精度、频率、采样率需求,这个配置可能会有相应变化,也有可能会有不同的选件。