数字电子技术基础PPT汇总

合集下载

数字电子技术基础全套ppt课件

输出方程

Y ( A Q ( 1 Q 2 ) ( A Q 1 Q 2 ) ) A Q 1 Q 2 A Q 1 Q 2

③计算、 列状态转

换表

Y 输A 入Q 1 Q 2 现A Q 态1 Q 2

A Q2 Q1

次

Q2*

态

Q1*

00 0

01

00 1

10

01 0

11

QQ102*1*AQ01 1 Q1

双向移位寄存器

2片74LS194A接成8位双向移位寄存器

用双向移位寄存器74LS194组成节日彩灯控制电路

1k

LED 发光 二极管

Q=0时 LED亮

+5V

RD Q0 DIR D0

Q1

Q2

Q3 S1

74LS194

S0

D1 D2 D3 DIL CLK +5V

RD Q0 DIR D0

Q1

Q2

Q3 S1

二.一般掌握的内容:

(1)同步、异步的概念,电路现态、次态、有效 状态、无效状态、有效循环、无效循环、自启动的 概念,寄存的概念;

(2)同步时序逻辑电路设计方法。

6.1 概述

一、组合电路与时序电路的区别

1. 组合电路: 电路的输出只与电路的输入有关, 与电路的前一时刻的状态无关。

2. 时序电路:

电路在某一给定时刻的输出

1 0 Q2

0 1

0 1

10 1

00

11 0

01

11 1

10

输出

Y

0 0 0 1 1 0 0 0

Q Q2*1*D D21A Q1 Q1 Q2

YA Q 1 Q 2A Q 1 Q 2

转换条件

Y ( A Q ( 1 Q 2 ) ( A Q 1 Q 2 ) ) A Q 1 Q 2 A Q 1 Q 2

③计算、 列状态转

换表

Y 输A 入Q 1 Q 2 现A Q 态1 Q 2

A Q2 Q1

次

Q2*

态

Q1*

00 0

01

00 1

10

01 0

11

QQ102*1*AQ01 1 Q1

双向移位寄存器

2片74LS194A接成8位双向移位寄存器

用双向移位寄存器74LS194组成节日彩灯控制电路

1k

LED 发光 二极管

Q=0时 LED亮

+5V

RD Q0 DIR D0

Q1

Q2

Q3 S1

74LS194

S0

D1 D2 D3 DIL CLK +5V

RD Q0 DIR D0

Q1

Q2

Q3 S1

二.一般掌握的内容:

(1)同步、异步的概念,电路现态、次态、有效 状态、无效状态、有效循环、无效循环、自启动的 概念,寄存的概念;

(2)同步时序逻辑电路设计方法。

6.1 概述

一、组合电路与时序电路的区别

1. 组合电路: 电路的输出只与电路的输入有关, 与电路的前一时刻的状态无关。

2. 时序电路:

电路在某一给定时刻的输出

1 0 Q2

0 1

0 1

10 1

00

11 0

01

11 1

10

输出

Y

0 0 0 1 1 0 0 0

Q Q2*1*D D21A Q1 Q1 Q2

YA Q 1 Q 2A Q 1 Q 2

转换条件

数字电子技术基础教学课件PPT

小结

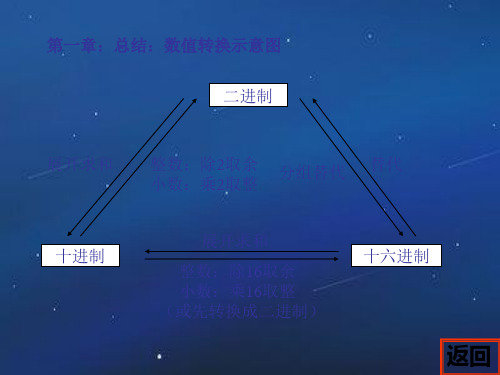

日常生活中使用十进制,但在计算机中基本上使用二进制, 有时也使用八进制或十六进制。利用权展开式可将任意进制数

常用的几种 BCD 码

十进 制数 8421 BCD码 2421 BCD码 5121 BCD码 余 3码 余3 循环码

0 1 2 3 4 5 6 7 8 9

0000 0001 0010 0011 0100 0101 0110 0111 1000 1001

0000 0001 0010 0011 0100 1011 1100 1101 1110 1111

注意:如无特别说明,本课程中的BCD码一概指组合的8421BCD码。

格雷码(Gray)

任意两个相邻码组之间只有一位码元不同(0和最大 数之间也只有一位不同),因此格雷码也称为循 环码;这种编码在形成和传输时不易出错。

比如:十进制3转换为4时,对应二进制的每一位变化,都会产

生很大的尖峰电流脉冲

上述编码方式是针对 “一位” 十进制数字而言的,一个多位的十进制数 与相应的8421BCD码之间的转换关系如下例所示: 3 0 9 1 十进制数:

对应的8421BCD码:

0011

0000

1001

0001

这样得到的BCD码在存放或处理时有两种格式: • 组合BCD码格式:每位十进制数字对应的BCD编码以四个二进制位来存放; (3091)10=(0011 0000 1001 0001)BCD • 非组合BCD码格式:每位十进制数字对应的BCD编码以八个二进制位来存放, 其中低四位存放真正的BCD码,高四位根据具体应用的不同定义为不同的 值 —— 如无特殊要求,高四位通常为全0; (3091)10=(00000011 00000000 00001001 00000001)BCD

《数字电子技术基础》(第四版)

CPLD结构特点

CPLD(复杂可编程逻辑器件)是一种基于乘积项的可编程逻辑器件,具有简单的结构和较快 的处理速度。它采用与或阵列(AND-OR Array)来实现逻辑功能,适用于中小规模的数字 电路设计。

FPGA与CPLD比较

FPGA和CPLD在结构、性能和适用场景上有所不同。FPGA具有更高的逻辑密度和更灵活 的可编程性,适用于大规模的数字电路设计和复杂的算法实现;而CPLD则具有更简单的 结构和更快的处理速度,适用于中小规模的数字电路设计和控制应用。

容量和提高存取速度

应用实例

如计算机的内存条就是采用RAM 存储器进行扩展的;而一些嵌入 式系统中则采用ROM存储器来

存储固件和程序代码等

发展趋势

随着科技的不断发展,存储器的 容量不断增大,存取速度不断提 高,功耗不断降低,未来存储器 将更加智能化、高效化和绿色化

05 可编程逻辑器件与EDA技 术

PLD可编程逻辑器件概述

要点一

PLD定义与分类

可编程逻辑器件(PLD)是一种通用集 成电路,用户可以通过编程来配置其逻 辑功能。根据结构和功能的不同,PLD 可分为PAL、GAL、CPLD、FPGA等类 型。

要点二

PLD基本结构

PLD的基本结构包括可编程逻辑单元 、可编程互连资源和可编程I/O单元 等。其中,可编程逻辑单元是实现逻 辑功能的基本单元,可编程互连资源 用于实现逻辑单元之间的连接,可编 程I/O单元则负责与外部电路的连接 。

逻辑代数法

利用逻辑代数化简和变换电路 表达式

图形化简法

利用卡诺图化简电路

பைடு நூலகம்

状态转换表

列出电路的状态转换过程,便 于分析和理解电路功能

状态转换图

以图形方式表示电路的状态转 换过程,直观易懂

CPLD(复杂可编程逻辑器件)是一种基于乘积项的可编程逻辑器件,具有简单的结构和较快 的处理速度。它采用与或阵列(AND-OR Array)来实现逻辑功能,适用于中小规模的数字 电路设计。

FPGA与CPLD比较

FPGA和CPLD在结构、性能和适用场景上有所不同。FPGA具有更高的逻辑密度和更灵活 的可编程性,适用于大规模的数字电路设计和复杂的算法实现;而CPLD则具有更简单的 结构和更快的处理速度,适用于中小规模的数字电路设计和控制应用。

容量和提高存取速度

应用实例

如计算机的内存条就是采用RAM 存储器进行扩展的;而一些嵌入 式系统中则采用ROM存储器来

存储固件和程序代码等

发展趋势

随着科技的不断发展,存储器的 容量不断增大,存取速度不断提 高,功耗不断降低,未来存储器 将更加智能化、高效化和绿色化

05 可编程逻辑器件与EDA技 术

PLD可编程逻辑器件概述

要点一

PLD定义与分类

可编程逻辑器件(PLD)是一种通用集 成电路,用户可以通过编程来配置其逻 辑功能。根据结构和功能的不同,PLD 可分为PAL、GAL、CPLD、FPGA等类 型。

要点二

PLD基本结构

PLD的基本结构包括可编程逻辑单元 、可编程互连资源和可编程I/O单元 等。其中,可编程逻辑单元是实现逻 辑功能的基本单元,可编程互连资源 用于实现逻辑单元之间的连接,可编 程I/O单元则负责与外部电路的连接 。

逻辑代数法

利用逻辑代数化简和变换电路 表达式

图形化简法

利用卡诺图化简电路

பைடு நூலகம்

状态转换表

列出电路的状态转换过程,便 于分析和理解电路功能

状态转换图

以图形方式表示电路的状态转 换过程,直观易懂

数字电子技术基础全套课件ppt

二进制 补码的 形式编 码

经 营 者 提 供 商品或 者服务 有欺诈 行为的 ,应当 按照消 费者的 要求增 加赔偿 其受到 的损失 ,增加 赔偿的 金额为 消费者 购买商 品的价 款或接 受服务 的费用

二、直接A/D转换器

并联比较型

0≤vi < VREF/15 时,7个比较 器输出全为0, CP 到来后,7 个触发器都置 0。经 编码器编码后 输出的二进制 代 码 为 d2d1d0 =000。

教学内容

§11.1 概述 §11.2 D/A转换器 §11.3 A/D转换器

教学要求

1、掌握DAC和ADC的定义及应用; 2、了解DAC的组成、倒T型电阻网络、集 成D/A转换器、转换精度及转换速度; 3、了解ADC组成、逐次逼近型A/D转换器、 积分型A/D转换器、转换精度及转换速度。

11.1 概述

取 1 8

取 2 15

最大量化误差为 △,即1/8V

最大量化误差为 1/2△,即1/15V

经 营 者 提 供 商品或 者服务 有欺诈 行为的 ,应当 按照消 费者的 要求增 加赔偿 其受到 的损失 ,增加 赔偿的 金额为 消费者 购买商 品的价 款或接 受服务 的费用

对双极性模拟电压的量化和编码

由于V-≈V+=0,所以开关S合到哪一边,都相当 于接到了“地”电位,流过每条电路的电流始终不 变。可等效为:

经 营 者 提 供 商品或 者服务 有欺诈 行为的 ,应当 按照消 费者的 要求增 加赔偿 其受到 的损失 ,增加 赔偿的 金额为 消费者 购买商 品的价 款或接 受服务 的费用

i2 Id34 Id28 Id11Id 60 取RF=R

CB7520电路原理图

经 营 者 提 供 商品或 者服务 有欺诈 行为的 ,应当 按照消 费者的 要求增 加赔偿 其受到 的损失 ,增加 赔偿的 金额为 消费者 购买商 品的价 款或接 受服务 的费用

经 营 者 提 供 商品或 者服务 有欺诈 行为的 ,应当 按照消 费者的 要求增 加赔偿 其受到 的损失 ,增加 赔偿的 金额为 消费者 购买商 品的价 款或接 受服务 的费用

二、直接A/D转换器

并联比较型

0≤vi < VREF/15 时,7个比较 器输出全为0, CP 到来后,7 个触发器都置 0。经 编码器编码后 输出的二进制 代 码 为 d2d1d0 =000。

教学内容

§11.1 概述 §11.2 D/A转换器 §11.3 A/D转换器

教学要求

1、掌握DAC和ADC的定义及应用; 2、了解DAC的组成、倒T型电阻网络、集 成D/A转换器、转换精度及转换速度; 3、了解ADC组成、逐次逼近型A/D转换器、 积分型A/D转换器、转换精度及转换速度。

11.1 概述

取 1 8

取 2 15

最大量化误差为 △,即1/8V

最大量化误差为 1/2△,即1/15V

经 营 者 提 供 商品或 者服务 有欺诈 行为的 ,应当 按照消 费者的 要求增 加赔偿 其受到 的损失 ,增加 赔偿的 金额为 消费者 购买商 品的价 款或接 受服务 的费用

对双极性模拟电压的量化和编码

由于V-≈V+=0,所以开关S合到哪一边,都相当 于接到了“地”电位,流过每条电路的电流始终不 变。可等效为:

经 营 者 提 供 商品或 者服务 有欺诈 行为的 ,应当 按照消 费者的 要求增 加赔偿 其受到 的损失 ,增加 赔偿的 金额为 消费者 购买商 品的价 款或接 受服务 的费用

i2 Id34 Id28 Id11Id 60 取RF=R

CB7520电路原理图

经 营 者 提 供 商品或 者服务 有欺诈 行为的 ,应当 按照消 费者的 要求增 加赔偿 其受到 的损失 ,增加 赔偿的 金额为 消费者 购买商 品的价 款或接 受服务 的费用

《数字电子技术基础》核心知识总结.ppt

M

CI

例:试利用两片4位二进制并行加法器74LS283和必要的 门电路组成1位二-十进制加法器电路。

解:根据BCD码中8421码 的加法运算规则,当两数 之和小于、等于9(1001) 时,相加的结果和按二进 制数相加所得到的结果一 样。当两数之和大于9(即 等于1010~1111)时,则应 在按二进制数相加的结果 上加6(0110),这样就可 以给出进位信号,同时得 到一个小于9的和。

分离出多余变量,将余下的变量分别有序地加到数据选择器的数 据输入端。

3.对照比较所求逻辑函数式和数据选择器的输出表达式确定选择 器输入变量的表达式或取值。

4.按照求出的表达式或取值连接电路,画电路连线图。 注意:

一个数据选择器只能用来实现一个多输入变量的单输出逻辑函 数。

4.22.用8选1数据选择器设计一个函数发生器, S1S0 输出 00 Y=AB

S0

B0

CI

完成二进制数相加操作

完成和的修正操作

第六章:同步二进制计数器

74161具有异步清零和同步置数功能. 74163具有同步清零和同步置数功能.

74LS191具有异步置数功能. 74LS193具有异步清零和异步置数功能.

第十章:本节小结

555接成施密特触发器

555接成单稳态触发器

555接成多谐振荡器

tw=1.1RC

振荡周期: T=0.69(R1+2R2)C

第十一章:本 章 小 结 学习本章,应能达到下列要求: (1)掌握下列概念:采样保持,量化编码,分辨率。 (2)掌握DAC的分类、组成原则、原理和特点。 (3)掌握ADC的分类和特点,掌握并联比较型、计数反馈型、逐

次渐近型ADC的组成原则,掌握双积分型ADC的原理和特点 (4)了解转换精度和转换速度的概念。

【精品PPT】数字电子技术基础全套课件-2(2024版)

一、逻辑函数

如果以逻辑变量作为输入,以运算结果作为 输出,当输入变量的取值确定之后,输出的取值 便随之而定。输出与输入之间的函数关系称为逻 辑函数。Y=F(A,B,C,…)

二、逻辑函数表示方法 常用逻辑函数的表示方法有:逻辑真值表(真

值表)、逻辑函数式(逻辑式或函数式)、逻辑 图、波形图、卡诺图及硬件描述语言。它们之间 可以相互转换。

( A B)

B A

( A B)

Y (( A B) ( A B)) ( A B)( A B) AB AB

5、波形图→真值表

A

1111

0000

B

11

11

00

00

C 1111

00

Y 11

00 11

0

00 0

ABC Y 00 0 0 t 00 1 1 01 0 1 t 01 1 0 10 0 0 t 10 1 1 11 0 0 t 11 1 1

A断开、B接通,灯不亮。

将开关接通记作1,断开记作0;灯亮记作1,灯 灭记作0。可以作出如下表格来描述与逻辑关系:

功能表

开关 A 开关 B 灯 Y

A

断开 断开

灭

0

断开 闭合

灭

0

1

闭合 断开

灭

1

闭合 闭合 亮

BY

00 真 10 值

00 表

11

两个开关均接通时,灯才会 Y=A•B

亮。逻辑表达式为:

实现与逻辑的电路称为与门。

与门的逻辑符号:

A

&

Y Y=A•B

B

二、或逻辑(或运算)

或逻辑:当决定事件(Y)发生的各种条件A,B,

C,…)中,只要有一个或多个条件具备,事件(Y)

如果以逻辑变量作为输入,以运算结果作为 输出,当输入变量的取值确定之后,输出的取值 便随之而定。输出与输入之间的函数关系称为逻 辑函数。Y=F(A,B,C,…)

二、逻辑函数表示方法 常用逻辑函数的表示方法有:逻辑真值表(真

值表)、逻辑函数式(逻辑式或函数式)、逻辑 图、波形图、卡诺图及硬件描述语言。它们之间 可以相互转换。

( A B)

B A

( A B)

Y (( A B) ( A B)) ( A B)( A B) AB AB

5、波形图→真值表

A

1111

0000

B

11

11

00

00

C 1111

00

Y 11

00 11

0

00 0

ABC Y 00 0 0 t 00 1 1 01 0 1 t 01 1 0 10 0 0 t 10 1 1 11 0 0 t 11 1 1

A断开、B接通,灯不亮。

将开关接通记作1,断开记作0;灯亮记作1,灯 灭记作0。可以作出如下表格来描述与逻辑关系:

功能表

开关 A 开关 B 灯 Y

A

断开 断开

灭

0

断开 闭合

灭

0

1

闭合 断开

灭

1

闭合 闭合 亮

BY

00 真 10 值

00 表

11

两个开关均接通时,灯才会 Y=A•B

亮。逻辑表达式为:

实现与逻辑的电路称为与门。

与门的逻辑符号:

A

&

Y Y=A•B

B

二、或逻辑(或运算)

或逻辑:当决定事件(Y)发生的各种条件A,B,

C,…)中,只要有一个或多个条件具备,事件(Y)

数字电子技术基础ppt课件

R

vo K合------vo=0, 输出低电平

vi

K

只要能判

可用三极管 代替

断高低电 平即可

在数字电路中,一般用高电平代表1、低 电平代表0,即所谓的正逻辑系统。

2.2.2 二极管与门

VCC

A

D1

FY

B

D2

二极管与门

A

B

【 】 内容 回顾

AB Y 00 0 01 0 100 11 1

&

Y

2.2.2 二极管或门

一般TTL门的扇出系数为10。

三、输入端负载特性

输入端 “1”,“0”?

A

ui

RP

R1 b1

c1

T1

D1

•

R2

•

T2

•

R3

VCC

•

R4

T4 D2

•

Y

T5

•

简化电路

R1

VCC

ui

A ui

T1

be

RP

2

be 0

RP

5

RP较小时

ui

RP RP R1

(Vcc Von )

当RP<<R1时, ui ∝ RP

•

R4

T4 D2

•

Y

T5

•

TTL非门的内部结构

•

R1

R2

A

b1 c1

T1

•

T2

D1

•

R3

VCC

•

R4

T4 D2

•

Y

T5

•

前级输出为 高电平时

•

R2

R4

VCC

T4 D2

数字电子技术基础全套课件共580页

= 1×25 + l×24 + 0×23 + 1×22 + 0×21 + l×20 + 1×2-1 + 0×2-2 + 1×2-3 = 32 + 16 + 0 + 4 + 0 + 1 + 0.5 + 0 + 0.125 = (53.625) D 【例1-2】 将十六进制数(4E5.8) H转换为十进制数。 解:(4E5.8) H = 4×(16)2 + E×(16)1 + 5×(16)0 + 8×(16)-1

将每个十六进制数用4位二进制来书写, 其最左侧或最右侧的可以省去。

通常采用基数乘除法。

二进制数

转换

十进制数

将对应的二、十六进制数按各位权展开, 并把各位值相加。

10

1.3.1 十六进制、二进制数与十进制数间的转换

【例1-1】将二进制数(110101.101)2转换为十进制数。 解:(110101.101)2

0 …… 1 高位

小数部分

0.625

整数

×2

1.250 ……… 1 高位

0.250

×2

0.500 ……… 0(顺序)

×2

1.000 ……… 1 低位

即 (59.625)D=(101011.101)B

12

1.3.2 十进制数转换为二进制、十六进制数

【例1-4】 将十进制数(427.34357)D转换成十六进制数。

16

1.4 数字系统中数的表示方法与格式

1.4.1 十进制编码

1. 8421 BCD码 在这种编码方式中,每一位二进制代码都代表一个固定的数值,

把每一位中的1所代表的十进制数加起来,得到的结果就是它所代表 的十进制数码。由于代码中从左到右每一位中的1分别表示8、4、2、 1(权值),即从左到右,它的各位权值分别是8、4、2、1。所以把 这种代码叫做8421码。8421 BCD码是只取四位自然二进制代码的 前10种组合。

将每个十六进制数用4位二进制来书写, 其最左侧或最右侧的可以省去。

通常采用基数乘除法。

二进制数

转换

十进制数

将对应的二、十六进制数按各位权展开, 并把各位值相加。

10

1.3.1 十六进制、二进制数与十进制数间的转换

【例1-1】将二进制数(110101.101)2转换为十进制数。 解:(110101.101)2

0 …… 1 高位

小数部分

0.625

整数

×2

1.250 ……… 1 高位

0.250

×2

0.500 ……… 0(顺序)

×2

1.000 ……… 1 低位

即 (59.625)D=(101011.101)B

12

1.3.2 十进制数转换为二进制、十六进制数

【例1-4】 将十进制数(427.34357)D转换成十六进制数。

16

1.4 数字系统中数的表示方法与格式

1.4.1 十进制编码

1. 8421 BCD码 在这种编码方式中,每一位二进制代码都代表一个固定的数值,

把每一位中的1所代表的十进制数加起来,得到的结果就是它所代表 的十进制数码。由于代码中从左到右每一位中的1分别表示8、4、2、 1(权值),即从左到右,它的各位权值分别是8、4、2、1。所以把 这种代码叫做8421码。8421 BCD码是只取四位自然二进制代码的 前10种组合。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

vA

vo1

vo

使电路迅速跳变到 vo=VOH≈ VDD

R1 R2 R2 VT =VI= VTH=( 1 )VTH R1 R1

Digital Electronics Technology 2019/3/11

v A VTH=

R2 VT R1 R2

10.2 施密特触发器

10.2.1 用门电路组成的施密特触发器

一、脉冲变换

二、脉冲鉴幅

Digital Electronics Technology

2019/3/11

10.2 施密特触发器

三、脉冲整形

Digital Electronics Technology

2019/3/11

10.3 单稳态触发器

特点:

①有一个稳态和一个暂稳态。

②在外界触发信号作用下,能从稳态→暂稳态,维持一段 时间后自动返回稳态。 ③暂稳态维持的时间长短取决于电路内部参数。

的获取方法:

Digital Electronics Technology

2019/3/11

10.1 概述

矩形脉冲特性的主要参数

脉冲周期T 上升时间tr

脉冲幅度Vm 下降时间tf

脉冲宽度tW 占空比q

2019/3/11

Digital Electronics Technology

10.2 施密特触发器

2019/3/11

本章重点

1. 施密特触发器、单稳态触发器、多谐振荡器的 工作特点和典型应用。 2. 555定时器及其应用。

Digital Electronics Technology

2019/3/11

10.1 概述

产生:不用信号源,加上电源自激振荡,

矩形脉冲信号 直接产生波形。 整形:通过各种整形电路把已有的周期 性变化波形变换成符合要求的矩形脉冲。 脉冲产生电路:多谐振荡器 脉冲整形(变换)电路:施密特触发器、 单稳态触发器

数字电子技术基础

Digital Electronics Technology

第10章

脉 冲 波 形 的产生和整形

教学内容

§10.1 概述

§10.2 施密特触发器 §10.3 单稳态触发器 §10.4 多谐振荡器 §10.5 555定时器及其应用

Digital Electronics Technology

应用:

脉冲整形、延时、定时等。

Digital Electronics Technology

2019/3/11

10.3 单稳态触发器

单稳态触发器结构:

两个门电路、一个RC电路

暂稳态靠RC电路的充、放电过程来维持

根据RC电路的不同接法,分为微分型和积分型

Digital Electronics Technology

Digital Electronics Technology 2019/3/11

电压传输特性

10.2 施密特触发器

10.2.1 用门电路组成的施密特触发器 施密特触发器的两个输出电压传输特性

vI

vo

VOH

vo

VT

vI

vA

VOH

vo

VT

VOL 0

VT-

VTH

VT+

VTH

当VI 1时,VO 1 。

当VI , 至VA VTH 时,进入传输 特性的放大区,故

vA

vo1

vo

使电路迅速跳变到

vo=VOL≈ 0

VA VTH (VDD

R1 VI ) VI R1 R2

VT-=VI=( 1 R1 )VTH R2

2019/3/11

由于VTH= VDD / 2,故

VT+

VDD vI

(a)同相输出

(b)反相输出

Digital Electronics Technology

2019/3/11

10.2 施密特触发器

10.2.2 集成施密特触发器

(略)

Digital Electronics Technology

2019/3/11

10.2 施密特触发器

10.2.3 施密特触发器的应用

Digital Electronics Technology

10.2 施密特触发器

10.2.1 用门电路组成的施密特触发器

VI VT VI VT

R1 (1 )VTH R2 R1 (1 )VTH R2

VT=VT+-VT- 2

R1 VTH R2

改变R1 / R2可以调节VT 、VT 和VT 但,必须R1 R2,否则有 VT 2VTH VDD;VT 0 vI 到VDD 或 到0,电路状态不变

2019/3/11

10.3 单稳态触发器

10.3.1 用门电路组成的单稳态触发器 一、积分型

1 . 原理分析

G1和G2为TTL门

* 稳态下: VI 0,VO 1, (VO1 VOH ),VA VOH ;

*VI 后,VO 0, 进入暂稳态, VO1 0, C开始放电;

*当放至 VA VTH 后,VO 1, 返回稳态;

R1< R2 (否则电路进入自锁状态,不能正常工作)

Digital Electronics Technology 2019/3/11

10.2 施密特触发器

10.2.1 用门电路组成的施密特触发器

R2 R1 vI v0 R1 R2 R1 R2

vA

当VI 0时,VO 0。

当VI , 至VA VTH 时,进入传输特性的放 大区(转折区),故

*VI 后,C重新充电至 VOH , 恢复初始态;

Digital Electronics Technology

2019/3/11

10.3 单稳态触发器

施密特触发器(Schmitt Trigger)

特点: 1、输入信号上升和下降时对应的转换电平不同;

2、内部有正反馈,使输出转换波形变得很陡 。 作用: 边沿变化缓慢的波形→边沿陡峭的矩形波;

清除→叠加在矩形波脉冲高、低电平上的噪声。

Digital Electronics Technology

2019/3/11

10.2 施密特触发器

10.2.1 用门电路组成的施密特触发器

两级反相器串接,通过分压电阻把输出端的电压反馈到输入端。

R2 vI R1 v I G1

vo1 1 1

G2 (a) 电路

vo vo

vI vI

vo vo

VTH = VDD/2 , VOH=反相器构成的施密特触发器 VDD, VOL=0,且R1< R2 图 6.2.1 用 CMOS

vo1

vo

使电路迅速跳变到 vo=VOH≈ VDD

R1 R2 R2 VT =VI= VTH=( 1 )VTH R1 R1

Digital Electronics Technology 2019/3/11

v A VTH=

R2 VT R1 R2

10.2 施密特触发器

10.2.1 用门电路组成的施密特触发器

一、脉冲变换

二、脉冲鉴幅

Digital Electronics Technology

2019/3/11

10.2 施密特触发器

三、脉冲整形

Digital Electronics Technology

2019/3/11

10.3 单稳态触发器

特点:

①有一个稳态和一个暂稳态。

②在外界触发信号作用下,能从稳态→暂稳态,维持一段 时间后自动返回稳态。 ③暂稳态维持的时间长短取决于电路内部参数。

的获取方法:

Digital Electronics Technology

2019/3/11

10.1 概述

矩形脉冲特性的主要参数

脉冲周期T 上升时间tr

脉冲幅度Vm 下降时间tf

脉冲宽度tW 占空比q

2019/3/11

Digital Electronics Technology

10.2 施密特触发器

2019/3/11

本章重点

1. 施密特触发器、单稳态触发器、多谐振荡器的 工作特点和典型应用。 2. 555定时器及其应用。

Digital Electronics Technology

2019/3/11

10.1 概述

产生:不用信号源,加上电源自激振荡,

矩形脉冲信号 直接产生波形。 整形:通过各种整形电路把已有的周期 性变化波形变换成符合要求的矩形脉冲。 脉冲产生电路:多谐振荡器 脉冲整形(变换)电路:施密特触发器、 单稳态触发器

数字电子技术基础

Digital Electronics Technology

第10章

脉 冲 波 形 的产生和整形

教学内容

§10.1 概述

§10.2 施密特触发器 §10.3 单稳态触发器 §10.4 多谐振荡器 §10.5 555定时器及其应用

Digital Electronics Technology

应用:

脉冲整形、延时、定时等。

Digital Electronics Technology

2019/3/11

10.3 单稳态触发器

单稳态触发器结构:

两个门电路、一个RC电路

暂稳态靠RC电路的充、放电过程来维持

根据RC电路的不同接法,分为微分型和积分型

Digital Electronics Technology

Digital Electronics Technology 2019/3/11

电压传输特性

10.2 施密特触发器

10.2.1 用门电路组成的施密特触发器 施密特触发器的两个输出电压传输特性

vI

vo

VOH

vo

VT

vI

vA

VOH

vo

VT

VOL 0

VT-

VTH

VT+

VTH

当VI 1时,VO 1 。

当VI , 至VA VTH 时,进入传输 特性的放大区,故

vA

vo1

vo

使电路迅速跳变到

vo=VOL≈ 0

VA VTH (VDD

R1 VI ) VI R1 R2

VT-=VI=( 1 R1 )VTH R2

2019/3/11

由于VTH= VDD / 2,故

VT+

VDD vI

(a)同相输出

(b)反相输出

Digital Electronics Technology

2019/3/11

10.2 施密特触发器

10.2.2 集成施密特触发器

(略)

Digital Electronics Technology

2019/3/11

10.2 施密特触发器

10.2.3 施密特触发器的应用

Digital Electronics Technology

10.2 施密特触发器

10.2.1 用门电路组成的施密特触发器

VI VT VI VT

R1 (1 )VTH R2 R1 (1 )VTH R2

VT=VT+-VT- 2

R1 VTH R2

改变R1 / R2可以调节VT 、VT 和VT 但,必须R1 R2,否则有 VT 2VTH VDD;VT 0 vI 到VDD 或 到0,电路状态不变

2019/3/11

10.3 单稳态触发器

10.3.1 用门电路组成的单稳态触发器 一、积分型

1 . 原理分析

G1和G2为TTL门

* 稳态下: VI 0,VO 1, (VO1 VOH ),VA VOH ;

*VI 后,VO 0, 进入暂稳态, VO1 0, C开始放电;

*当放至 VA VTH 后,VO 1, 返回稳态;

R1< R2 (否则电路进入自锁状态,不能正常工作)

Digital Electronics Technology 2019/3/11

10.2 施密特触发器

10.2.1 用门电路组成的施密特触发器

R2 R1 vI v0 R1 R2 R1 R2

vA

当VI 0时,VO 0。

当VI , 至VA VTH 时,进入传输特性的放 大区(转折区),故

*VI 后,C重新充电至 VOH , 恢复初始态;

Digital Electronics Technology

2019/3/11

10.3 单稳态触发器

施密特触发器(Schmitt Trigger)

特点: 1、输入信号上升和下降时对应的转换电平不同;

2、内部有正反馈,使输出转换波形变得很陡 。 作用: 边沿变化缓慢的波形→边沿陡峭的矩形波;

清除→叠加在矩形波脉冲高、低电平上的噪声。

Digital Electronics Technology

2019/3/11

10.2 施密特触发器

10.2.1 用门电路组成的施密特触发器

两级反相器串接,通过分压电阻把输出端的电压反馈到输入端。

R2 vI R1 v I G1

vo1 1 1

G2 (a) 电路

vo vo

vI vI

vo vo

VTH = VDD/2 , VOH=反相器构成的施密特触发器 VDD, VOL=0,且R1< R2 图 6.2.1 用 CMOS