数字电路答案第三章 2

(完整版)数字电路与逻辑设计课后习题答案蔡良伟(第三版)

0 1 1 0

0 1 1 1

1 0 0 0

1 0 0 1

1 0 1 0

1 0 1 1

1 1 0 0

1 1 0 1

1 1 1 0

1 1 1 1

0 0 0 0

0 0 0 1

0 0 1 0

0 0 1 1

0 1 0 0

0 1 0 1

0 1 1 0

0 1 1 1

1 0 0 0

1 0 0 1

1 0 1 0

3-6

3-7

3-8

3-9

3-10

求减数的补码,然后与被减数相加即可。电路图如下:

3-11

3-12

(1)

(2)

(3)

(4)

(5)

(6)

(7)

(8)

3-13

(1)真值表:

(2)电路图

3-14

3-15

第四章习题

4-1

4-2

4-3

4-4

4-5

4-6

4-7

4-8

4-9

4-10

RSDRSJK RST

4-11

(1)转换真值表

1 1 0 1

1 1 1 0

1 1 1 1

1 0 1 0

0 0 0 0

0 0 0 1

0 0 1 0

00 11

0 1 0 0

0 1 0 1

0 1 1 0

0 1 1 1

1 0 0 0

1 0 0 1

××××

××××

××××

××××

××××

1×0×1×0×

0×0×0××1

0×0××1 1×

0×0××0×1

0××1 1×1×

数字电路第五版(康华光)课后答案

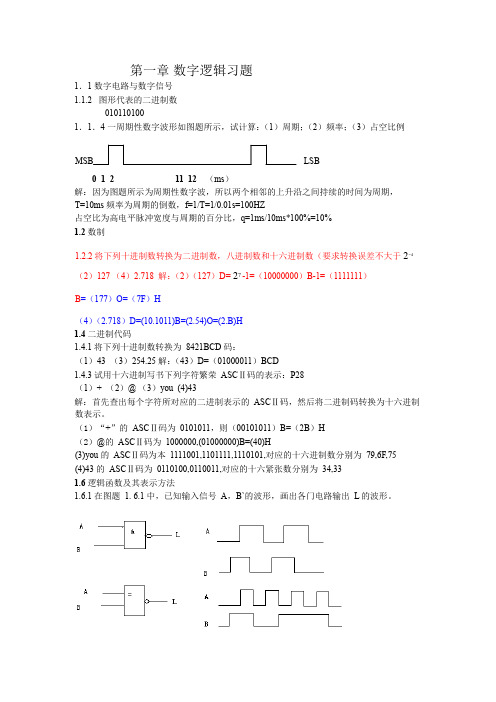

第一章数字逻辑习题1.1 数字电路与数字信号1.1.2 图形代表的二进制数0101101001.1.4 一周期性数字波形如图题所示,试计算:(1)周期;(2)频率;(3)占空比例MSB LSB0 1 2 11 12 (ms)解:因为图题所示为周期性数字波,所以两个相邻的上升沿之间持续的时间为周期,T=10ms 频率为周期的倒数,f=1/T=1/0.01s=100HZ占空比为高电平脉冲宽度与周期的百分比,q=1ms/10ms*100%=10%1.2 数制1.2.2 将下列十进制数转换为二进制数,八进制数和十六进制数(要求转换误差不大于2−4(2)127 (4)2.718解:(2)(127)D= 27 -1=(10000000)B-1=(1111111)B=(177)O=(7F)H(4)(2.718)D=(10.1011)B=(2.54)O=(2.B)H1.4 二进制代码1.4.1 将下列十进制数转换为8421BCD 码:(1)43 (3)254.25 解:(43)D=(01000011)BCD1.4.3 试用十六进制写书下列字符繁荣ASCⅡ码的表示:P28(1)+ (2)@ (3)you (4)43解:首先查出每个字符所对应的二进制表示的ASCⅡ码,然后将二进制码转换为十六进制数表示。

(1)“+”的ASCⅡ码为0101011,则(00101011)B=(2B)H(2)@的ASCⅡ码为1000000,(01000000)B=(40)H(3)you 的ASCⅡ码为本1111001,1101111,1110101,对应的十六进制数分别为79,6F,75(4)43 的ASCⅡ码为0110100,0110011,对应的十六紧张数分别为34,331.6 逻辑函数及其表示方法1.6.1 在图题1. 6.1 中,已知输入信号A,B`的波形,画出各门电路输出L 的波形。

解: (a)为与非, (b)为同或非,即异或第二章逻辑代数习题解答2.1.1 用真值表证明下列恒等式(3)A⊕ =B AB AB+ (A⊕B)=AB+AB解:真值表如下由最右边2栏可知,A⊕B与AB+AB的真值表完全相同。

数电第五版(阎石)第三章课后习题及答案

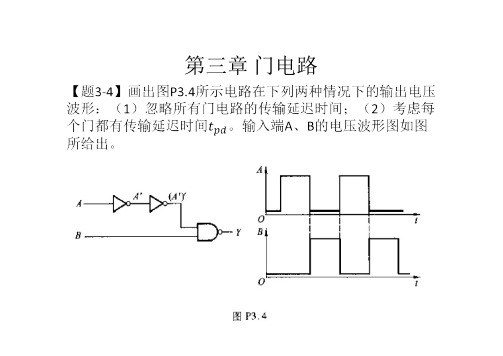

第三章门电路解:两种情况下的电压波形图如图A3.4所示。

【题3.7】试分析图3.7中各电路图的逻辑功能,写出输出的逻辑函数式。

(a )图P3.7(a )电路可划分为四个反相器电路和一个三输入端的与非门电路,如图所示。

从输入到输出逐级写出输出的逻辑函数式,'111'1'1'1)(,,,C B A D C C B B A A ''''111')(C B A C B A C B A D Y(b )图P3.7(b )电路可划分为五个反相器电路和一个或非门电路,如图所示。

从输入到输出逐级写出输出的逻辑函数式:'111''''()()YA B C A B C ABC(c )图P3.7(c )电路可划分为三个与非门电路、两个反相器电路和一个或非门电路,如图所示。

从输入到输出逐级写出输出的逻辑函数式:''')(,)(,)'(,)(G INHH EF G CD F AB E '''''()()'()'()()Y I H AB CD INH AB CD INH(d)图P3.7(d)电路可划分为两个反相器电路和两个传输门电路,如图所示。

从输入到输出逐级写出输出的逻辑函数式:'YBAAB'【题3.8】试画出图3-8(a)(b)两个电路的输出电压波形,输入电压波形如图(c)所示。

输出电压波形如右图所示:【题3.9】 在图3-21所示电路中,G 1和G 2是两个OD 输出结构的与非门74HC03,74HC03输出端MOS 管截止电流为 导通时允许的最大负载电流为这时对应的输出电压V OL (max )=0.33V 。

负载门G 3-G 5是3输入端或非门74HC27,每个输入端的高电平输入电流最大值为 ,低电平输入电流最大值为 ,试求在 、、、、并且满足 ,的情况下, 的取值的允许范围。

数字集成电路习题(第三章)

0. Explain qualitatively

4

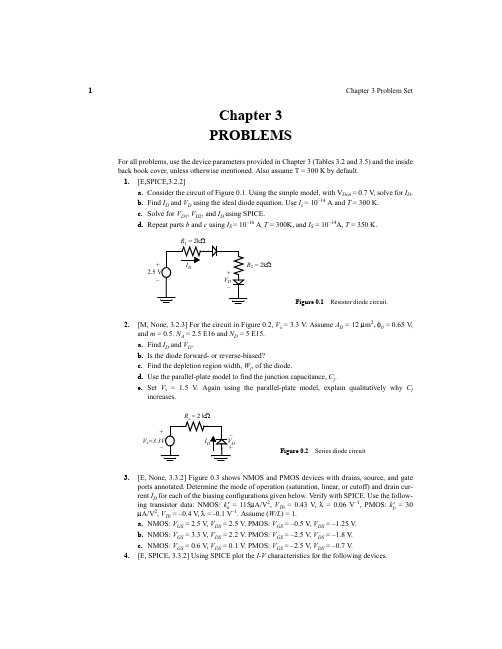

Chapter 3 Problem Set a. Write down the equations (and only those) which are needed to determine the voltage at node X. Do NOT plug in any values yet. Neglect short channel effects and assume that λp = 0. b. Draw the (approximative) load lines for both MOS transistor and resistor. Mark some of the significant points. c. Determine the required width of the transistor (for L = 0.25µm) such that X equals 1.5 V. d. We have, so far, assumed that M1 is a long-channel device. Redraw the load lines assuming that M1 is velocity-saturated. Will the voltage at X rise or fall?

Table 0.2 Measurements taken from the MOS device, at different terminal voltages.

Measurement number 1 2 3 4 5 6 7 8.

VGS (V) -2.5 1 -0.7 -2.0 -2.5 -2.5 -2.5

R1 = 2kΩ + 2.5 V – ID R2 = 2kΩ

课后习题答案_第3章_门电路

数字电子技术基础第三章习题答案3-1 如图3-63a~d所示4个TTL门电路,A、B端输入的波形如图e所示,试分别画出F1、F2、F3和F4的波形图。

略3-2 电路如图3-64a所示,输入A、B的电压波形如图3-64b所示,试画出各个门电路输出端的电压波形。

略3-3 在图3-7所示的正逻辑与门和图3-8所示的正逻辑或门电路中,若改用负逻辑,试列出它们的逻辑真值表,并说明F和A、B之间是什么逻辑关系。

答:(1)图3-7负逻辑真值表F与A、B之间相当于正逻辑的“或”操作。

(2)图3-8负逻辑真值表F与A、B之间相当于正逻辑的“与”操作。

3-4 试说明能否将与非门、或非门、异或门当做反相器使用?如果可以,各输入端应如何连接?答:三种门经过处理以后均可以实现反相器功能。

(1)与非门: 将多余输入端接至高电平或与另一端并联;(2)或非门:将多余输入端接至低电平或与另一端并联;(3) 异或门:将另一个输入端接高电平。

3-5 为了实现图3-65所示的各TTL 门电路输出端所示的逻辑关系,请合理地将多余的输入端进行处理。

答:a )多余输入端可以悬空,但建议接高电平或与另两个输入端的一端相连;b)多余输入端接低电平或与另两个输入端的一端相连;c) 未用与门的两个输入端至少一端接低电平,另一端可以悬空、接高电平或接低电平;d )未用或门的两个输入端悬空或都接高电平。

3-6 如要实现图3-66所示各TTL 门电路输出端所示的逻辑关系,请分析电路输入端的连接是否正确?若不正确,请予以改正。

答:a )不正确。

输入电阻过小,相当于接低电平,因此将Ω50提高到至少2K Ω。

b) 不正确。

第三脚V CC 应该接低电平。

c )不正确。

万用表一般内阻大于2K Ω,从而使输出结果0。

因此多余输入端应接低电平,万用表只能测量A 或B 的输入电压。

3-7 (修改原题,图中横向电阻改为6k Ω,纵向电阻改为3.5 k Ω,β=30改为β=80) 为了提高TTL 与非门的带负载能力,可在其输出端接一个NPN 晶体管,组成如图3-67所示的开关电路。

万里学院-数字电子技术基础-第三章习题及参考答案

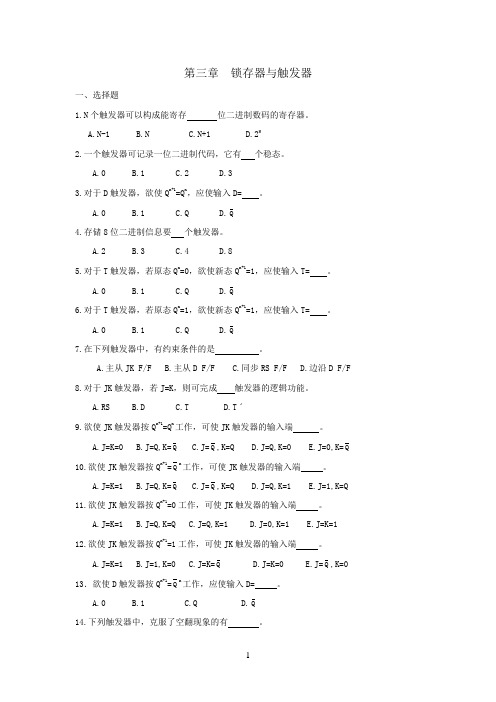

第三章锁存器与触发器一、选择题1.N个触发器可以构成能寄存位二进制数码的寄存器。

A.N-1B.NC.N+1D.2N2.一个触发器可记录一位二进制代码,它有个稳态。

A.0B.1C.2D.33.对于D触发器,欲使Q n+1=Q n,应使输入D= 。

A.0B.1C.QD.Q4.存储8位二进制信息要个触发器。

A.2B.3C.4D.85.对于T触发器,若原态Q n=0,欲使新态Q n+1=1,应使输入T= 。

A.0B.1C.QD.Q6.对于T触发器,若原态Q n=1,欲使新态Q n+1=1,应使输入T= 。

A.0B.1C.QD.Q7.在下列触发器中,有约束条件的是。

A.主从JK F/FB.主从D F/FC.同步RS F/FD.边沿D F/F8.对于JK触发器,若J=K,则可完成触发器的逻辑功能。

A.RSB.DC.TD.Tˊ9.欲使JK触发器按Q n+1=Q n工作,可使JK触发器的输入端。

A.J=K=0B.J=Q,K=QC.J=Q,K=QD.J=Q,K=0E.J=0,K=Q10.欲使JK触发器按Q n+1=Q n工作,可使JK触发器的输入端。

A.J=K=1B.J=Q,K=QC.J=Q,K=QD.J=Q,K=1E.J=1,K=Q11.欲使JK触发器按Q n+1=0工作,可使JK触发器的输入端。

A.J=K=1B.J=Q,K=QC.J=Q,K=1D.J=0,K=1E.J=K=112.欲使JK触发器按Q n+1=1工作,可使JK触发器的输入端。

A.J=K=1B.J=1,K=0C.J=K=QD.J=K=0E.J=Q,K=0 13.欲使D触发器按Q n+1=Q n工作,应使输入D= 。

A.0B.1C.QD.Q14.下列触发器中,克服了空翻现象的有。

A.边沿D触发器B.主从RS触发器C.同步RS触发器D.主从JK触发器15.下列触发器中,没有约束条件的是。

A.基本RS触发器B.主从RS触发器C.同步RS触发器D.边沿D触发器16.为实现将JK触发器转换为D触发器,应使。

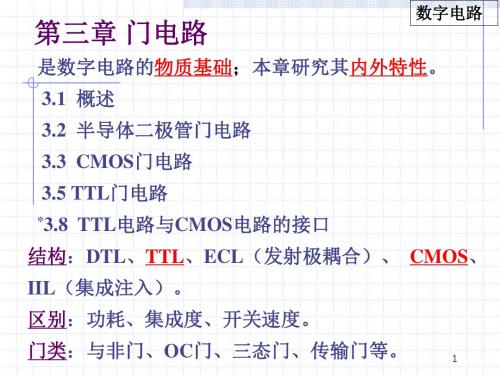

数字电路精简 第3章门电路.

3.2.2二极管与门

5V

表3.2.2

电平分析 AB Y L L L H

3.2 二极管开关特性

正逻辑 AB 00 01 10 11 Y 0 0 0 1 负逻辑

AB Y

11 10 01 00 1 1 1 0

图3.2.5 正逻辑分析: Y A B 表3.2.1 有低出低全高出高

uA uB UY

Y A B 负逻辑分析: Y A B

正逻辑的“或”等于负逻辑 的“ 与” 或门的工作波形(口诀)

A 0 1 0 1 0 1 0 1 0 D1通 B 0 1 1 0 0 1 1 0 0 F 0 1 1 1 0 1 1 1 0 特点:简单,高低电平不统一 4

D2止 D2通

夹断区: UGS< Uth (开启电 3.3.1MOS管的开关特性压) , ID=0 ,D、S间相当 +VDD 于开关断开(ROFF109 )。

发射区高 掺杂浓度 退存储 效应tS

J I 是电子空 C 穴复合过程 B+ P

JE

R

VBB R

几十K

R

3.3 CMOS门电路

第三章 门电路

uI

ID

Uo

>Uth

t

D 漏

Ui

<Uth

G

栅

S 源

N M OS

uO

0V

图3.3.4 MOS 管开关特性图 可变电阻区:UGS>Uth, UDS 特点:有延迟,MOS管 0V , D、S间相当于开关 的高、低电平幅度大、省 闭合(RON1K ) 5 电等优点。

数电-带答案

第一章 逻辑代数基础 例题1.与(10000111)BCD 相等的十进制数是87, 二进制数是1010111 十六进制数是57,2.AB+CD=0(约束项)求 的最简与或表达式。

解:D C A C B A Z +=,见图1-1, 得3.若F(A,B,C,D)=∑m(0,1,2,3,4,7,15)的函数可化简为: 则可能存在的约束项为( 3 )。

见图1-21.逻辑函数式Y A B C D =++()的反演式为 D C B A + 2. 在下列不同进制的数中,数值最大的数是( D )1051A.() .101010B 2() 163E C.() D.(01011001)8421BCD 码 3、用卡诺图化简下式为最简与或式。

D C B A ++ Y(A,B,C,D)= ∑m(0,2,4,5,6,8,9)+ ∑d(10,11,12,13,14,15) 4.已知F ABC CD =+选出下列可以肯定使F=0的情况( D )A. A=0,BC=1B. B=C=1C. D=0,C=1D. BC=1,D=1 5、是8421BCD 码的是( B )。

A 、1010 B C 、1100 D 、11016、欲对全班43个学生以二进制代码编码表示,最少需要二进制码的位数是( B )。

A 、5B 、6C 、8D 、437、逻辑函数F(A,B,C) = AB+B C+C A 的最小项标准式为( D )。

A 、F(A,B,C)=∑m(0,2,4)B 、F(A,B,C)=∑m(1,5,6,7)C 、F(A,B,C)=∑m (0,2,3,4)D 、F(A,B,C)=∑m(3,4,6,7)Z A BC A B AC D =++Z Z AC AC =+()B C D C D ++1..2..3..4..AC A DA C AB A D A B A B B C++++8、用代数法化简下式为最简与或式。

A+CC B BC C B A BCD A A F ++++=判断题1.若两个函数具有不同的真值表,则两个逻辑函数必然不相等。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

判断是否存在竞争冒险现象,就是判别表达式中是否存在AAF=或AAF+=,判断结论如下:当BCD=011时,表达式中存在AAF+=的情况,电路会出现竞争冒险现象。

当BD=10或ABD=011时,表达式中存在CCF+=的情况,电路会出现竞争冒险现象。

当AC=01=时,表达式中存在DDF+=的情况,电路会出现竞争冒险现象。

习题3.7习题3.7图(a)和(b)电路有无竞争冒险现象?若有,请说明出现冒险的输入条件,并修改设计。

画出无冒险的逻辑图。

解:(1)分析习题3.7图(a)所示电路,得到逻辑表达式为:F=)(BCABDAD++⋅,若输入信号A=B=1,则有F=DD,因此电路有竞争冒险。

增加冗余项后的逻辑表达式为:F=ABBCABDAD+++⋅)(,修改后的逻辑图如图习题3.7图(c)所示。

(2)分析习题3.7图(b)所示电路,其表达式为:F=))((BDDACBA+++。

若输入信号ACD=011,则有F=BB+,电路有竞争冒险。

若输入信号BCD=010,则有F=AA+,电路有竞争冒险。

增加冗余项后的逻辑表达式为:F=DCBCDABDDACBA+++++))((,修改后的逻辑图如图习题3.7图(d)所示。

习题3.8 试设计一个无冒险的电路,其工作条件是:当输入4位码为∑)15,14,13,5,4,2,0(m时显示绿灯,输入其余码时显示红灯。

解:(1)根据题意设4位码ABCD为输入变量,设绿灯和红灯分别为输出变量F1、F2,输出取值为1表示灯亮,否则灯不亮。

(2)由于题目要求比较明确,可以直接作函数卡诺图,化简函数,得到最简与或式,如习题3.8图(a)所示。

为了使电路无冒险,应考虑增加冗余项,如习题3.8图(b)所示,求得无冒险的与或式。

又由于输出变量F1和F2互为反函数,因此只求一个输出函数的表达式即可。

习题3.8图1 2(c)ABD D C A ABC D C B C B A D B A F +++++=1, 12F F = (4)由逻辑表达式画出逻辑图如习题3.8图(b )所示。

习题3.9 按习题3.2已知条件完成下列要求: (1)试用最少的与非门设计此电路。

(2)检查电路是否存在竞争冒险?若存在,则讨论在什么时刻可能出现冒险现象。

(3)用增加冗余项的办法来消除冒险现象。

解:参考习题3.2的解题过程,分析卡诺图如习题3.2图(a )所示,所求函数是最简与或式,且无竞争冒险。

习题3.10 用VHDL 硬件描述语言设计一个10输入的优先编码器。

解:优先编码器的文件名为xiti3_10.vhd ,输入信号定义为ina (9)~ina (0),且为高有效,ina (9)的优先级别最高,ina (0)的优先级别最低;输出信号定义为outy (3)~outy (0),且为高有效编码输出。

LIBRARY IEEE;USE IEEE.std_logic_1164.all; ENTITY xiti3_10 ISPORT (ina: IN STD_LOGIC_VECTOR(9 DOWNTO 0);outy: OUT STD_LOGIC_VECTOR(3 DOWNTO 0) );END xiti3_10;ARCHITECTURE rtl OF xiti3_10 IS BEGINPROCESS(ina) BEGINIF(ina(9)='1')THEN outy<="1001";ELSIF(ina(8)='1')THEN outy<="1000";ELSIF(ina(7)='1')THEN outy<="0111";ELSIF(ina(6)='1')THEN outy<="0110"; ELSIF(ina(5)='1')THEN outy<="0101"; ELSIF(ina(4)='1')THEN outy<="0100"; ELSIF(ina(3)='1')THEN outy<="0011"; ELSIF(ina(2)='1')THEN outy<="0010"; ELSIF(ina(1)='1')THEN outy<="0001"; ELSEouty<="0000"; END IF; END PROCESS; END rtl;习题3.11 用VHDL 行为描述语言设计一个3线—8线译码器。

解:3-8线译码器的文件名为xiti3_11.vhd ,输入信号定义为inp (2)~inp (0);输出信号定义为outp (7)~outp (0),高有效输出。

LIBRARY IEEE;USE IEEE.std_logic_1164.all; USE IEEE.std_logic_unsigned.all; ENTITY xiti3_11 ISPORT (inp:in std_logic_vector(2 downto 0);outp:out bit_vector(7 downto 0));END xiti3_11;ARCHITECTURE behave OF xiti3_11 IS BEGINoutp(0)<='1' WHEN inp="000" ELSE '0'; outp(1)<='1' WHEN inp="001" ELSE '0'; outp(2)<='1' WHEN inp="010" ELSE '0'; outp(3)<='1' WHEN inp="011" ELSE '0'; outp(4)<='1' WHEN inp="100" ELSE '0'; outp(5)<='1' WHEN inp="101" ELSE '0'; outp(6)<='1' WHEN inp="110" ELSE '0'; outp(7)<='1' WHEN inp="111" ELSE '0'; END behave;习题3.12 设计一个译码显示电路。

显示器为共阳极七段LED 字形显示器,显示译码器的输入G 4G 3G 2G 1为循环码。

(1)设计循环码显示译码器,写出输出函数a ,b ,c …g 的表达式。

(2)按共阳极显示器的要求,显示译码器输出a ,b ,c …g 和显示器相连时应取的逻辑电平是什么?(3)画出显示译码器和显示器的接线图。

解:(1)译码器的输入为G 4G 3G 2G 1,输出为a ,b ,c …g ,根据设计要求得到真值表如表习题3.12表所示。

化简得到输出逻辑表达式为:12301301230231201230123013123023012301230230230123023123123013023123012013G G G G G G g G G G G G G G G G f G G G G G G G G G G G G G G G G G e G G G G G G G G G G G G G G d G G G G G G G G G G c G G G G G G G G G b G G G G G G G G G a +=++=++++=+++=++=++=++=(2)如果是共阳极显示器,显示译码器输出a ,b ,c …g 应为低电平有效,且与显示器的阴极相连。

(3)显示译码器的逻辑电路图按逻辑表达式a、b、c、d、e、f、g连接,连接图略。

习题3.13 用VHDL描述语言设计一个BCD码显示译码器,并且显示发光管是共阳极。

解:l LIBRARY IEEE;USE IEEE.std_logic_1164.all;USE IEEE.std_logic_unsigned.all;ENTITY xiti3_13 ISPORT(inp:in std_logic_vector(3 downto 0); --inp是输入码a,b,c,d,e,f,g:out std_logic); -- a,b,c,d,e,f,g是低有效输出END xiti3_13;ARCHITECTURE beh OF xiti3_13 ISBEGINPROCESS(inp)VARIABLE temout :std_logic_vector(0 to 6);BEGINCASE inp ISWHEN "0000"=> temout:= "0000001";WHEN "0001"=> temout:= "1001111";WHEN "0011"=> temout:= "0010010";WHEN "0010"=> temout:= "0000110";WHEN "0110"=> temout:= "1001100";WHEN "0111"=> temout:= "0100100";WHEN "0101"=> temout:= "1100000";WHEN "0100"=> temout:= "0001111";WHEN "1100"=> temout:= "0000000";WHEN "1101"=> temout:= "0001100";WHEN "1111"=> temout:= "0000100";WHEN "1110"=> temout:= "1100000";WHEN "1010"=> temout:= "1110010";WHEN "1011"=> temout:= "1000010";WHEN "1001"=> temout:= "0110000";WHEN "1000"=> temout:= "0111000";WHEN others =>temout:= "1111111";END CASE;a<=temout(0);b<=temout(1);c<=temout(2);d<=temout(3);e<=temout(4);f<=temout(5);g<=temout(6);END PROCESS;END beh;习题3.14 试设计一个将8421BCD码转换成余3码的电路。