STM32ADC采样频率的确定.pdf

STM32ADCDMA采样时间计算

STM32ADCDMA采样时间计算在STM32上,ADC的采样时间取决于以下几个因素:1. ADC时钟频率(ADC Clock Frequency):选择合适的时钟频率可以提高采样速度。

2. ADC分辨率(ADC Resolution):ADC的分辨率越高,采样时间越长。

3. ADC转换周期(ADC Conversion Cycle):每次转换的时间,包括单次转换和连续转换。

首先,我们需要确定ADC时钟频率。

在STM32中,ADC的时钟频率可以通过设置RCC_CCFGR寄存器的相应位来选择。

这个时钟频率决定了每个ADC转换周期所花费的时间。

其次,我们需要确定ADC分辨率。

在STM32中,ADC的分辨率可以通过设置ADC_CR1寄存器的相应位来选择。

通常有8位、10位、12位和16位等选项。

分辨率越高,则每次转换所需的时间越长。

最后,我们需要确定ADC转换周期。

在STM32中,默认情况下每次转换只需要一个转换周期。

如果需要连续采样,则还需要考虑连续转换模式。

计算ADC采样时间的公式为:ADC采样时间=ADC转换周期×ADC分辨率/ADC时钟频率例如,假设ADC转换周期为10个时钟周期,分辨率为12位(4096个转换步骤),时钟频率为10MHz,则:ADC采样时间=10×4096/10,000,000≈4.096μs在使用DMA进行数据传输时,可以将ADC的转换结果直接传输到SRAM等目标内存区域,从而减少CPU的负担和数据传输的延迟。

总结起来,通过合理设置ADC时钟频率、分辨率和转换周期,以及结合DMA进行数据传输,可以实现高效的数据采样和处理。

STM32多通道ADC采集详解(DMA模式和非DMA模式)

STM32多通道ADC采集详解(DMA模式和非DMA模式)在非DMA模式下,ADC采集的数据是通过CPU直接读取的,采集效率相对较低,但是编程相对简单。

首先,需要初始化ADC模块的工作模式(单通道、多通道等)和采样时间。

然后,使能ADC模块,并配置所需的通道和采样时间。

接着,设置采样序列,指定要采集的通道和相应的排列顺序。

在采集数据时,首先需要设置ADC转换模式和采样时间,然后开始转换,并等待转换完成。

转换完成后,通过读取ADC_DR寄存器可以获取转换结果。

如果需要采集多个通道的数据,可以通过设置ADCSQR中的SQx位来启动下一次转换。

在DMA模式下,ADC采集的数据是通过DMA控制器传输到指定的内存区域,采集效率较高,适合数据量较大的应用场景。

与非DMA模式相比,DMA模式下的配置需要额外设置DMA控制器的工作模式(单次传输、循环传输等)和传输数据的目的地地址。

在采集数据前,需要设置DMA传输的目的地地址,并使能DMA传输。

在开启ADC转换后,DMA控制器会根据设置的目的地地址来自动传输数据,无需CPU干预。

采集完成后,CPU可以通过检查DMA传输完成标志位来判断数据是否已传输完毕。

总结:

使用非DMA模式的ADC采集相对简单而容易上手,适用于数据量较小且对实时性要求不高的应用场景。

DMA模式下的ADC采集效率更高,适用于数据量较大且对实时性要求较高的应用场景。

无论是DMA模式还是非DMA模式,都需要根据具体的应用需求来选择合适的模式。

在使用DMA模式时,还需要注意合理设置DMA传输的目的地地址和传输模式,以充分发挥DMA的优势。

STM32CUBEMX配置教程(十二)STM32的定时器触发的固定频率ADC采样(使用DMA)

STM32CUBEMX配置教程(十二)STM32的定时器触发的固定频率ADC采样(使用DMA)本教程将向您展示如何使用STM32CubeMX配置定时器触发的固定频率ADC采样,并使用DMA进行数据传输。

此配置可以用于您需要按照固定频率对模拟信号进行采样的应用中。

在开始之前,请确保已安装好STM32CubeMX和相应的IDE(如Keil、IAR等),并且您已熟悉STM32CubeMX的基本使用方法。

以下是配置步骤:1. 打开STM32CubeMX,并选择您的目标MCU型号。

2. 在"Pinout & Configuration"选项卡中,配置定时器和ADC引脚。

a.选择一个定时器,并设置其时钟源和频率。

您可以选择任何一个可用的定时器来触发ADC采样。

b.配置ADC引脚,将其连接到您的模拟信号源。

3. 在"Configuration"选项卡中,配置ADC。

a.启用ADC和DMA控制器。

b.配置ADC分辨率,采样时间和采样周期。

这些参数取决于您的应用需求。

c. 在"Mode"选项中,选择"Continuous Conversion Mode"。

这样ADC将会不断地根据定时器触发进行采样。

d. 启用"DMA Continuous Requests"。

这样当ADC完成一次采样后,DMA控制器将自动将数据传输到内存中。

4. 在"NVIC Settings"选项卡中,启用DMA和ADC中断。

5. 在"Project"选项卡中,选择生成代码所需的IDE和工程路径。

然后单击"Generate Code"按钮生成代码。

现在您已成功配置了定时器触发的固定频率ADC采样,并使用DMA进行数据传输。

您可以在生成的代码中初始化和启用各个模块,并编写相应的中断处理函数来处理DMA和ADC中断。

STM32 ADC 采样速率计算

stm32 ADC采样速率的问题RCC_ADCCLKConfig(RCC_PCLK2_Div8); ADC_RegularChannelConfig(ADC1, ADC_Channel_11, 1, ADC_SampleTime_55Cycles5); 系统时钟72M,以上两句是不是ADC时钟设置为9M,然后用55.5个采用周期?那ADC就是55.5*1/9us,采集一次什么?那ADC最快和最慢采样速率...展开1,ADC时钟是设为9M2,ADC总转换时间=采样时间+12.5个ADC时钟周期(信号量转换时间),而采样时间由寄存器设定,最低1.5ADC周期,最大239.5ADC周期,也就是你程序中设置的55.5个采样周期。

所以ADC一次采样的总采样时间是55.5+12.5=68个ADC周期,也就是68/9 us3,所以,总采样时间最快就是1.5+12.5个ADC周期,最慢就是239.5+12.5个ADC周期。

至于采样速率,是跟你的程序是有关的,比如ADC采样时间设定为最快,但你可以设定1s采一次,那采样速率仍是1;再比如你开启扫描模式,跟单次转换又不一样总结(lee):1、CLK_ADC = PCLK2/ADC_DIV , ADC_DIV 由程序设定。

2、TIME_ADC_CONVERT = TIME_SAMPLE + TIME_SIGNAL_CONVERT1.5 <= TIME_SAMPLE <= 239.5 ,TIME_SAMPLE是在配置ADC的时候程序写入的(根据实际需要来设置),例如上面例子中设置的事55.5 .TIME_SIGNAL_CONVERT(最低12.5个周期,硬件因素决定,无法改变)3、ADC转换时间 = CLK_ADC / TIME_ADC_CONVERT4、ADC的时钟最高为14M,如果PCLK2 为72M,那么 ADC的时钟最高只能设置成12M(72 M 6 分频)此时ADC的转换速率为12M/( 12.5 +1.5 ),没有1M。

STM32 ADC采样频率的确定

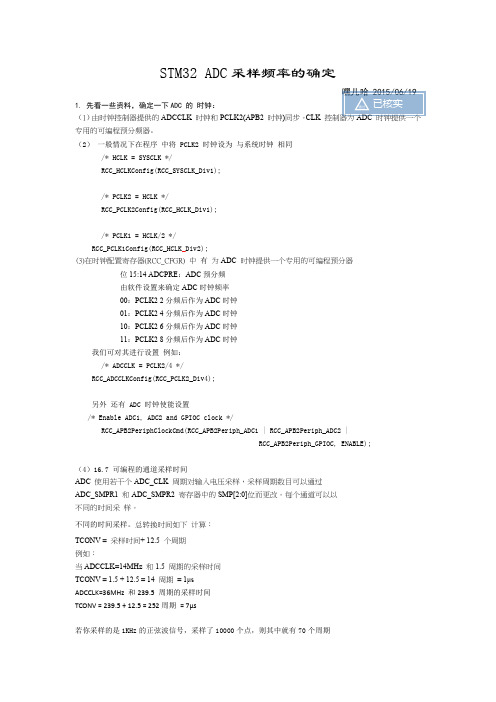

STM32 ADC 采样频率的确定 嘿儿哈2015/06/19 1. 先看一些资料,确定一下ADC 的 时钟:(1)由时钟控制器提供的ADCCLK 时钟和PCLK2(APB2 时钟)同步。

CLK 控制器为ADC 时钟提供一个专用的可编程预分频器。

(2) 一般情况下在程序 中将 PCLK2 时钟设为 与系统时钟 相同/* HCLK = SYSCLK */RCC_HCLKConfig(RCC_SYSCLK_Div1);/* PCLK2 = HCLK */RCC_PCLK2Config(RCC_HCLK_Div1);/* PCLK1 = HCLK/2 */RCC_PCLK1Config(RCC_HCLK _Div2);(3)在时钟配置寄存器(RCC_CFGR) 中 有 为ADC 时钟提供一个专用的可编程预分器位15:14 ADCPRE :ADC 预分频由软件设置来确定ADC 时钟频率00:PCLK2 2分频后作为ADC 时钟01:PCLK2 4分频后作为ADC 时钟10:PCLK2 6分频后作为ADC 时钟11:PCLK2 8分频后作为ADC 时钟我们可对其进行设置 例如:/* ADCCLK = PCLK2/4 */RCC_ADCCLKConfig(RCC_PCLK2_Div4);另外 还有 ADC 时钟使能设置/* Enable ADC1, ADC2 and GPIOC clock */RCC_APB2PeriphClockCmd(RCC_APB2Periph_ADC1 | RCC_APB2Periph_ADC2 |RCC_APB2Periph_GPIOC, ENABLE);(4)16.7 可编程的通道采样时间ADC 使用若干个ADC_CLK 周期对输入电压采样,采样周期数目可以通过ADC_SMPR1 和ADC_SMPR2 寄存器中的SMP[2:0]位而更改。

每个通道可以以不同的时间采 样。

不同的时间采样。

stm32f4adc采样频率计算

STM32F4系列的ADC(模拟数字转换器)的采样频率主要取决于系统时钟频率以及ADC的预分频器(prescaler)和通道选择器(resolution)的设置。

ADC的采样频率可以按照以下公式进行计算:

```scss

ADC_Sampling_Frequency = ADC_Clock_Frequency / (ADC_Prescaler + 1) / ADC_Resolution

```

其中:

* `ADC_Clock_Frequency` 是系统时钟频率,对于STM32F4系列,这通常为84MHz或168MHz。

* `ADC_Prescaler` 是ADC预分频器的值,这个值可以根据需要进行设置,范围是0到63。

如果预分频器设置为0,那么ADC的时钟频率等于系统时钟频率;如果设置为63,那么ADC的时钟频率就是系统时钟频率除以64。

* `ADC_Resolution` 是ADC的分辨率,可以设置为12位(即ADC_Resolution为12)或其他位数的分辨率。

在12位分辨率下,ADC的通道选择器(resolution)的值是12。

因此,如果你想计算12位分辨率下,系统时钟频率为84MHz,预分频器为63的ADC的采样频率,你可以这样做:

```scss

ADC_Sampling_Frequency = 84MHz / (63 + 1) / 12 = 1.024MHz

```

这意味着ADC的采样频率为1.024MHz。

请注意,这些计算假定ADC的其他设置(如通道选择器、比较器、DMA等)不会影响ADC的采样频率。

这些设置可能会影响实际的采样频率。

stm32f4adc采样频率计算

stm32f4adc采样频率计算一、STM32F4ADC简介STM32F4ADC(Analog-to-Digital Converter,模拟-数字转换器)是STM32F4系列微控制器内置的一款高性能、高精度的模拟转换器。

它能够将连续的模拟信号转换为离散的数字信号,广泛应用于各种传感器数据采集、信号处理等领域。

二、采样频率计算方法在实际应用中,采样频率是一个非常重要的参数。

根据奈奎斯特定理,采样频率必须大于信号最高频率的两倍,才能保证信号的完整性,避免发生混叠。

1.确定ADC转换位数首先,需要确定ADC的转换位数。

一般来说,转换位数越高,采样精度越高,但同时也会增加数据处理和存储的负担。

常见的ADC转换位数有8位、10位、12位等。

2.计算最大模拟电压根据ADC的位数和电源电压,可以计算出ADC的最大模拟电压。

例如,对于12位ADC,最大模拟电压为电源电压的一半(即2^12=4095)。

3.计算采样频率采样频率等于ADC的最大转换速度除以最大模拟电压。

ADC的最大转换速度通常在数据手册中会有说明。

例如,如果最大转换速度为100MSPS(百万次每秒),则采样频率计算公式为:采样频率= 100MSPS / 4095 = 24.4kHz三、注意事项1.考虑到STM32F4ADC的采样速率、模拟输入范围等因素,合理选择ADC的转换位数和采样频率。

2.确保采样频率大于信号最高频率的两倍,避免信号混叠。

3.在实际应用中,可以根据需求调整采样频率,以达到最佳的性能和功耗平衡。

4.考虑到ADC的分辨率和电源电压,合理设置ADC的参考电压和偏置电压。

四、总结本文介绍了STM32F4ADC的简介、采样频率的计算方法以及注意事项。

通过合理选择ADC的转换位数、采样频率等参数,可以充分发挥STM32F4ADC的高性能和实用性,为各种传感器数据采集和信号处理应用提供可靠的支持。

STM32 ADC采样时间、采样周期、采样频率计算方法

STM32 ADC 采样时间、采样周期、采样频率计算

方法

ADC 转换就是输入模拟的信号量,单片机转换成数字量。

读取数字量必须等转换完成后,完成一个通道的读取叫做采样周期。

采样周期一般来说=转换时间+读取时间。

而转换时间=采样时间+12.5 个时钟周期。

采样时间是你通过寄存器告诉STM32 采样模拟量的时间,设置越长越精确

一STM32 ADC 采样频率的确定

1. :先看一些资料,确定一下ADC 的时钟:

(1),由时钟控制器提供的ADCCLK 时钟和PCLK2(APB2 时钟)同步。

CLK

控制器为ADC 时钟提供一个专用的可编程预分频器。

(2) 一般情况下在程序中将PCLK2 时钟设为与系统时钟相同

/* HCLK = SYSCLK */

RCC_HCLKConfig(RCC_SYSCLK_Div1);。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

STM32 ADC 采样频率的确定 嘿儿哈

2015/06/19 1. 先看一些资料,确定一下ADC 的 时钟:

(1)由时钟控制器提供的ADCCLK 时钟和PCLK2(APB2 时钟)同步。

CLK 控制器为ADC 时钟提供一个专用的可编程预分频器。

(2) 一般情况下在程序 中将 PCLK2 时钟设为 与系统时钟 相同

/* HCLK = SYSCLK */

RCC_HCLKConfig(RCC_SYSCLK_Div1);

/* PCLK2 = HCLK */

RCC_PCLK2Config(RCC_HCLK_Div1);

/* PCLK1 = HCLK/2 */

RCC_PCLK1Config(RCC_HCLK _Div2);

(3)在时钟配置寄存器(RCC_CFGR) 中 有 为ADC 时钟提供一个专用的可编程预分器

位15:14 ADCPRE :ADC 预分频

由软件设置来确定ADC 时钟频率

00:PCLK2 2分频后作为ADC 时钟

01:PCLK2 4分频后作为ADC 时钟

10:PCLK2 6分频后作为ADC 时钟

11:PCLK2 8分频后作为ADC 时钟

我们可对其进行设置 例如:

/* ADCCLK = PCLK2/4 */

RCC_ADCCLKConfig(RCC_PCLK2_Div4);

另外 还有 ADC 时钟使能设置

/* Enable ADC1, ADC2 and GPIOC clock */

RCC_APB2PeriphClockCmd(RCC_APB2Periph_ADC1 | RCC_APB2Periph_ADC2 |

RCC_APB2Periph_GPIOC, ENABLE);

(4)16.7 可编程的通道采样时间

ADC 使用若干个ADC_CLK 周期对输入电压采样,采样周期数目可以通过

ADC_SMPR1 和ADC_SMPR2 寄存器中的SMP[2:0]位而更改。

每个通道可以以

不同的时间采 样。

不同的时间采样。

总转换时间如下 计算:

TCONV = 采样时间+ 12.5 个周期

例如:

当ADCCLK=14MHz 和1.5 周期的采样时间

TCONV = 1.5 + 12.5 = 14 周期 = 1μs

ADCCLK=36MHz 和239.5 周期的采样时间

TCONV = 239.5 + 12.5 = 252周期 = 7μs

若你采样的是1KHz 的正弦波信号,采样了10000个点,则其中就有70个周期

SMPx[2:0]:选择通道x的采样时间

这些位用于独立地选择每个通道的采样时间。

在采样周期中通道选择位必须保持不变。

000:1.5周期100:41.5周期

001:7.5周期101:55.5周期

010:13.5周期110:71.5周期

011:28.5周期111:239.5周期

注:

– ADC1的模拟输入通道16和通道17在芯片内部分别连到了温度传感器和VREFINT。

– ADC2的模拟输入通道16和通道17在芯片内部连到了VSS。

2.具体分析如下:

(1)我们的输入信号是50Hz (周期为20ms),初步定为1周期200个采样点,(注:一周期最少采20个点,即采样率最少为1k),每2个采样点间隔为 20ms /200 = 100 us

ADC可编程的通道采样时间我们选最小的 1.5 周期,则 ADC采样周期一周期大小为

100us /1.5=66us 。

ADC 时钟频率为 1/66us =15 KHz。

ADC可编程的通道采样时间我们选71.5 周期,则 ADC采样周期一周期大小为

(100us /71.5)。

ADC 时钟频率为 7.15MHz。

(2)接下来我们要确定系统时钟:我们用的是 8M Hz 的外部晶振做时钟源(HSE),估计得经过 PLL倍频 PLL 倍频系数分别为2的整数倍,最大72 MHz。

为了提高数据计算效率,我们把系统时钟定为72MHz,(PLL 9倍频)。

则 PCLK2=72MHz,PCLK1=36MHz;

我们通过设置时钟配置寄存器(RCC_CFGR) 中有为ADC 时钟提供一个专用的可编程预分器,将PCLK2 8 分频后作为ADC 的时钟,则可知ADC 时钟频率为9MHz

从手册可知:ADC 转换时间:

STM32F103xx 增强型产品:ADC 时钟为56MHz 时为1μs(ADC 时钟为72MHz 为1.17μs)(3)由以上分析可知:不太对应,我们重新对以上中内容调整,提出如下两套方案:

方案一:我们的输入信号是50Hz (周期为20ms),初步定为1周期2500个采样点,(注:一周期最少采20个点,即采样率最少为1k),每2个采样点间隔为 20ms /2500 = 8 us ADC可编程的通道采样时间我们选71.5 周期,则 ADC采样周期一周期大小为

8us /71.5 。

ADC 时钟频率约为 9 MHz。

将PCLK2 8 分频后作为ADC 的时钟,则可知ADC 时钟频率为9MHz

方案二:我们的输入信号是50Hz (周期为20ms),初步定为1周期1000个采样点,(注:一周期最少采20个点,即采样率最少为1k),每2个采样点间隔为 20ms /1000= 20 us ADC可编程的通道采样时间我们选239.5周期,则 ADC采样周期一周期大小为

20us /239.5 。

ADC 时钟频率约为 12 MHz。

将PCLK2 6 分频后作为ADC 的时钟,则可知ADC 时钟频率为12MHz。