飞思卡尔单片机的讲解

飞思卡尔单片机快速上手指南说明书

Freescale Semiconductor, Inc.Document Number: 用户指南 Rev. 0, 09/2014Confidentiality statement, as appropriate to document/part status.___________________________________________________________________飞思卡尔单片机快速上手指南作者:飞思卡尔半导体IMM FAE 团队飞思卡尔半导体是全球领先的单片机供应商,其单片机产品包含多种内核,有数百个系列。

为支持用户使用这些产品,飞思卡尔提供了丰富的网站资源、文档及软硬件工具,另外,我们还有众多的第三方合作伙伴及公共平台的支持。

对于不熟悉飞思卡尔产品和网站的初学者来说,了解和使用这些资源这无疑是一个令人望而生畏的浩瀚工程。

本指南的目的,就是给初学者提供一个指导,让他们不被这些海量信息淹没;用户根据本指导提供的操作步骤,能迅速找到所需的资源,了解如何使用相关的工具。

在本指南中,我们以飞思卡尔的新一代Kinetis 单片机K22系列为例,介绍了如何获取与之相关的资源,如何对其进行软硬件设计和开发。

实际上,这些方法也适用于其它的单片机系列。

当然,对于其它有较多不同之处的产品,我们也会继续推出相应的文档,供广大用户参考。

目录1 如何获取技术资料与支持 ..........................................................2 2 如何选择产品、申请样片及购买少量芯片和开发工具 ........... 93 飞思卡尔单片机的开发环境、开发工具和生态系统 ............. 224 如何阅读飞思卡尔的技术文档 ................................................ 45 5 飞思卡尔单片机硬件设计指南 ................................................ 55 6飞思卡尔单片机软件开发指南 (67)飞思卡尔单片机快速上手指南, Rev. 1, 09/20142Freescale Semiconductor, Inc.1 如何获取技术资料与支持1.1 概述当用户使用飞思卡尔单片机芯片时,如何获取芯片的数据手册(Datasheet )、参考设计(Reference Manual )和官方例程等资源呢?另外当用户遇到了技术问题该如何获得帮助和解答呢?这里以Kinetis 的K22系列芯片为例为大家介绍如何解决这些问题。

飞思卡尔单片机 ECT学习资料

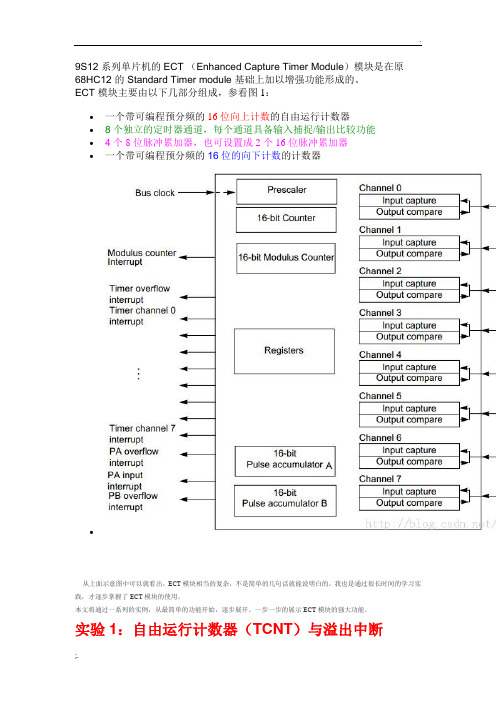

9S12 系列单片机的ECT (Enhanced Capture Timer Module)模块是在原68HC12 的 Standard Timer module 基础上加以增强功能形成的。

ECT 模块主要由以下几部分组成,参看图1:•一个带可编程预分频的16位向上计数的自由运行计数器•8个独立的定时器通道,每个通道具备输入捕捉/输出比较功能•4个8位脉冲累加器,也可设置成2个16位脉冲累加器•一个带可编程预分频的16位的向下计数的计数器•从上面示意图中可以就看出,ECT 模块相当的复杂,不是简单的几句话就能说明白的。

我也是通过很长时间的学习实践,才逐步掌握了ECT模块的使用。

本文将通过一系列的实例,从最简单的功能开始,逐步展开。

一步一步的展示ECT 模块的强大功能。

实验1:自由运行计数器(TCNT)与溢出中断自由运行计数器(TCNT)也称为自由运行主定时器,是一个16位的计数器,可以说是ECT的核心。

在系统复位时,这个自由运行计数器的初值为$0000。

当ECT 模块运行时,自由运行计数器从$0000~$FFFF 循环递增计数。

当计数器溢出复零时,会置位中断标志。

利用这个计数器,可以产生一个周期的中断信号。

TCNT 的输入时钟也是可以选择的,图2 给出了TCNT 的时钟源的示意图。

可以看出,TCNT的输入时钟可以来源于总线时钟、总线时钟经过预分频、外部引脚输入的脉冲、外部引脚输入脉冲经过脉冲累加器分频这四种选择。

当然,选择哪个时钟源其实就是在程序中设置一下相应的寄存器这么简单。

了解了上面的介绍,就可以开始本文的第一个例子了,这个例子非常简单,将BUS CLOCK 分频后作为TCNT 的输入时钟,使能TCNT 溢出中断。

在开始代码之前,还需要介绍几个程序中用到的寄存器。

TCNT寄存器(Timer Count Register)这个寄存器其实已经介绍过了,它是一个16 位的只读寄存器。

在每个时钟输入下计数值会自动加1,当计数值为0xFFFF 后下一个时钟脉冲会使计数器溢出为0x0000。

飞思卡尔单片机 第1节-CPU寄存器

CPU寄存器

CPU寄存器

累加器 (A) 累加器A是一个通用8位寄存器。经常用于暂存一个输入到算 术逻辑单元(ALU)的操作数,并且用于存放(ALU)的计算结果。 复位对累加器A的内容没有影响。 索引寄存器(H:X) 这个16位寄存器实际上分为两个8位寄存器(H和X),它们作为 一个16位的地址指针一起工作,H存放一个地址的高位字节 和X存放地址的低位字节。所有索引寻址模式指令利用H:X中 全部16位值作为一个索引参考指针;然后,为了与早先 M68HC05家族兼容,一些指令只在低8位(X)中运行,并且H在 复位过程中强制为0x00。复位对X的内容没有影响。

HCS08 CPU的特点包括:

▪目标代码完全向上兼容M68HC05和M68HC08家族 ▪所有寄存器和存储器映射在单块64 Kbyte地址空间 ▪16位堆栈指针SP(64 Kbyte地址空间中的任意大小堆栈) ▪16位索引寄存器(H:X)的强大的寻址索引模式 ▪多种寻址模式 ▪8位累加器(A) ▪支持存储器到存储器的数据传送 ▪高效的位操作指令 ▪快速的8位乘8位和16位除以 8位指令 ▪STOP和WAIT指令唤醒低功耗运行状态

条件代码寄存器(CCR) 条件代码寄存器 8位条件代码寄存器存放中断屏蔽位(I)和5个指出刚执行指令 结果的标志。第5和第6位永远设置为1。如图:

I 位是中断屏蔽控制位,与其他位不同的是它在CCR 中不是处 理器状况位。在CCR的六个可执行位中,I 位也是复位后唯一可 被初始化的位。I 位复位后置为1,这使得中断被屏蔽直到堆栈 指针被初始化。其他五个状态位(V、H、N、Z 和C)在复位后是 未知的,只有在执行一个指令后才能知道。复位后无须强制这 些位为特定的值,因为直到执行了一个影响它们的指令后,与 这些位相关的条件转移才有意义。 这五个状态位标志了运算和其他指令的结果。条件转移指令 根据CCR 内状态位的值来决定是直接转移到一个新的程序地址, 还是继续执行下一个指令。简单的条件转移指令(BCC、BCS、 BNE、BEQ、BHCC、BHCS、BMC、BMS、BPL 和BMI)所导 致的转移取决于单一的CCR 位状态,而其他转移指令则被两三 个更复杂的CCR 位控制。例如,若布尔表达式[(Z) | (N⊕V)]真, 则将产生小于等于转移(BLE).

飞思卡尔单片机教学

沿锁存。LSTRB:在外部使用2片8位宽度存储器时和ADDR0,R/W配合使用。可可转转到到9页页图图。。

模式选择和PORTE复用 TEST:保留脚,接地 XIRQ:非屏蔽中断 IRQ:可屏蔽中断

RAM

EEPROM

Flash/ROM

外部扩展存储器

低

§3-5 复位及时钟—复位

上电复位

单片机自动检测VDD端的正跳变,启动自动工作。

外部复位

通过RESET引脚加一低电压,拉低超过一定时间 后可实现复位。

看门狗复位

帮助系统在软件跑飞后自动复位。

时钟监视器复位

利用内部的RC电路来保证时钟频率满足要求。

MC9S12DG128拥有128K的FLASH,8K的RAM,2K的EEPROM。

用于给单片机内部提供合适的电源电压,9S12单片机内核使用2.5V供电.VDD1\2,VSS1\3,VDDPLL若使用电压调整模块,这些引脚

电压调整模块及相关引脚 只用接去耦电容.注意VDD1.2的箭头是向外出的.

电压调整模块

存储器容量寄存器

RAM_SW2-RAM_SW0:分配系统RAM存储空间

寄存器区映射寄存器-INITRG

指定内部寄存器区基址的高5位。 则最小基址是$0000,最大基址为$7FFF(D7=0决定)。

使用时,一般定位在$0000开始的1K中。 因为前256个字节可以用直接地址(8 bit地址)访问,如果

Z: 0标志,当运算结果为0时,该位置1。

V: 2补码运算溢出标志,当运算结果出现2补码溢出时,该位置1。

飞思卡尔MC9S12XS128单片机重点模块讲解

�

这一点和 51 单片机的 I/O 口有区别,在典型的 51 单片中 P0 口内部没有上拉电阻,但作为 I/O 口使用时需要外接排阻。其他 P1-P3 口则可以直接作为双向口使用,51 单片在上电复位 后端口被默认的置 1.在 51 单片中端口的某一位置 0 时端口作为输出口使用,置 1 时作为输 入口使用。例如如果我们想把 P1 作为输出口使用时我们可以在程序开始时写 P1=0x00; 如果 我们想把 P1 口作为输入口使用时我们可以写 P1=0xff; 这一点正好和飞思卡尔的 128 单片机 相反,另外 128 单片有专门的数据方向寄存器 DDRA 或者 DDRB 等来管理各个端口的输入 输出选择,51 单片没有。如果我们想把端口 A 作为输入口使用,我们只需写 DDRA=0x00; 即所有位都置 0,如果我们想把端口 A 作为输出口使用,我们只需要写 DDRA=0xff; 即所有 位都置 1 ,而如 果我们想要 把端口 A 的高四 位做输入口 ,低 4 位做输 出口时我们 就 写 DDRA=0x0f; 当我们需要将该端口的某一位做输出或者输入口使用时只需要将该端口对应的 方向位置 1 或者置 0 即可。例如我们想把 A3 口作输入口, A4 口作输出口使用时我们只需 要写: DDRA_DDRA3=0; DDRA_DDRA4=1; 即可。 � � 对于数据方向寄存器的使用只要记住:置 1——输出 置 0——输入 PORTA 数据寄存器也是由 8 位组成,任何时候都可以对它进行读写操作。

#define uchar unsigned char //数据类型宏替换 #define uint unsigned int /*------------------------延时函数--------------------------------------*/ void delay(uint a) { uint i,j; for(i=0;i<a;i++) for(j=0;j<a;j++) ; } /*--------------------------指示灯闪烁函数-------------------------------*/ void light() { while(INPUT) { PORTB=0x3f; delay(500); PORTB=0x00; delay(500); } } //6 只灯全点亮 //延时一段时间 //6 只灯全熄灭 //延时一段时间 //判断输入电平的高低

飞思卡尔8位单片机—飞思卡尔8位单片机基础知识

7〉 管脚的复用

注意: 0、管脚功能复用时的优先 级见右表,高优先级接管管 脚时,对低优先级模块会产 生杂乱信号,因此切换前应 先停止不使用的功能。 1、PTA5作为只能输入管脚 而言,输入电压不能超过 VDD。 2、IIC使用的端口可以通过 设置SOPT2 寄存器中的 IICPS位重新定位到PTB6和 PTB7,复位时缺省使用 PTA2 and PTA3。 3、如果ACMP和ADC被同 时使能,管脚PTA0和PTA1 可同时使用。

管脚及其功能

6〉 管脚控制寄存器

位于高页面的管脚控制寄存器,可以独立设置每个管 脚的输出驱动强度、输出信号变化速度、输入脚的内部 上拉允许等。内部上拉的设置有些时候自动失效,比如 管脚设为输出、管脚被外设使用、管脚作为模拟电路使 用等。如果管脚被用于键盘中断KBI模块,,并设置上升 沿触发,则允许上拉时实际是配置了下拉电阻。 对输出管脚设置了输出变化速度控制后,可以减少 EMC辐射,变化速度控制对输入脚无效。 输出管脚的输出驱动强度控制,可以选择更大的驱 动电流,虽然每个输出管脚都可以设置成大电流驱动, 但总电流不能超出芯片的工作范围。同时大驱动电流对 EMC辐射也会有一定影响。

• EPROM

EPROM(Erasable Programmable ROM,可擦除可编 程ROM)芯片可重复擦除和写入,。EPROM芯片在其正 面的陶瓷封装上,开有一个玻璃窗口,透过该窗口,可以 看到其内部的集成电路, 紫外线透过该孔照射内部芯片 就可以擦除其内的数据,完成芯片擦除的操作要用到 EPROM擦除器。EPROM内资料的写入要用专用的编程 器,并且往芯片中写 内容时必须要加一定的编程电压( VPP=12—24V,随不同的芯片型号而定)。EPROM的型 号是以27开头的,如27C020(8*256K)是一片 2M Bits容 量的EPROM芯片。EPROM芯片在写入资料后,还要以 不透光的贴纸或胶布把窗口封住,以免受到周围的紫外线 照射而使资料受损

飞思卡尔16位单片机概述

飞思卡尔16位单片机概述飞思卡尔提供所有16位汽车电子解决方案。

飞思卡尔有着30多年汽车电子的领导地位,并将继续开拓微控制器技术,是全球领先的汽车工业半导体供应商。

飞思卡尔是全球第十大半导体厂商,也是最大的汽车和通讯产业嵌入芯片制造商。

2004年,飞思卡尔从摩托罗拉中剥离了出来。

目前,它为摩托罗拉提供绝大多数手机用芯片。

S12X系列的性能达到了原HCS12器件五倍。

S12X系列尽管增加了172条额外指令来提高分页访问功能并执行32位计算,但其设计宗旨是实现与先前编写的HCS12代码的完全兼容性。

此外,S12X系列还提供了业界首个XGATE模块。

这个多用途、高效处理器实现了高达80 MIPS 的附加处理能力,将一些诸如基本网关活动和相关外设处理的任务从主CPU上卸载。

其并行架构实现了对于中断可进行更多的决定性处理并使设计工程师可以避免核心功能与中断处理间的冲突。

相关系列S12XB系列面向通用市场进行了特性/成本优化,针对相对S12XD需要更精简外设的应用;提供128K 到256K Flash和80到112个管脚的封装。

S12XD系列面向通用市场的全功能系列,满足很广泛的应用需求,在可裁减性、兼容性和整体系统成本上提供极高的价值。

提供64K到512K Flash和80……S12XE系列S12X系列中性能最好的产品,带有XGATE和增强的系统集成特性。

提供128K到1MB的Flash 和80到208个管脚的封装。

S12XF系列面向底盘节点中执行器和传感器应用的Flex Ray系列;提供128K Flash和64到112个管脚的封装。

S12XH系列MC9S12XHZ系列16位微控制器是工业界第一款集成片上TFT图形显示驱动的产品,扩充了低端仪表板的图形显示能力。

MC9S12XHZ512……S12XS系列S12XS 16位微控制器(MCU)系列针对广泛的低成本汽车车身电子应用进行了优化。

提供64K到256K Flash和48到112个管脚的封装。

飞思卡尔单片机教程

注 : A/D模块的时钟频率要在500KHz和2MHz之间, 所以在选择分频因子时一定要注意。

采样时间选择

SMP [1 :0]

采样时间

00

2个 A/D时钟周期

01

4个A/D时钟周期

ATDclock= ( (BusClock) / (PRS+1) ) /2

10

8个A/D时钟周期

11

16个A/D时钟周期

设CCBCA = 000,转换序列从通道

0开始;ATD0DR0,

ATD0DR1,ATD0DR2存放转换结果

设CCBCA = 0 10,转换序列从通道 2开始。 仍然是ATD0DR0,

ATD0DR1,ATD0DR2存放转换结果

S8C 、S4C 、S2C 、S1C:定义转换队列的长度 。默认长度为4。 FIFO: 结果寄存器先进先出模式 。1=FIFO模式 ,转换结果是连续 存放的;0=非FIFO模式 ,转换结果放在对应的寄存器中。 FRZ1、FRZ0:背景调试冻结模式允许 。这两个控制位就决定了,

{ while (ATD1STAT0_SCF ==0) ;

ad_value [0] = ATD1DR0; ad_value [4] = ATD1DR4;//使用 PORTB= (byte) ad_value [4] ;

}}

void ATDInit(void)

{ATD1CTL2=0xC0;//AD模块上电,快速清零,无等待模式,禁止外部触发, 中断禁止 // ADPU AFFC AWAI ETRIGLE --- ETRIGP ETRIGE ASCIE ASCIF

PRS=3

ATD1CTL5=0xA4; //右对齐无符号 ,单通道采样 ,通道0

单片机飞思卡尔开发工具使用入门讲解学习

Crystal

单片机原理与应用

Page

一、概述

3.实验目标板

Signal connector

PWM D/A convert

7Seg Numeric LED

keypad

Connect points Pulse generator

RS232 driver

Analog voltage generator

单片机原理与应用

Page

二、创建工程 C/C++ Options

第7步:选择V5.0中的用户自定义模式

单片机原理与应用

Page

二、创建工程 PC-Lint

第8步:选择不使用PC-Lint(TM)链接工具软件,点击“完 成”按钮,Code Warrior集成开发环境就会自动生成整个工 程的文件系统。

LED(light emitting diode/发光二极管) 将电转化为可见光

PN节结构,正向导通发光,反向截至熄 灭。

多种颜色,多种尺寸,多种封装 控制流经电流决定其亮度,需要使用限

流电阻 LED具有一定的响应速度

单片机原理与应用

Page

五、并行口及驱动 8.Turn on LED

单片机原理与应用

单片机飞思卡尔开发工具使用入 门

本章要点

一、概述

二、创建工程 三、编写程序 四、编译调试 五、并行口及驱动 六、实验扩展

单片机原理与应用

一、概述

CodeWarrior IDE

main(fad) { return(0); }

build

010010001 110010010 001010010

USB cable

Jutch the debugger

飞思卡尔单片机ppt讲解

单片机(中国)——微控制器MCU(国外)Micro Controller Unit

片上系统 SoC(System on Chip):提高可靠性、降低复杂性、减少硬件尺

寸、降低成本和功耗。

应用系统单片化:总有一款适合你!(几千种) 嵌入式系统ES( Embedded systems ):以应用为中心、以计算机技术

针孔摄像机有线或无线实时传输,可以边 拍边看。这些摄像头都是很小的,最小的 跟手表上装的那种纽扣电池差不多。

1.3 单1.1片计算机机历的分史类与及发新展 技术

单片机的发展

• 20世纪70年代,4位单片机问世 • 第一代(1976一1978年)探索阶段

Intel、Motorola • 第二代(I978一1982年)完善阶段

同时可以实现简单的调试功能,如显示和修改各内部寄存器、显 示和修改内存等。 * 通过PC串口和单片机的串口实现人机对话,可以使单片机的开发 不依赖于任何开发工具(51系列仿真芯片SST89E516) * 占用用户资源(串口、片内RAM和闪存) * 监控程序和应用程序共享一个CPU,因此不能做动态调试。

CPU的集成度已达到千万只晶体管,时钟频率高达GHz

1.3 单片机历史及新技术

计算机的发展动向

1.大型、巨型计算机

2.小型、微型计算机

中国国防科技大学2011年5月公布超级电脑“ 天河一号”,每秒运算速度逾千万亿次,使中国

成为继美国之后第二个能研制千万亿次超级电脑

的国家。该电脑一天的运算量相当于一台主流个 人电脑不间断地计算160年。这套重155吨的先进 系统,由103个冰箱大小的银灰色机柜组成,占地 面积约1000平方公尺。这台超级电脑耗资人民币6 亿元。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

强烈建议!

• 尽量使用默认的资源映射设置! • 需要对资源映射时,注意不要使地址重叠,导致异常错误

Slide 9

TM

Freescale Semiconductor Confidential and Proprietary Information. Freescale™ and the Freescale logo are trademarks of Freescale

MODC MODB MODA

0

0

0

0

0

1

0

1

0

0

1

1

1

0

0

1

0

1

1

1

0

1

1

1

MODE Special Single Chip Special Expanded Narrow

Special Test Emulation Expanded Wide

Normal Single Chip Expanded Narrow

工作模式

RESET

HCS12

MODA MODB MODC/BKGD

Mode Pins are sampled and latched on rising edge of Reset .

CLOCK /RESET

MODA MODB MODC

Mode Register

Sample Latch $_0B

Special Single Chip Emulation Exp Narrow Special Test Emulation Exp Wide Normal Single Chip Normal Exp Narrow

Peripheral Mode Expanded Wide

MODx Write Capability

MODC, B, A write anytime but not to 110 no write

MODC, B, A write anytime but not to 110 no write

MODB, A write once but not to 110 no write

Peripheral Normal Exp Wide

Slide 2

TM

Freescale Semiconductor Confidential and Proprietary Information. Freescale™ and the Freescale logo are trademarks of Freescale

Semiconductor, Inc. All other product or service names are the property of their respective owners. © Freescale Semiconductor, Inc. 2005.

MODC, MODB, MODA Write Capability

Peripheral Mode

1

1

1

Expanded Wide

ADDR DATA BDM

0

0 Active

16

8 Allowed

16

16 Allowed

16

16 Allowed

0

0 Allowed

16

8 Allowed

---

---

---

16

16 Allowed

MODA and MODB have active pulldowns during reset. MODC has the pull-up on the pin enabled after reset.

内部RAM位置初始化寄存器

Slide 6

TM

Freescale Semiconductor Confidential and Proprietary Information. Freescale™ and the Freescale logo are trademarks of Freescale

Semiconductor, Inc. All other product or service names are the property of their respective owners. © Freescale Semiconductor, Inc. 2005.

Semiconductor, Inc. All other product or service names are the property of their respective owners. © Freescale Semiconductor, Inc. 2005.

映射优先级

如果资源映射时,发生重叠,则优先级高的资源有效

Freescale

HCS12 微控制器 MC9S12DP256

2005年8月

TM

Freescale Semiconductor Confidential and Proprietary Information. Freescale™ and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. © Freescale Semiconductor, Inc. 2005.

的范围内,而且映射的地址必须是2K的整数倍。

内部寄存器位置初始化寄存器

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Slide 5

0

0TM

0

1 0 0 0 0 0 0 0 0 0 0 0 0 0x1000 Freescale Semiconductor Confidential and Proprietary Information. Freescale™ and the Freescale logo are trademarks of Freescale

使用 HCS12的第一步

1) HCS12 技术概述 2) Operating Modes工作模式 3) Resource Mapping资源映射 4) External Bus Interface外部总线接口 5) Port Integration Module端口集成模块 6) Background Debug Mode背景调试模 块MODC MODB MODA源自MODE00

0

Special Single Chip

0

0

1

Special Expanded Narrow

0

1

0

Special Test

0

1

1 Emulation Expanded Wide

1

0

0

Normal Single Chip

1

0

1

Expanded Narrow

1

1

0

分配他们的位置。

2. 这些寄存器只能写一次,建议在初始化分配寄存器,RAM,EEPROM

的位置。对每个INITxx赋值后,在其指令后需插入一空指令。

3. 如果映射有冲突,寄存器具有最高优先级,与其重叠的RAM和

EEPROM此时无效。

4. 复位后,寄存器从0x0000开始,但可以被映射到64K空间内的前32K

内部存储器映射-EEPROM

1. DP256有4K的EEPROM,通过INITEE的EEON位来使能 • 复位后,EEPROM区域从$0000开始,但可被映射任意64K空间中

的4K字节块内。

• EE15-12决定16位EEPROM区域地址的前4位

比如:INITEE=0x11,则地址是从$1000开始

no write

no write

Slide 4

TM

Freescale Semiconductor Confidential and Proprietary Information. Freescale™ and the Freescale logo are trademarks of Freescale

优先级

最高

... ... ... ...

最低

资源

BDM space (Internal) when BDM is active this 256 byte block of registers and ROM

appear at $FF00 – $FFFF Register Space (Internal) – 1K bytes fully

Semiconductor, Inc. All other product or service names are the property of their respective owners. © Freescale Semiconductor, Inc. 2005.

Modes of Operation

TM

Freescale Semiconductor Confidential and Proprietary Information. Freescale™ and the Freescale logo are trademarks of Freescale

Semiconductor, Inc. All other product or service names are the property of their respective owners. © Freescale Semiconductor, Inc. 2005.

Semiconductor, Inc. All other product or service names are the property of their respective owners. © Freescale Semiconductor, Inc. 2005.