嵌入式系统教案-中断(全英)

嵌入式系统第12节 中断

中断的作用

(1)并行操作,提高工作效率 并行操作,

CPU与外设同时工作,多个外设同时工作。

(2)实现实时处理

在控制系统中,有些参量要求计算机能快速处理,用中断方式很容易 实现。

(3)故障处理

出现故障,提出中断申请,要求计算机及时响应。

中断源

引起中断的原因或能发出中断申请的来源。

Intelligence & Control

中断控制器

程序状态寄存器PSR(全局)

F位置1,CPU不接受FIQ I位置1,CPU不接受IRQ

Intelligence & Control

SRCPND/ SUBSRCPND

Intelligence & Control

SRCPND为主中断源引脚寄存器,SUBSRCPND为副中 断源引脚寄存器 作用是用于标示出哪个中断请求被触发 SRCPND的有效位为32,SUBSRCPND 的有效位为11, 它们中的每一位分别代表一个中断源。如果相应中断源产生 中断请求则其对应位置为1。该寄存器中的位将自动由中断 请求置位,而不管INTMASK寄存器中的掩码位是否有效。 另外,该寄存器不受中断控制器的优先级逻辑影响。在中断 服务程序中,该寄存器的相应位必须进行清零处理,清零的 方法是将该位写入1。

Intelligence & Control

中断过程

Intelligence & Control

子中断源状态寄存器

中断源状态寄存器

关于__irq 的使用

Intelligence & Control

__irq用来表示一个函数是否为中断函数 现场保护和恢复自动完成 给不具备中断嵌套功能的ARM系统带来了问题,若使用 __irq 时有中 断嵌套产生,现场保护就会混乱。 若有中断嵌套,需要自己编写中断入口现场保护代码

嵌入式技术应用教程——SC第五章

第五章中断中断是指计算机在执行程序的过程中,当出现异常情况或特殊请求时,计算机停止现行程序的运行,转向对这些异常情况或特殊请求的处理,处理结束后再返回现行程序的间断处,继续执行原程序。

中断是单片机或ARM实时地处理内部或外部事件的一种机制。

换言之,中断可以作为ARM外围设备与CPU之间的一种联系或通信方式。

S3C2410A中有56个中断源,这些中断源分别为:表 5.1假如UART0的接收缓存收到了来自外部的数据,那么设备UART0要通知CPU已经收到数据,请示CPU进行下一步工作。

那么UART0要通过什么方式告知CPU收到数据了呢?设想一下,UART是通用异步收发器的英文缩写,一般在ARM芯片与外部进行数据传输的时候并不是一直不断地进行数据交换,而是断断续续地进行数据通信,那么CPU不可能一直监视着UART设备。

在UART设备不进行数据收发时,CPU可以去进行别的程序处理。

一旦UART 设备需要和外部进行数据传输的时候,比如收到了来自外部设备的一帧数据,此时CPU还在进行着别的程序处理,那么UART设备就要告知CPU收到数据了,需要对数据进行处理,UART会通过中断的方式通知CPU,打断CPU正在进行的工作,让CPU对UART收到的数据进行处理。

此时CPU收到UART的中断通知,那么他会停下正在处理的工作,保存当前的数据,转向UART的数据处理程序(UART中断服务程序)对UART收到的数据进行处理,处理完毕后如果没有其他设备的中断请求,CPU会跳转回UART中断之前的程序,调出中断时保存的数据继续运行中断之前的程序。

S3C2410A是以ARM920T为内核的ARM,ARM920T内核有两种中断模式:FIQ和IRQ。

IRQ全称为Interrupt Request,即是“中断请求”的意思。

FIQ全称为Fast Interrupt Request,即是“快速中断请求”的意思。

FIQ模式是特权模式中的一种,同时也属于异常模式一类。

嵌入式系统实验2中断实验

中南大学嵌入式系统实验(二)中断实验学院:**************专业班级:*********姓名:*************学号:*************中断实验一.实验目的1.熟悉arm开发板中断原理。

并产生中断。

2.了解快速中断和普通中断。

编写嵌套中断实验。

二.实验器材PC机一台,周立功开发板一块三.实验原理EasyARM2103开发板提供了4个绿色发光二极管用作显示,电路如图1.1所示。

显示电路采用了灌电流的方式来驱动发光二极管,由于微控制器LPC2103 I/O口提供的灌电流大于其拉电流,采用此驱动方式可以保证二极管发光的亮度。

1.1Led电路原理四. 实验原理ARM体系的CPU有7种工作模式,可以通过软件来进行模式切换,或者发生各类中断、异常进行相应模式。

CPU可以识别两种类型中断,正常中断(IRQ)和快速响应中断(FIQ)状态寄存器的PSR中F和R位决定是中断的启闭。

为了使能中断,必须将PSR中F或R位清零,并且中断屏蔽寄存器相应位也要清零。

ARM中断分为子中断源和一般中断源,子中断源多了两个寄存器SUBRCPN(标识子中断源是否发生)INTSUBMSK(屏蔽子中断源)。

ARM中断发生过程如下:1.如果为子中断源,则SUBSRCPND寄存器相应位置1,然后根据子中断源屏蔽寄存器(INTSUBMSK)的设置来判断该中断是否被屏蔽,如未屏蔽,则在SRCPND寄存器相应位置1。

2.如果为非子中断则直接在SRCPND寄存器相应位置1。

3.如果INTMOD寄存器中该中断被设置为FIQ快速中断(相应位置1),即该中断立即执行。

如不是,则判断INTMSK寄存器中该中断是否被屏蔽,如未屏蔽,则进入中断优先仲裁器进行中断优先设置(PRIORITY寄存器)经过中断优先仲裁后,最高优先级的中断在INTPND寄存器中相应位置1(同一时间,此寄存器只有一位置1),INTOFFSET寄存器值用来表示INTPND寄存器置1位(即INTPND 寄存器中位[x]为1时,INTOFFSET寄存器值为x,可以用它确定是什么中断。

(完整word版)嵌入式-中断实验

实验五中断控制实验(一)实验目的了解中断的作用;掌握嵌入式系统中断的处理流程;掌握ARM中断编程。

(二)实验设备计算机;ARM硬件仿真器;ARM开发板(三)实验硬件设置在做实验之前,先将开发板电源接好,将仿真器的USB连线与电脑相连,通电,然后按核心板的复位键。

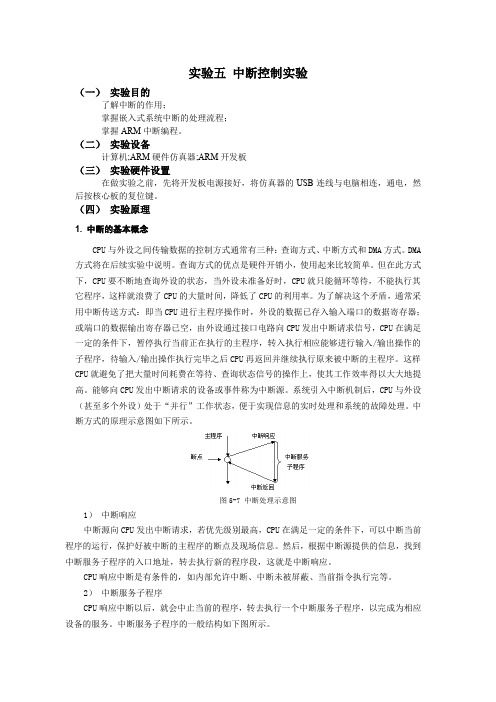

(四)实验原理1. 中断的基本概念CPU与外设之间传输数据的控制方式通常有三种:查询方式、中断方式和DMA方式。

DMA 方式将在后续实验中说明。

查询方式的优点是硬件开销小,使用起来比较简单。

但在此方式下,CPU要不断地查询外设的状态,当外设未准备好时,CPU就只能循环等待,不能执行其它程序,这样就浪费了CPU的大量时间,降低了CPU的利用率。

为了解决这个矛盾,通常采用中断传送方式:即当CPU进行主程序操作时,外设的数据已存入输入端口的数据寄存器;或端口的数据输出寄存器已空,由外设通过接口电路向CPU发出中断请求信号,CPU在满足一定的条件下,暂停执行当前正在执行的主程序,转入执行相应能够进行输入/输出操作的子程序,待输入/输出操作执行完毕之后CPU再返回并继续执行原来被中断的主程序。

这样CPU就避免了把大量时间耗费在等待、查询状态信号的操作上,使其工作效率得以大大地提高。

能够向CPU发出中断请求的设备或事件称为中断源。

系统引入中断机制后,CPU与外设(甚至多个外设)处于“并行”工作状态,便于实现信息的实时处理和系统的故障处理。

中断方式的原理示意图如下所示。

图5-7 中断处理示意图1)中断响应中断源向CPU发出中断请求,若优先级别最高,CPU在满足一定的条件下,可以中断当前程序的运行,保护好被中断的主程序的断点及现场信息。

然后,根据中断源提供的信息,找到中断服务子程序的入口地址,转去执行新的程序段,这就是中断响应。

CPU响应中断是有条件的,如内部允许中断、中断未被屏蔽、当前指令执行完等。

2)中断服务子程序CPU响应中断以后,就会中止当前的程序,转去执行一个中断服务子程序,以完成为相应设备的服务。

嵌入式系统中断课程设计

嵌入式系统中断课程设计一、课程目标知识目标:1. 理解中断在嵌入式系统中的基本概念、作用和重要性;2. 掌握中断响应过程、中断优先级管理和中断嵌套的处理方法;3. 学会分析中断服务程序的设计和优化方法;4. 了解中断相关硬件原理,如中断控制器、中断请求和中断向量。

技能目标:1. 能够运用所学知识设计简单的中断服务程序,并实现中断功能;2. 能够运用调试工具对中断相关程序进行调试和优化;3. 能够分析和解决嵌入式系统中断相关的实际问题。

情感态度价值观目标:1. 培养学生对嵌入式系统及中断技术的兴趣,激发学习热情;2. 培养学生严谨的科学态度,注重实践与理论相结合;3. 培养学生团队协作意识,学会共同分析和解决问题。

本课程针对高年级学生,结合嵌入式系统课程特点,旨在提高学生理论联系实际的能力,培养学生解决实际工程问题的技能。

通过本课程的学习,使学生具备嵌入式系统中断相关领域的基本知识和实践技能,为后续深入学习打下坚实基础。

同时,注重培养学生的情感态度价值观,提高学生的综合素质。

二、教学内容1. 中断基本概念与原理:介绍中断的定义、分类及其在嵌入式系统中的作用;讲解中断响应过程、中断向量表和中断优先级管理。

教材章节:第三章“中断与异常”2. 中断控制器:分析中断控制器的原理、结构和功能;介绍中断请求、中断屏蔽和中断向量寄存器的作用。

教材章节:第三章“中断控制器”3. 中断服务程序设计:讲解中断服务程序的设计方法、中断处理流程和注意事项;举例说明中断服务程序的应用。

教材章节:第四章“中断服务程序设计”4. 中断嵌套与优先级管理:介绍中断嵌套的概念、实现方法及优先级管理的原则;分析中断嵌套时的程序执行流程。

教材章节:第五章“中断嵌套与优先级管理”5. 中断调试与优化:讲解中断相关程序的调试方法、技巧和优化策略;分析实际案例,提出解决方案。

教材章节:第六章“中断调试与优化”6. 实践环节:设计中断实验,使学生动手编写中断服务程序,实现特定功能;通过实验巩固理论知识,提高实际操作能力。

嵌入式系统教学课件:第八讲 嵌入式软件编程-中断和时间管理

~OSTCBCur->OSTCBBitX) == 0) {

OSRdyGrp &= ~OSTCBCur->OSTCBBitY; } OSTCBCur->OSTCBDly = ticks; OS_EXIT_CRITICAL(); OSSched(); } }

/* 初始化uC/OS-II*/

/* 应用程序初始化代码... */

/* 调用OSTaskCreate()创建至少一个任务*/

允许时钟节拍中断; /* 错误!可能crash!*/

OSStart();

/* 开始多任务调度 */

}

26

系统的初始化与启动

在调用C/OS-II的任何其它服务之前,用户必须 首先调用系统初始化函数OSInit()来初始化 C/OS的所有变量和数据结构;

❖ 调用OSTimeDLY后,任务进入等待状态; ❖ 使用方法

void OSTimeDly (INT16U ticks); ticks表示需要延时的时间长度,用时钟节

拍的个数来表示。

17

OSTimeDLY()

void OSTimeDly (INT16U ticks) {

if (ticks > 0) {

任务的PC

高地址

堆栈的增长

12

时钟节拍

时钟节拍是一种特殊的中断,相当于操作 系统的心脏起搏器;

μC/OS需要用户提供周期性信号源,用于 实现时间延时和确认超时。节拍率应在10 到100Hz之间,时钟节拍率越高,系统的额 外负荷就越重;

时钟节拍的实际频率取决于用户应用程序 的精度。时钟节拍源可以是专门的硬件定 时器,或是来自50/60Hz交流电源的信号。

课件:第06讲 - 嵌入式处理器中断处理

访问 RO

复位值 0

地址 0xFFFF F000

RO

0

0xFFFF F004

所有中断的状态寄存器 VICRawIntr 该寄存器读出32个中断请求/软件中断的状态,不 RO

管中断是否使能或分类

0

0xFFFF F008

注意:读取VICRawIntr寄存器将得到所有32个中断请 求和软件中断的状态西安,电子它科不技大管学软中件断学院是否使能或分类 。 18

向量地址0寄存器 VICVectAddr0

向量地址31寄存器 向量地址寄存器

VICVectAddr31

VICVectAddr

名称

VICVectAddr0 ~

VICVectAddr31

描述

复位 置

向量地址0寄存器 0

~

向量地址31寄存器

地址

0xF200_0100 ~

0xF200_017C

VIC0Addr

R/W 0xFF 0xE020_0F00

R/W 0 0xE020_0F40

西安电子科技大学软件学院

30

• 寄存器汇总

1.正在执行用户程序;

2.外部中断0发生中断;

3.VIC硬件将中断服务程序 地址装入VICVectAddr寄 存器; 4.程序跳转至异常向量表 中IRQ入口0x0018处; 5.执行指令跳转至 VICVectAddr寄存器中的 中断服务地址;

0x0000000

异常向量表

0

④

⑤

①

用户程序 ②

⑥ 中断服务程序

中断地址寄存器 0

西安电子科技大学软件学院

0xF200_0F00

15

• 寄存器描述-控制寄存器

名称

嵌入式系统课程“中断、异常与事件”教学实践及启示

“异常”作为与“中断”不完全相同的一个概 念,其显著差异的另一重要体现(或证据)是针 对它们的允许与屏蔽指令不同 [1]。

就微处理器或微控制器的角度而言,根据触 发源(即“异常”事件)的不同,一般可将异常 分为同步异常和异步异常。同步异常是指与 CPU 当前执行的指令密切相关,造成 CPU 正常运行 状态被中止的系统事件(或称内部事件),如指 令未定义、指令预取中止、数据访问中止等。异 步异常则由外部事件触发,与 CPU 当前执行的 指 令 无 关, 故 被 称 为 异 步 异 常(或 外 部 异 常 )。 复位即属于异步异常。

几乎所有的国内外嵌入式系统教材或技术

基金项目:中央高校基本科研业务费资助智库专项课题(3850219013)。 第一作者简介:潘登,男,副教授,研究方向为嵌入式系统教学,pandengreal@。

第7期

教育与教学研究

73

文献,均在“中断”之外都提及“异常”,“异常” 与“中断”显然不是一个完全等价的概念;另一 方面,几乎所有的嵌入式系统教材,在论述微处 理器或微控制器的工作原理时,又都毫无例外地 将“异常”与“中断”混在一起不做区分,说明 微处理器或微控制器处理“中断请求”和系统“异 常”事件一定存在着大量共性的方面。

中断�求 event_IRQ

其他事件 event_other

�常事件 event_exception

事件 event 图 1 中断请求、异常与事件

从图 1 可以明显看到,狭义“事件”“event_ other”与“中断请求”“异常事件”除了具有广义 “事件”的属性之外,显然还存在着明显的差异。 “event_other”在 嵌 入 式 系 统 中 具 体 表 现 为 何 种 “事件”?应如何处理?与“中断请求”“异常事 件”的处理机制是否相同?这些问题都应当在教 学中向学生提出,引导并激发学生去深入思考。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

• When issue n occurs, stop and attend to it

• Requires a method of stopping the normal program flow to jump to attend to the priority task

done state transition) – Can be used to wake periodically from ‘sleep’ saving

power

Dealing with Interrupts

• Do nothing (i.e. wait until something happens)

wait a considerable time to be serviced • Hybrid schemes are possible (execute at

most k tasks before restarting, Round Robin for secondary tasks with prioritised return to important tasks

asking the user to ‘Press any key to continue) • Two main options – Polling loops or Interrupts

Polling Loop

Polling is a method where the processor checks to see if components need attention/servicing. Different ways of checking exist.

Task1

Task5

Task2

Task4

Task3

Polling Strategies - Prioritised

• Tasks listed in priority order • Processor returns to the start after

attending to a task • Disadvantage is that low priority tasks may

• There is no separate operating system - there is nowhere for the program to return to

• The program will run • All errors/exceptions must be handled (NOT by

Question:

In Lab 2, you did not use interrupts, where would they have helped?

Program Flow

• Unlike a general purpose computer, the program in an embedded processor is unlikely to be changed

– external I/O device (like a keyboard or printer) or – an internal event (like an op code fault, or a periodic

timer.) – occurs when the hardware needs service (busy to

• High priority tasks served by interrupts • Important to keep track of who is doing

EE312 Instrumentation and Microcontrollers

Lecture 3: Interrupts

What you will learn

• What the difference is between interrupts and polling

• When to use interrupts • How to use interrupts from C

Interrupts

• An interrupt is the automatic transfer of software execution in response to events (from hardware) that are asynchronous with the current software execution.

Hybrid Systems

• Most embedded systems combine polling loop and interrupt systems

• Polling loop replaces ‘do nothing’ as the background task in the interrupt scheme, dealing with low priority tasks

• Check issue one and attend to as necessary • Check issue two and attend to as necessary

• Check issue n and attend to as necessary

START AGAIN

Polling Strategies - Round Robin

• In a round robin scheme, the processor goes through each task in turn, attending to them as necessary

• All tasks have the same priority

• Can take some time to get back to a task if all the other tasks require attention