集成电路模拟试题1

2023下半年集成选择题

1. 集成电路的集成度是指: A. 集成电路中晶体管的数量 B. 集成电路中电阻的数量

C. 集成电路中电容的数量

D. 集成电路中二极管的数量

2. 集成电路的工艺水平是指: A. 集成电路的制造工艺 B. 集成电路的设计水平 C. 集成电路的封装水平 D. 集成电路的测试水平

3. 集成电路的性能是指: A. 集成电路的功耗 B. 集成电路的速度 C. 集成电路的可靠性 D. 集成电路的抗干扰性

4. 集成电路的应用范围包括: A. 计算机 B. 通信设备 C. 家用电器 D. 汽车电子

5. 集成电路的发展趋势是: A. 集成度越来越高 B. 工艺水平越来越先进 C. 性能越来越好 D. 应用范围越来越广

6. 集成电路的类型包括: A. 小规模集成电路 B. 中规模集成电路 C. 大规模集成电路

D. 超大规模集成电路

7. 集成电路的封装形式包括: A. DIP封装 B. SOP封装 C. QFP封装 D. BGA封装

8. 集成电路的测试方法包括: A. 功能测试 B. 参数测试 C. 可靠性测试 D. 环境测试

9. 集成电路的质量保证包括: A. 原材料质量控制 B. 工艺过程质量控制 C. 产品质量控制 D. 售后服务质量控制

10. 集成电路的市场前景是: A. 非常广阔 B. 比较广阔 C. 一般 D. 不太好。

CMOS模拟集成电路习题集1

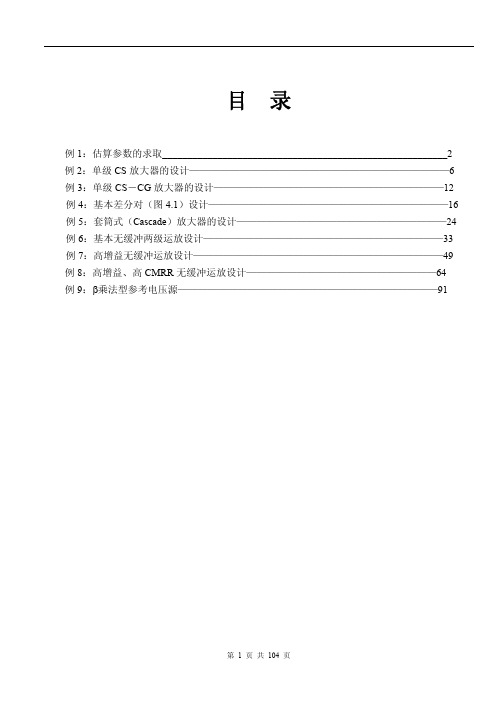

目录例1:估算参数的求取_________________________________________________________2 例2:单级CS放大器的设计——————————————————————————6 例3:单级CS-CG放大器的设计———————————————————————12 例4:基本差分对(图4.1)设计————————————————————————16 例5:套筒式(Cascade)放大器的设计—————————————————————24 例6:基本无缓冲两级运放设计————————————————————————33 例7:高增益无缓冲运放设计—————————————————————————49 例8:高增益、高CMRR无缓冲运放设计———————————————————64例9:β乘法型参考电压源——————————————————————————91例1:估算参数的求取1.Kn 、Kp 的求取图1.1表1.1 思考题1.1:从表1.1中可以看出沟道调制效应系数λ是否为常数?为什么?.上试中:22ox n(p)D on DS onn(p)n(p)μC W W I =V (1+λV )=K V 2L L oxn(p)DS n(p)μC (1+λV K =)22.λn、λp的求取图1.2图1.3图1.4表1.2*比较上面求得的λn、λp与上学期所学教材中λ∝1/L的差异。

MOSFET的简化版图如图1.5所示,其中L1表示MOS管源漏区接触孔与多晶硅之间的最小距离,L2表示接触孔的最小尺寸,L3表示接触孔与源漏区边缘间的最小距离。

寄生电容可按表1.3估算:图1.5表1.3 MOS管寄生电容的计算公式MOSFET的寄生电容C GS C GD C DB(C SB)饱和区C GSO W eff +0.67 C OX W eff L eff C GDO W eff WE C j +2(W+E) C jsw 表1.3中E=L1 + L2 + L3 , L1、L2、L3这些规则尺寸可以很容易在技术资料上找到(对于“懒惰”的工程师们而言,一个也许更高效的办法是从晶元厂提供的版图库中直接通过测量获得)。

1+X集成电路理论练习题含参考答案

1+X集成电路理论练习题含参考答案一、单选题(共40题,每题1分,共40分)1、在电子产品测试中需保证测试环境稳定,其中使用环境稳定是指()。

A、使用人员操作得当B、硬件的工作参数稳定C、软件的工作参数稳定D、模拟真实用户使用时的场景正确答案:D2、以全自动探针台为例,关于上片的步骤,下列所述正确的是:( )。

A、打开盖子→花篮放置→花篮下降→花篮到位→花篮固定→合上盖子B、打开盖子→花篮放置→花篮到位→花篮下降→花篮固定→合上盖子C、打开盖子→花篮放置→花篮下降→花篮固定→花篮到位→合上盖子D、打开盖子→花篮放置→花篮固定→花篮下降→花篮到位→合上盖子正确答案:D答案解析:以全自动探针台为例,上片的步骤为:打开盖子→花篮放置→花篮固定→花篮下降→花篮到位→合上盖子。

3、转塔式分选机设备进行编带后,进入( )环节。

A、上料B、测试C、外观检查D、真空包装正确答案:C答案解析:转塔式分选机设备芯片检测工艺的操作步骤一般为:上料→测试→编带→外观检查→真空包装。

4、通常情况下,一个内盒中装入的DIP管装芯片( )颗。

A、3000B、1000C、5000D、2000正确答案:D答案解析:一般情况下,一个内盒中装入的DIP管装芯片2000颗。

5、元器件的引线直径与印刷焊盘孔径应有()的合理间隙。

A、0.1~0.4mmB、0.2~0.3mmC、0.1~0.3mmD、0.2~0.4mm正确答案:D6、在电子电路方案设计中最简单的显示平台是()。

A、OLEDB、LCDC、LEDD、数码管正确答案:C7、平移式分选机进行料盘上料时,在上料架旁的红色指示灯亮的含义是( )。

A、上料机构故障B、上料架上有料盘C、上料架上有空料盘D、上料架上没有料盘正确答案:B答案解析:平移式分选机进行料盘上料时,上料架上是否有料盘可以通过上料架旁的传感器进行检测。

当传感器指示灯为红色时,表明上料架上还有料盘,可以继续进行上料,当传感器指示灯为绿色时,表明上料架上无料盘,停止上料。

《模拟电子技术基础》习题课1-2章-概念

三种组态为:BJT的共射、共基、共集 FET的共源、共栅、共漏

BJT

FET

差放

共射 共射 共集 共基 共源 共漏 共栅 差模 共模 (带反馈Re)

微变等效电路

p74

Ri

Ro

Av

15

模拟电路习题课(一)

共射小信号(微变)等效分析 输入电阻、输出电阻和增益

Ri

vi ii

rbe // Rb

Av

vo vi

(1 1)R'L rbe (1 1)R'L

1

R'o

rbe

1 1

//

rce1

rbe

1 1

Ro R'o // ro2 R'o

共集放大器的Ri比共射大很多

电压放大倍数接近于1(小于1)因此称为射随器

共集放大器的Ro比共射的小很多

17

模拟电路习题课(一)

共基小信号(微变)等效分析

R'i

U

反向击穿 电压VBR

2

二极管的电阻

模拟电路习题课(一)

直流等效电阻 RD:

RD

VD ID

交流(动态)电阻 rd:

rd

(

diD dvD

)Q1

2vd 2id

rd

(

diD dvD

)Q1

VT ID

3

模拟电路习题课(一)

共射(共E)BJT工作原理

以发射极(E极)作为公共端,EB结正偏,CB结反偏。

iC

参见 P12 图1.3.4

7

3. 饱和区

vCE<vBE vCB<0

4

集电结正偏

1+X集成电路理论模拟考试题(含参考答案)

1+X集成电路理论模拟考试题(含参考答案)一、单选题(共39题,每题1分,共39分)1.下列说法错误的是()。

A、在cadence软件界面上,单击Tools菜单,选择Library Manager命令,出现“库文件管理器”B、用户可以在库文件里新建单元,但不能在新建的单元下新建视图C、选择Tool选项中的Composer-Schematic选项,表示在单元下建立电路图视图D、在电路编辑窗口中,利用图标栏可以快速建立、编辑电路图正确答案:B2.湿度卡的作用是( )。

A、去潮湿物质中的水分B、可以防止静电C、起到防水的作用D、显示密封空间的湿度状况正确答案:D答案解析:湿度卡是用来显示密封空间湿度状况的卡片。

3.通过监控某一特定谱峰或波长,在预期的刻蚀终点可探测到对应的数据的方法是()。

A、发射光谱法B、干涉测量法C、质谱分析法D、椭圆偏振法正确答案:A答案解析:发射光谱法是通过监控来自等离子体反应中一种反应物的某一特定发射光谱峰或波长,在预期的刻蚀终点可探测到发射光谱的改变,从而来推断刻蚀过程及终点。

4.芯片封装工艺中,下列选项中的工序均属于前段工艺的是()。

A、晶圆切割、引线键合、塑封、激光打字B、晶圆贴膜、芯片粘接、激光打字、去飞边C、晶圆贴膜、晶圆切割、芯片粘接、引线键合D、晶圆切割、芯片粘接、塑封、去飞边正确答案:C答案解析:封装工艺流程中前段工艺包括晶圆贴膜、晶圆切割、芯片粘接以及引线键合,后段工艺则包括塑封、激光打字、去飞边、电镀以及切筋成型。

5.对准和曝光过程中,套准精度是指形成的图形层与前层的最大相对位移大约是关键尺寸的()。

A、二分之一B、三分之一C、四分之一D、五分之一正确答案:B答案解析:版图套准过程有了对准规范,也就是常说的套准容差或套准精度。

具体是指要形成的图形层与前层的最大相对位移。

一般而言大约是关键尺寸的三分之一。

6.晶圆检测工艺中,6英寸的晶圆进行晶圆墨点烘烤时,烘烤时长一般为()分钟。

【精品】集成电路试题

集成电路试题二、选择题(14分,每小题2分)1、集成运放的输入级采用差分放大电路是因为可以()。

A减小温漂B增大放大倍数C提高输入电阻2、为提高集成运放的放大倍数,集成运放的中间级多采用()。

A共射极放大电路B共集放大电路C共基放大电路3、现有电路:A反相运算电路B同相运算电路C积分运算电路D微分运算电路E加法运算电路F乘方运算电路(1)欲将正弦波电压转换成二倍频电压,应选用()。

(2)欲将正弦波电压叠加上一个直流量,应选用()。

(3)欲实现Au=-100的放大电路,应选用()。

(4)欲将方波电压转换成三角波电压,应选用()。

(5)欲将方波电压转换成尖顶波电压,应选用()。

下列关于74LS245的用途,不正确的说法是()A.常用于数据锁存B.常用于数据双向传送C.常用于数据驱动D.常用于数据缓冲一、RS-232C标准的电气特性中数据"0"规定为()二、 A.-3~-15V三、 B.-5~0V四、 C.0~+5V五、 D.+3~+15V六、选择题;1一个理想运放的基本条件是()。

(a)A ud=∞;(b)r od=∞;(c)r id=0;(d)K CMRR=0。

2集成运放在应用中出现自激,这一般是由于下述原因之一所致()。

(a)退耦电容太大;(b)分布电容太小;(c)负载电容太大;(d)耦合电容太大。

3在下列几种典型的积分电路中,哪个是比较积分电路?()。

4模拟电路的非线性应用之一是()。

(a)比例放大;(b)求和放大;(c)积分器;(d)对数器。

5模例乘法器的应用电路之一是()。

(a)加法器;(b)减法器;(c)整流器;(d)鉴频器。

6在下例比较器中,抗干扰能力最强的是()。

(a)单门限比较器;(b)迟滞比较器;(c)窗口比较器;(d)三态比较器。

7在集成变换器中,属于周期性变换器的是()。

(a)U/I变换器;(b)I/U变换器;(c)U/F变换器;(d)阻抗变换器。

8DAC0832的转换位数是()。

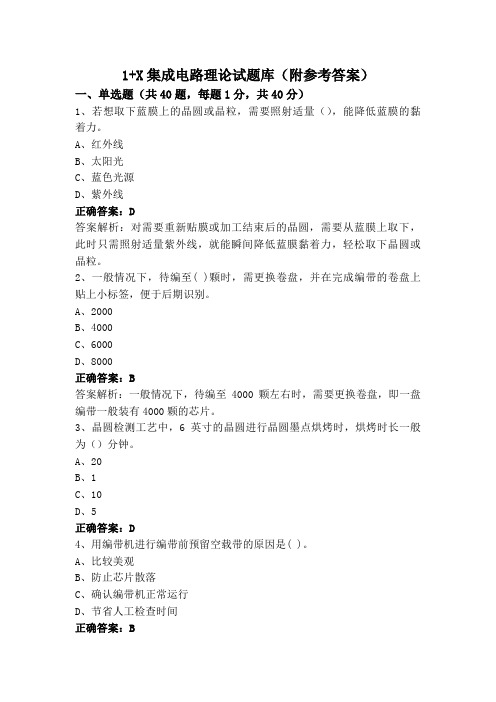

1+X集成电路理论试题库(附参考答案)

1+X集成电路理论试题库(附参考答案)一、单选题(共40题,每题1分,共40分)1、若想取下蓝膜上的晶圆或晶粒,需要照射适量(),能降低蓝膜的黏着力。

A、红外线B、太阳光C、蓝色光源D、紫外线正确答案:D答案解析:对需要重新贴膜或加工结束后的晶圆,需要从蓝膜上取下,此时只需照射适量紫外线,就能瞬间降低蓝膜黏着力,轻松取下晶圆或晶粒。

2、一般情况下,待编至( )颗时,需更换卷盘,并在完成编带的卷盘上贴上小标签,便于后期识别。

A、2000B、4000C、6000D、8000正确答案:B答案解析:一般情况下,待编至4000颗左右时,需要更换卷盘,即一盘编带一般装有4000颗的芯片。

3、晶圆检测工艺中,6英寸的晶圆进行晶圆墨点烘烤时,烘烤时长一般为()分钟。

A、20B、1C、10D、5正确答案:D4、用编带机进行编带前预留空载带的原因是( )。

A、比较美观B、防止芯片散落C、确认编带机正常运行D、节省人工检查时间正确答案:B答案解析:空余载带预留设置是为了防止卷盘上编带的两端在操作过程中可能会出现封口分离的情况,导致端口的芯片散落。

5、使用化学机械抛光进行粗抛时,抛光区域温度- 般控制在()A、38~50°CB、20~50°CC、20~30°CD、20~38°C正确答案:A答案解析:一般抛光区的温度控制在38~50°C (粗抛)和20~30°C (精抛)。

6、用比色法进行氧化层厚度的检测时,看到的色彩是()色彩。

A、反射B、干涉C、衍射D、二氧化硅膜本身的正确答案:B答案解析:硅片表面生成的二氧化硅本身是无色透明的膜,当有白光照射时,二氧化硅表面与硅-二氧化硅界面的反射光相干涉生成干涉色彩。

不同的氧化层厚度的干涉色彩不同,因此可以利用干涉色彩来估计氧化层的厚度。

7、芯片检测工艺中,进行管装包装时,将真空包装的编带盘放入内盒、合上盖子后,需要在内盒的封口边()处贴上“合格”标签。

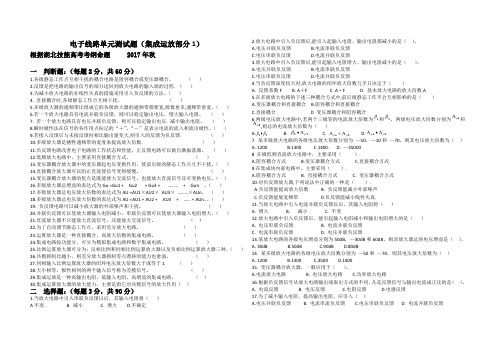

电子线路单元测试题(集成运放部分1)

电子线路单元测试题(集成运放部分1)根据湖北技能高考考纲命题 2017年秋一判断题:(每题2分,共60分)1.各级静态工作点互相干扰的耦合电路是阻容耦合或变压器耦合。

()2.反馈是把电路的输出信号的部分送回到放大电路的输入端的过程. ()3.为减小放大电路的非线性失真的措施采用引入负反馈的方法。

()4. 直接耦合时,各级静态工作点互相干扰。

()5.多级放大器的通频带比组成它的各级放大器的通频带都要宽,级数愈多,通频带愈宽。

()6.若一个放大电路具有电流并联负反馈,则可以稳定输出电压,增大输入电阻。

()7. 若一个放大电路具有电压并联负反馈,则可以稳定输出电压. 减小输出电阻。

()8.瞬时极性法在信号的各作用点标记的“+”、“-”是表示电流的流入和流出极性。

()9.若接入反馈后与未接反馈时相比输出量变大,则引入的反馈为负反馈. ()10.多级放大器是牺牲通频带的宽度来提高放大倍数. ()11.负反馈电路改善电子电路的工作状态和性能,正反馈电路可以做自激振荡器。

()12.低频放大电路中,主要采用直接耦合方式。

()13.变压器耦合放大器中的变压器起电压变换作用,使前后级的静态工作点互不干扰。

()14.直接耦合放大器可以阻止直流使信号变得缓慢。

()15.变压器耦合放大器的优点是既能放大交流信号,也能放大直流信号还可变换电压。

()16.多级放大器总增益的表达式为Gu =Gu1 + Gu2 + Gu3 + ………+ Gun 。

()17.多级放大器总电压放大倍数的表达式为AU =AU1×AU2×AU3×………×AUn。

()18.多级放大器总电压放大倍数的表达式为AU =AU1 + AU2 + AU3 + …… + AUn。

()19. 负反馈电路可以减小放大器的外部噪声和干扰。

()20.并联负反馈可以使放大器输入电阻减小,串联负反馈可以使放大器输入电阻增大。

()21.直流放大器不只能放大直流信号,还能放大交流信号。