数字下变频FPGA实现

数字下变频的FPGA实现

通常不能满足实际需要, 常采用 多 级 级 联 的 方 法 来 获 得 较 好 的 阻带衰减。如果使用 ’ 级的级联 )*) 来实现, 阻带衰 减 将 达 到 ( 1 ./ = 2>) ’@ ?, = 但并不可以 任 意 地 增 大 ’ 值, ’ 值的增大同 时也会引起 通 带 波 纹 (通 带 容 限) 的 增 大, 从而影响滤波器性 能。另外, 从式 (<) 中 可 以 得 到 ’ 级 级 联 后 的 振 幅 将 达 到 #’ , 需要必要的运 算 对 其 进 行 修 正。 因 为 )*) 滤 波 器 无 需 乘 法 运 算, 该滤波器应用在下变频系统数据量最大的最前端。 图/ ( 9) 所示为用 ’A6B4CD484:9BE: 软 件 工 具 设 计 的 )*) 滤 波 器模型。其主体部分由 . 个 2 阶、 2 倍抽取率的 )*) 滤 波 器 和 . 个移位寄存器 组 成。 其 中 移 位 寄 存 器 的 作 用 是 适 当 的 衰 减 由 于多级滤波器级联 导 致 的 振 幅 增 大 问 题。 图 / ( F) 为设计模型

{

., (! " ! # 1 . ( , 其他

(2)

的仿真结果。其中波形 . 为 输 入 信 号, 波 形 % 为 输 出 信 号。 因 输入信号为标准正弦波形, 理 想 情 况 下 带 宽 为 . 。 因 此, 2 倍下 变频反映到时域中的效果为对输入信号进行 2 倍的抽取。

由于 )*) 滤波器的所 有 系 数 都 是 . , 因此这种滤波器实现 起来极其简单, 只是通过简单 的 求 和 即 可 完 成 滤 波 过 程。 这 种

!"": 年 第&期

仪 表 技 术 与 传 感 器

=.)*/?,+.* 6+HF.BA?+ 0.G ’+.)1/

宽带信号数字下变频技术的FPGA实现

• 189•两路供电一路是NORMAL POWER,一路是ESS POWER,线路图上也是两路供电但实际操作中按要求拔出跳开关后DEU 上还有电,带电拆装容易损坏DEU ,所以在进行拆装时还要整机断电(图1)。

AMM 23-73-00-22700-00-B 。

2)DEU 的联接端和终端:DEU 上的终端/联接端盒是根据DEU 在飞机上的安装位置决定的IPC23-73-09-08H 图而且两者件号是不同的(图2、图3)。

航后报告有故障信息CAM NOT LOADED 或OBRM/CIDS(101RH)-SDF1之类故障一般就要重新安装CAM 或OBRM 卡然后进行测试。

注意COM 卡和OBRM 及PRAM 卡在FAP上会显示件号,拔出后会显示图2图3NONE ,重新安装后要做一遍上电测试才会出现件号。

航后报告有信息SMOKE 一般情况下要更换DIRECTOR,因为烟雾探测是有CIDS 计算机SDF 部分的功能。

总结:CIDS 系统功能强大涉及到的部件及故障多种多样,引起的原因也各不相同,排故时要考虑到的东西很多,我们平时要本着从易到难,从简单到复杂的思路进行排故,尽量不要把问题搞大。

因为虽然CIDS 系统大都是客舱内的故障但有些还是影响飞行或者是根本就无法放行,所以对CIDS 系统还是要有一定的了解,对我们在航前,过站能快速准确的对相应的故障有一个正确处理措施保障航班的正常运行有很大的帮助。

引言:雷达发射信号的带宽直接决定雷达的距离分辨率,高分辨率目标识别雷达要求更高的信号带宽,以实现对目标型号的具体识别。

对于要求信号实时处理的雷达系统,高速的ADC 采样速率与低速的FPGA 流水处理速率,需要引入多相滤波理论,通过并行多相分解实现FPGA 低速处理高速的ADC 采样信号,并且通过合适的抽取速率以降低数字下变频后信号的处理速率。

1 数字下变频的多相分解传统的窄带信号数字下变频理论是将信号混频、低通滤波、抽取。

一种基于FPGA的高效多路独立数字下变频的实现方法

总第 3 8 4期 RE S E A RC H ON T E L E COMM U NI CA T I ON T EC HN oL oGY 2 0 1 4年 第 2期

一

种基于 F P G A 的高效 多路

独 立数 字 下 变 频 的实 现 方法

弥 宪梅 刘 亭 亭 杨 鑫 刘 芬

收 机 的 数 量 , 而 且 需 要 大 量 的天 线 共 用 设 备 和

射 频 控 制 模 块 , 整 个 监 测 系 统 将 会 很 庞 大 , 同 定站 建设 的复杂度亦会增 加 , 更不适 合在机载 、

舰载 、 车 载等机动载 体上使 用 。 面对这一 问题 ,

迫 切 需 要 数 量 大 而 且 小 型 化 、控 制 灵 活 的 接 收 机 。 为 此 ,利 用 宽 带 接 收 采 集 、 软 件 无 线 电处 理技 术进行 窄带处理成 为接 收机土要 的方式 。

能 , 使 数 据 传 输 和 数 据 融 合 更 加 方 便 ,而 且 控

・2 8・ s i n ( £ " )

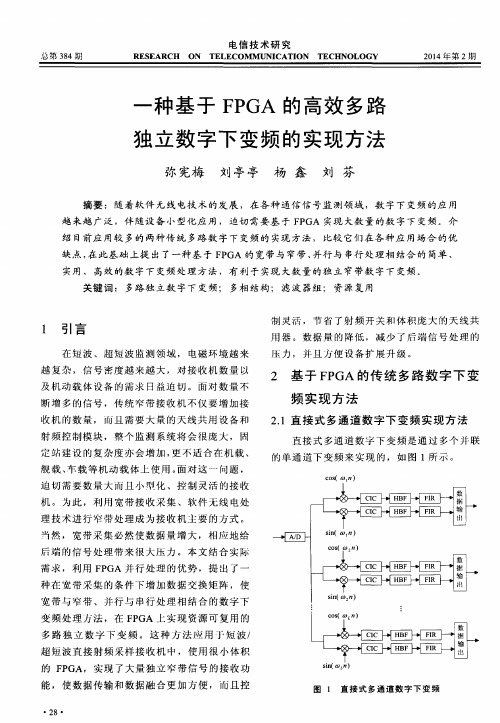

图 1 直 接 式 多通 道 数 字下 变频

科技论文:一种基于 F P G A 的高 效 多 路 独 立 数 字 下 变 频 的 实 现 方 法

图 中共 有 £个 通 道 , 可 分 别 对 A/ D 采 样 带

种 滤波器组进 行多相分解 , 得 到 均 匀 DF T滤 波

宽 内 的 £个 信 号 ( 由 £个 本 振 频 率 l , ∞ 一

£

器 组 的 推 导

得 出均 匀 DF T滤 波 器 组 多相 结 构 如 图 3所 示 。

决 定 )进 行 接 收 处 理 。根 据 带 宽及 采 样 率 需

数字下变频电路的FPGA实现

数字下变频电路的FPGA实现随着数字化时代的到来,数字信号处理技术已经成为了许多领域中不可或缺的一部分。

其中,数字下变频技术是一种非常重要的数字信号处理技术,被广泛应用于雷达、通信、音频处理等领域。

本文将介绍数字下变频电路的FPGA实现。

数字下变频电路的基本原理数字下变频电路的基本原理是将输入信号进行混频,将高频信号转换为低频信号,并对低频信号进行采样和滤波,得到一个纯净的低频信号。

数字下变频电路通常由数字信号处理器、数字乘法器和数字低通滤波器等组成。

FPGA实现数字下变频电路的优势 FPGA(Field Programmable Gate Array)是一种可编程逻辑器件,能够根据需要实现各种数字电路。

与传统的数字信号处理芯片相比,FPGA具有以下优势:高速并行处理能力:FPGA内部具有大量的可编程逻辑器件,可以实现高速并行处理,提高处理速度和效率。

灵活性:FPGA可以通过重新编程实现不同的数字电路,方便灵活,可以快速适应不同的应用场景。

可靠性:FPGA内部具有严格的质量保证措施,保证了数字电路的可靠性和稳定性。

设计数字下变频电路的算法:根据具体应用场景和要求,利用MATLAB 等软件设计数字下变频电路的算法。

将算法转换为硬件描述语言:将设计的数字下变频电路算法转换为硬件描述语言(如VHDL或Verilog),并利用EDA工具进行仿真和验证。

将硬件描述语言编译成二进制文件:将生成的硬件描述语言编译成二进制文件,以便在FPGA上实现。

将二进制文件下载到FPGA中:将生成的二进制文件下载到FPGA中,通过调试和测试,最终实现数字下变频电路。

结论数字下变频电路的FPGA实现具有高速并行处理能力、灵活性和可靠性等优势,已经被广泛应用于雷达、通信、音频处理等领域。

通过设计算法、转换为硬件描述语言、编译成二进制文件以及下载到FPGA中等步骤,可以实现数字下变频电路的高效、快速和可靠实现。

数字下变频电路是一种重要的信号处理单元,它在通信、雷达、电子对抗等领域有着广泛的应用。

数字下变频的FPGA实现

一 一 一

一 一 一 一 … 一 一 一 一

Ke y wo r d s : DDC; I P c o r e ; d i r e c t d i g i a t l s y n t h e s i z e r ( DDS) ; F PGA

中图分类号 : T N 7 4

文献标 识码 : B

文章编号 : 1 9 9 4 — 3 0 9 1 ( 2 0 1 3 ) 0 5 — 0 6 9 — 0 7 2

0 引 言

软件无线 电是 目前和未来无 线通信 系统的关键技术 ,

s o f t wa r e r a d i o ,t h i s p a p e r i n t r o d u c e s t h e d i it g a l d o wn c o n v e r s i o n p r i n c i p l e ,a n d t h e n ma i n l y d i s c u s s e s t h e

果表 明 , 各 个模块 和 整 个 系统 都 能按 要 求工作 , 从 而验证 了 F P G A 实现 数 字 下变频 的正确 性 。

关键 词 : 数 字 下变频 ; I P核 ; 数 字频 率合成 器( DDS ) ; F 1 - 1 / 一  ̄ A

Re a l i z a t i o n o f di g i t a l d own c o n ve r s i o n by FPGA

F P GA me t h o d ,t h r o u g h t h e F P G A c h i p V i r t e x 一 5 Xc 5 v l x l 1 0 T d e s i g n a n d i mp l e me n t a t i o n o f d i it g a l d o wn

基于FPGA的高速数字下变频系统设计

基于FPGA的高速数字下变频系统设计摘要:基于FPGA设计了一高速数字下变频系统,在设计中利用并行NCO和多相滤波相结合的方法有效的降低了数据的速率,以适合数字信号处理器件的工作频率。

为了进一步提高系统的整体运行速度,在设计中大量的使用了FPGA中的硬核资源DSP48。

Xilinx ISE14.4分析报告显示,电路工作速度可达360MHz。

最后给出了在Matlab和ModelSim中仿真的结果,验证了各个模块以及整个系统的正确性。

数字下变频(Digital Down Conversion,DDC)是软件无线电系统的关键模块之一,其可将高频数据流信号变成易于后端数字信号处理器(Digital Signal Processor,DSP)设备实时处理的低频数据流信号。

在数字下变频实现中,随着信号采样率的不断提高,数据率也会相应的提高,但是实际应用中随着数据速率的不断提高,数据处理器件(如FPGA)的处理速度会无法满足要求而不能正常工作,从而带来了数字信号处理的瓶颈问题。

本设计就是以多路并行NCO技术为基础,研究了如何在FPGA中用多路并行采样数据的方式来解决数据处理器件无法提供高速率的匹配信号的问题,并给出了高速DDC实现的架构和仿真结果。

1 数字下变频基本原理数字下变频主要由频谱搬移和抽取两部分组成,如图1所示,其中频谱搬移包含数控振荡器(Numerically Controlled Oscillators,NCO)、乘法器和低通滤波器(LPF,Low Pass Filter);抽取包含抽取滤波器(LPF2)和D倍的抽取,LPF2是为了限制信号的频谱,以免抽取后发生混叠。

模拟信号经过A/D转换后分成两路信号,一路信号和NCO输出的正弦信号相乘(同相分量),一路和NCO输出的余弦信号相乘(正交分量),之后经过低通滤波器(LPF1)将高频分量滤除,然后信号经过抽取滤波以降低速率,最终输出的两路信号就可以送往后续的数字信号处理器中做进一步的处理。

基于FPGA的数字下变频设计与实现

基于FPGA的数字下变频设计与实现在扩频通信中,数字下变频(DDC)是一种很重要的技术,它包括数字混频器、数控振荡器以及数字滤波器三部分。

而传统的DDC 大多采用专用芯片,虽然其外围电路简单、功能实现容易控制,但其大部分功能已经固化,存在兼容性较差、产品开发灵活性低、后续升级困难等缺陷。

本文利用FPGA 运算快速、易于升级等优点,在简化算法的基础上,用最短的时间进行混频滤波得到两路相交信号。

用Verilog 语言对整个下变频进行行为描述建模,并给出相应的仿真综合结果。

1 正交下变频方案理论分析因为DDC 的数据流是采样信号的速率,DSP 处理芯片很难完成高频实时处理任务,而且FPGA 中通常有大容量ROM 资源,满足查找表所需ROM 资源,所以更适合用FPGA 实现数字正交下变频。

数字正交下变频是借助数控振荡器NCO 通过查找表的方式产生本地正交载波信号,与输入信号进行正交混频,经过低通滤波得到I―Q基带信号。

图1 为其方案框图。

接收机收到的高频信号表达式为:式中,为接收信号的幅值,d(t)为数据信息的波形,c(t)为伪码波形,fc=891 MHz,fd=18.176 MHz 为信号频偏,n(t)为高斯白噪声。

根据带通采样定理,引入单位冲激函数δ(t)构成冲激函数P(t):输入信号为x(t),其傅里叶变换为x(ω),则用fS 抽样后得到抽样信号可表示为:由傅里叶变换性质得到XS(ω),可表示为:由式(5)可知,A/D 采样使信号频谱发生了周期延拓。

中心频率fC=891 MHz(如图2)经带通欠采样后将信号频谱搬移至fO=18.533 MHz。

fO 是fC 除以fS 后的余数。

这样A/D 采样实现了一个下变频功能。

tips:感谢大家的阅读,。

FPGA_ASIC-数字下变频的FPGA实现

数字下变频的FPGA实现作者:郑传家屈德新邱晓军周铁解放军理工大学通信工程学院来源: 电子产品世界摘要:本文介绍了数字下变频的组成结构,并通过一个具体的实例,给出了FPGA实现的具体过程。

关键词:FPGA;数字下变频;VHDL引言数字化中频(DIF)频谱分析仪在高中频实现数字化处理,具有分析带宽大、RBW小、测量时长短,可对复杂信号实施时—频分析的功能,因而得到越来越广泛的应用。

但由于现有的数字信号处理器(DSP)处理速度有限,往往难以对高速率A/D采样得到的数字信号直接进行实时处理。

为了解决这一矛盾,需要采用数字下变频(DDC)技术,将采样得到的高速率信号变成低速率基带信号,以便进一步的分析处理。

用现场可编程阵列(FPGA)来设计数字下变频器有许多好处:FPGA在硬件上具有很强的稳定性和极高的运算速度,在软件上具有可编程的特点,可以根据不同的系统要求,采用不同的结构来完成相应的功能,具有很强的灵活性,便于进行系统功能扩展和性能升级。

数字下变频数字下变频的主要目的是经过数字混频将A/D转换输出的中频信号搬移至基带,然后通过抽取,滤波完成信道提取的任务。

因此,数字下变频器由本地振荡器(NCO)、混频器、抽取滤波器和低通滤波器组成,如图1所示。

图1 数字下变频原理图A/D变换后的信号分成两个信号,一个信号乘以正弦序列(同相分量),下变频至零中心频率上,通过抽取滤波器、整形低通FIR滤波形成与原信号相位相同的信号;另一路信号乘以经过90度相移的正弦序列(正交分量),同样是下变频至零中心频率上,再通过相同的抽取滤波器、整形低通FIR滤波器,形成与原信号正交的信号。

这样,DDC 输出的低速率、零中频的正交的两路信号送往DSP等数字信号处理器进行后续的数字处理。

DDC的FPGA以某中频数字化接收机为例来说明如何实现基于FPGA的数字下变频器。

输入信号为中频26MHz,带宽500KHz的调频信号,该信号经过A/D变换之后送到DDC(A/D 采样精度为8位,采样率20MHz),要求DDC将其变换为数字正交基带信号,并实现10倍抽取,即输出给基带处理器的数据速率为2MSPS,最后再经过16阶FIR滤波器进行信号整形。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

2 系统结构

本文所设计的VB-DDC用于如下图 1 所示的宽带数字接收机中频处理系统 中,该系统硬件主要由 1 片FPGA:Altera公司Stratix II 系列的EP2S60F672C4, AD公司的宽带A/D转换器AD6645(14Bit,最高采样率达 105MSPS)[2],以及TI 公司的达芬奇系列数字信号处理器:TMS320DM6437。 本系统的数据流程如图 1 所示,A/D 采样的中频模拟信号输出至 FPGA, FPGA 中的 VB-DDC 将中频信号下变频至基带,再通过 McBSP 接口将基带信号 传给 DSP 进行解调、功率谱估计等数字信号处理,最后 DSP 再将结果通过以太 网送至上位机 PC 进行显示。同时,VB-DDC 可通过 McBSP 接口接受上位机 PC 传来的配置参数,实现 DDC 的动态配置。

(School of Electronic Engineering, University of Electronic Science and Technology of China , Chengdu , 611731)

Abstract: Digital Down-Converter is an important part of Wideband Digital

DDC 参数 动态 配置

输 出 至 D S P

图 2 FPGA 内部模块框图

3 数字下变频技术

1) 数字下变频中的频谱搬移

数字下变频的理论模型如图 3 所示,主要功能为以下三方面:第一,数字混 频器将 A/D 采样的数字中频信号和数控振荡器(NCO)产生的正交本振信号相 乘,将特定频率的中频信号下变频至基带;第二,低通滤波以滤除带外噪声,提 取有用信号;第三,改变采样速率,降低输出数据率,以利于后级 DSP 处理。 抽取因子变化范围越大(本设计抽取因子为 2~896) ,则可设计实现宽带或窄带 VB-DDC 的灵活性越高。

−n

+∞

D −n

)

(2)

令

Ek ( z ) = 0,1,...D − 1 ∑ h ( nD + k )( z ) , k =

n =0 D −1

(3)

将(3)式代入(2)式可得:

H ( z ) = ∑ z − k Ek ( z D )

k =0 D −1

(4)

式(4)即为 H ( z ) 的多相滤波表达式。若将其和抽取器相结合,则可得抽取 器多相滤波的高效结构如图 6 所示。 由图可见, 此种结构的滤波在抽取之后进行, 可大大降低对硬件的速度要求。 在多相滤波结构中,滤波器阶数由原来的转移函数的 N 个减少到现在每个分支 上的 N / D 个,可以减少滤波运算的累积误差,提高运算精度。 多相滤波结构的数字下变频器在抽取倍数 D 很大时,所需低通滤波器阶数 会很高,需要很多乘法器单元,乃至无法实现。所以本文结合了多相滤波结构与 传统窄带数字下变频结构各自的优点, 实现了在现有硬件条件下性能与资源的平 衡。

x (n)

D

z −1 z −1

E0 ( z )

y ( n)

D

E1 ( z )

z −1

D

ED−1 ( z )

图 6 抽取器多相滤波的高效结构

4 基于 CORDIC 算法的 NCO 模块

NCO 的主要功能就是产生一个理想的频率可变的正弦或余弦序列。数学表 达式如下:

= ) cos(2π × S (n f LO × n), (= n 0,1, 2...) fS

变带宽数字下变频器 (Variable-Bandwidth Digital Down-Converter, VB-DDC) 可以对多种带宽的输入信号进行处理,因此其在雷达、通信、电子侦察等有广泛 应用。商用数字下变频器如intersil公司单通道DDC:HSP50214B等,虽然可以实 现处理带宽可变,但是其最高输入数据采样率只有 65MHz [1],而且由于其采用 多级级联积分梳状滤波器(Cascaded Integrator-Comb, CIC)的传统下变频结构, 因此处理带宽较窄, 不超过 1MHz, 不适合作为宽带数字接收机的数字下变频器。 基于多相滤波结构的宽带DDC可以处理宽带信号,但是处理带宽一般固定,而 且当需要处理信号的带宽很窄时,因为抽取因子变大,所需乘法器数目增多,但 是乘法器的工作频率降低,所以其资源利用率很低。 本文基于 Altera 公司的 Stratix II EP2S60F672C4 所设计的 VB-DDC 结合了传 统数字下变频结构与多相滤波结构的优点, 实现了对输入中频信号的高效高速处 理,同时可以在较大范围内对信号处理带宽进行灵活配置。当 A/D 输出中频信 号采样率为 100MSPS 时,本文设计的这种 VB-DDC 信号处理带宽可在 40MHz~8KHz 的范围内灵活配置,输出基带信号数据率可在 50MSPS~112KSPS 的范围内变化。

关键词:带宽可变;DDC;多相滤波;FPGA

An FPGA Implementation of Variable-Bandwidth Digital Down-Converter in Wideband Digital Receiver

Author: WANG Xiao Tutor: XIA Wei, HAN Chunlin

I 时钟 重 配置

中频 信号

I NCO Q

AD 6645

S W I T C H 开关

2选1 I_N BUS MUX Q_N Q

I_W 2 多相滤波结 构的宽带滤 Q_W 选 1 波器 B U S I_N Q_N M U X

M c B S P 接口

配置 参数

I Q

FPGA EP2S60F672C4

S W 窄带滤 I 波器组 Q_N T C H I_N

中频信号 A/D AD6645 FPGA EP2S60F672C4 McBSP接口 DSP DM6437 100M 以太网

时钟100MHz

图 1 宽带数字接收机中频部分

本文主要讨论该系统中的 FPGA 部分, 其内部各模块框图如图 2 所示。 由图 可见,本设计中的 VB-DDC 可根据处理信号带宽要求,灵活选择下变频器结构 为传统下变频结构的窄带 DDC 或者基于多相滤波结构的宽带 DDC, 或者联合使 用两种结构。

x ( n)

(a)

⊗ ⊗

(b) NCO

低通滤波 (c) 低通滤波 (d)

D抽取 (e) D抽取

I

cos(ωC n)

Q

− sin(ωC n)

图 3 数字下变频理论模型

数字下变频对输入实信号的频谱搬移过程如图 4 所示,其中图 4(c) 中 的阴影部分为图 2 中低通滤波后信号(d)的频谱。

X (e jω )

基于 FPGA 的宽带数字接收机变带宽数字下变频器设计

作者:王晓 导师:夏威 韩春林

(电子科技大学电子工程学院,成都,611731)

摘要:数字下变频器(Digital Down-Converter,DDC)是宽带数字接收机的重

要组成部分, 本文基于 FPGA 芯片 Stratix II EP2S60F672C4 设计了一个适用于宽 带数字接收机的带宽可变的数字下变频器(VB-DDC) 。该 VB-DDC 结合了传统 数字下变频结构与多相滤波结构的优点,实现了对输入中频信号的高效高速处 理, 同时可以在较大范围内对信号处理带宽进行灵活配置。硬件调试结果验证了 本设计的有效性。

Receivers. The Variable-Bandwidth Digital Down-Converter (VB-DDC) ,which is suitable for Wideband Digital Receiver, is implemented in FPGA chip Stratix II EP2S60F672C4. The VB-DDC combines the advantages of traditional digital down-conversion architectures and poly-phase filter architectures, realizes efficient high-speed processing for input IF signal, and could configure the bandwidth of signal processing flexibly in a large range. Hardware test result shows the effectiveness of this design.

(5)

式中 f LO 为本振频率; f S 为 DDC 输入信号的中频信号采样频率。 在本设计中, f LO 要求动态可变, f S 为 100MHz。输入中频信号与其相乘完成混频运算。 Altera 推荐使用现成的或经过测试的宏功能模块、IP 内核,用来增强已有的 HDL 的设计方法。所以本设计的 NCO 使用 Altera 提供的 NCO IP 内核,基于 CORDIC 算法实现以节省 RAM 资源。当 NCO 输出本振频率为 32.4MHz 时,输 出信号的频率响应如图 7 所示。由图可见,NCO 输出信号的质量是令人满意的。 数字混频器即乘法器使用硬件乘法器单元,其速度比 LE 搭建的乘法器有较 大优势,能够满足 100MHz 的运算速度要求。 NCO 部分的实现如图 8 所示, A/D 送来的 14bits 精度的输入信号与 NCO 产 生的 18bits 正弦样本信号和余弦样本信号以 100MHz 的速率相乘, 就完成了输入 信号与本振信号的混频运算,输出为 32bits 有符号数 I、Q。 NCO 的频率分辨率计算公式为:

好,通常需要采用多级 CIC 级联的方法加大阻带的衰减。同时由于 CIC 滤波器 的通带很窄,使其不适合用作宽带数字下变频器。HB 滤波器的滤波器系数近一 半为零,可以节省近一半的乘法器,因此被作为第二级低通滤波和抽取。HB 的 抽取因子固定为 2,特别适合采样率降低一半的要求。通过 CIC 和 HB 滤波抽取 后,基带信号由最初的高数据率被降到较低的速率,适于后级 DSP 处理。FIR 滤波器的主要用途是对整个信道进行整形滤波。