用MATLAB在FPGA芯片中实现数字下变频设计

宽带数字下变频和重采样处理Matlab仿真与FPGA实现

宽带数字下变频和重采样处理Matlab仿真与FPGA实现伍小保;王冰【期刊名称】《现代电子技术》【年(卷),期】2015(000)023【摘要】宽带数字下变频(DDC)和重采样处理可应用于成像雷达和电子对抗宽带侦查等领域的新型宽带数字接收机设计中,讨论了基于多相滤波结构的宽带DDC和重采样滤波处理的高效实现方式,并通过一个设计实例进行Matlab仿真和FPGA实现,给出了仿真和实现结果,该方法可应用于当前新型宽带数字接收机宽带数字解调设计。

%Broadband digital down⁃converter(DDC)and resample processing can be applied in the design of new wideband digital receiver in the fields of imaging radar and broadband reconnaissance in electronic countermeasure. The efficient realiza⁃tion way of resample filtering processing and broadband DDC based on polyphase filtering structure are discussed in this paper. A design instance is adopted to perform Matlab simulation and FPGA implementation. The simulation and implementation results are provided. This method can be used in the design of broadband digital demodulation of the new broadband digital receiver.【总页数】5页(P6-9,12)【作者】伍小保;王冰【作者单位】中国电子科技集团公司第三十八研究所,安徽合肥 230088;中国电子科技集团公司第三十八研究所,安徽合肥 230088【正文语种】中文【中图分类】TN957.51-34【相关文献】1.一种新型高速宽带数字下变频器的FPGA实现 [J], 庞少龙;马志刚;吴子贤2.基于FPGA的宽带信号数字下变频设计与实现 [J], 邓岚;康怀祺;李宏波;鄢林3.宽带数字下变频器的FPGA实现 [J], 顾明超;李倩4.宽带信号接收机中数字下变频的设计与FPGA实现 [J], 覃荣捷;袁晓;辛超;陆大海5.宽带信号数字下变频技术的FPGA实现 [J], 李芾因版权原因,仅展示原文概要,查看原文内容请购买。

基于FPGA的超宽带数字下变频设计

1 引 言

随 着 雷 达 应 用 需 求 的 提 高和 数 字 信 号 处 理 技 术 的 迅 速 发 展 ,对 雷达 接 收 系 统 的设 计 也越 来越希望符合软件无 线电的设计思想 ,即将A D C 尽可能靠近天线 ,将接 收到的模 拟信号尽早数

字化 。 数 字 化 的 中 频信 号 通 常 基 于F P G A 实现 数 字 下 变 频 获 得 基 带 I / Q 信 号 , 但 随 着 信 号 载 频 和 带 宽 的不 断提 高 , 也 需 要 更 加 高 速 的 A D C 完 成 信 号 采 样 ,于 是 对 数 字 下 变频 的 处 理 要 求 也 越 来 越 高 。在 超 宽 带 雷 达 接 收 系 统 中 , 高速 的 数 据 率 使 得 基 于 F P G A 的宽 带 数 字 下 变 频 算 法 己 不 再 适 合 采 用 传 统 的 串 行 结 构 实 现 ,本 文 介 绍 了一 种 基 于 并 行 多 相 滤 波 结 构 的 超 宽 带 数 字 下 变 频 设 计 方法 , 其 并 行 的 流 水 处 理 方 式 使 得 高 速 数 据 无 需缓 存 , 处理 带 宽 也 相 应 大 大 提 高 。 2 . 设 计原 理 根 据 带 通 采 样 定 理 ,在 数 字 中 频 接 收 系 统 中 采样 率 与 信 号 中频 。满 足 / =1 / ( 2 ) M- 1

日 ( z ) :∑ h ( n ) z

月-

设D 为信 号 抽 取 倍 数 , 此式 展 开 后 得 到 :

D- J + ∞ D- 1 - 嘲

—4 0 0 M H I D D R _; l o 0 M H

图 2 高 一2 0 0 MH m l I  ̄ X 4

一种基于FPGA的高效多路独立数字下变频的实现方法

总第 3 8 4期 RE S E A RC H ON T E L E COMM U NI CA T I ON T EC HN oL oGY 2 0 1 4年 第 2期

一

种基于 F P G A 的高效 多路

独 立数 字 下 变 频 的实 现 方法

弥 宪梅 刘 亭 亭 杨 鑫 刘 芬

收 机 的 数 量 , 而 且 需 要 大 量 的天 线 共 用 设 备 和

射 频 控 制 模 块 , 整 个 监 测 系 统 将 会 很 庞 大 , 同 定站 建设 的复杂度亦会增 加 , 更不适 合在机载 、

舰载 、 车 载等机动载 体上使 用 。 面对这一 问题 ,

迫 切 需 要 数 量 大 而 且 小 型 化 、控 制 灵 活 的 接 收 机 。 为 此 ,利 用 宽 带 接 收 采 集 、 软 件 无 线 电处 理技 术进行 窄带处理成 为接 收机土要 的方式 。

能 , 使 数 据 传 输 和 数 据 融 合 更 加 方 便 ,而 且 控

・2 8・ s i n ( £ " )

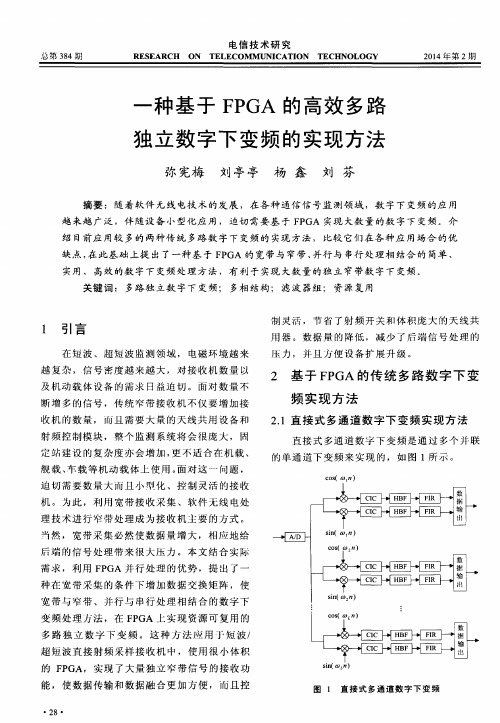

图 1 直 接 式 多通 道 数 字下 变频

科技论文:一种基于 F P G A 的高 效 多 路 独 立 数 字 下 变 频 的 实 现 方 法

图 中共 有 £个 通 道 , 可 分 别 对 A/ D 采 样 带

种 滤波器组进 行多相分解 , 得 到 均 匀 DF T滤 波

宽 内 的 £个 信 号 ( 由 £个 本 振 频 率 l , ∞ 一

£

器 组 的 推 导

得 出均 匀 DF T滤 波 器 组 多相 结 构 如 图 3所 示 。

决 定 )进 行 接 收 处 理 。根 据 带 宽及 采 样 率 需

数字下变频FPGA实现

I

时钟 重

配置

I_W

S W

Q 2选1 I_N BUS

MUX

多相滤波结

2

构的宽带滤 Q_W 选

M c

I Q_N

波器

1B

中频

IT

S

AD 信号

C

6645

NCO Q H

BP U 接口 输

S

出

开关

S

配置

至

FPGA EP2S60F672C4

I Q

I_N W

窄带滤

I

波器组 Q_N T

C

I_N Q_N

M 参数 U DDC X 参数

…

−2π −π −ω1 0 ω1 π 2π ω

(a)下变频前实信号频谱

X (e jω )

−ω1 0

ω

(b)复本振信号频谱

X (e jω )

A

…

…

−2ω1 0 2ω1

ω

(c)混频后的信号频谱

图 4 数字下变频完成的频谱搬移

2) 数字下变频器两种典型结构

a) 传统窄带数字下变频结构

图 5 传统窄带数字下变频结构

本系统的数据流程如图 1 所示,A/D 采样的中频模拟信号输出至 FPGA, FPGA 中的 VB-DDC 将中频信号下变频至基带,再通过 McBSP 接口将基带信号 传给 DSP 进行解调、功率谱估计等数字信号处理,最后 DSP 再将结果通过以太 网送至上位机 PC 进行显示。同时,VB-DDC 可通过 McBSP 接口接受上位机 PC 传来的配置参数,实现 DDC 的动态配置。

Receivers. The Variable-Bandwidth Digital Down-Converter (VB-DDC) ,which is suitable for Wideband Digital Receiver, is implemented in FPGA chip Stratix II EP2S60F672C4. The VB-DDC combines the advantages of traditional digital down-conversion architectures and poly-phase filter architectures, realizes efficient high-speed processing for input IF signal, and could configure the bandwidth of signal processing flexibly in a large range. Hardware test result shows the effectiveness of this design.

数字下变频电路的FPGA实现

数字下变频电路的FPGA实现随着数字化时代的到来,数字信号处理技术已经成为了许多领域中不可或缺的一部分。

其中,数字下变频技术是一种非常重要的数字信号处理技术,被广泛应用于雷达、通信、音频处理等领域。

本文将介绍数字下变频电路的FPGA实现。

数字下变频电路的基本原理数字下变频电路的基本原理是将输入信号进行混频,将高频信号转换为低频信号,并对低频信号进行采样和滤波,得到一个纯净的低频信号。

数字下变频电路通常由数字信号处理器、数字乘法器和数字低通滤波器等组成。

FPGA实现数字下变频电路的优势 FPGA(Field Programmable Gate Array)是一种可编程逻辑器件,能够根据需要实现各种数字电路。

与传统的数字信号处理芯片相比,FPGA具有以下优势:高速并行处理能力:FPGA内部具有大量的可编程逻辑器件,可以实现高速并行处理,提高处理速度和效率。

灵活性:FPGA可以通过重新编程实现不同的数字电路,方便灵活,可以快速适应不同的应用场景。

可靠性:FPGA内部具有严格的质量保证措施,保证了数字电路的可靠性和稳定性。

设计数字下变频电路的算法:根据具体应用场景和要求,利用MATLAB 等软件设计数字下变频电路的算法。

将算法转换为硬件描述语言:将设计的数字下变频电路算法转换为硬件描述语言(如VHDL或Verilog),并利用EDA工具进行仿真和验证。

将硬件描述语言编译成二进制文件:将生成的硬件描述语言编译成二进制文件,以便在FPGA上实现。

将二进制文件下载到FPGA中:将生成的二进制文件下载到FPGA中,通过调试和测试,最终实现数字下变频电路。

结论数字下变频电路的FPGA实现具有高速并行处理能力、灵活性和可靠性等优势,已经被广泛应用于雷达、通信、音频处理等领域。

通过设计算法、转换为硬件描述语言、编译成二进制文件以及下载到FPGA中等步骤,可以实现数字下变频电路的高效、快速和可靠实现。

数字下变频电路是一种重要的信号处理单元,它在通信、雷达、电子对抗等领域有着广泛的应用。

基于FPGA的DDC(数字下变频)设计与实现

在早期的雷达收发系统中,都是采用模拟器件来实现各个功能模块,设计过程中经常会出现温度漂移、增益变化等问题.相对于模拟电路来说,数字电路具有可自检、可编程等优点,上面所述的系统很多部分都已经逐步数字化.在数字化进程中,数字信号处理技术的应用也受到了雷达系统研究工作者的重视,成为相关积累(如FFT、数字滤波、脉冲压缩等)、非相关积累(视频积累)、目标检测以及图像处理等功能的技术保证。随着数字信号处理理论的不断成熟和完善,微电子技术的飞速发展,雷达技术和其它的电子信息化技术的发展,尤其是软件无线电技术的兴起,更加方便了雷达数字化系统的实现。在这样的发展趋势下,除了微波发射和射频部分,整个雷达系统将全部由数字电路实现,在数字信号处理的优势能得到全面的发挥的同时,还使具有体制标准化、系统数字化,功能模块化,低功耗,高度开放性以及灵活性等性能,这将成为了现代雷达系统的关键技术和发展趋势[]。在现今的高科技发展的时代,人们纷纷打起的信息战和电子战,雷达系统在其中扮演的角色尤为重要。为了能更好的适应现代战争的需求,对现今的雷达系统也提出抗干扰、反隐形,具有高分辨力以及强大的自我生存等能力,高要求的提出,使得雷达信号处理技术的研究也得到了快速的进步.目前雷达信号处理正在由视频处理阶段向中频处理阶段迈进,目的就是实现雷达中频以下的处理全部数字化,研究热点.

微系统设计、测试与控制

课程大作业之

基于FPGA的DDC(数字下变频)的设计与仿真

基于matlab的简单数字下变频器的设计

t=0:1/Fs:endtime; N=length(t); n=1; y=zeros(1, N); IND=zeros(1, N); % Input Frequency Word k=floor(fout/Fs*2^Bits); index=0;

%输入原始信号

b = firhalfband(18,0.00245,'dev'); % 获得设计的半带滤波器抽头系数

impz(b);

% 半带滤波器的冲击响应

h = mfilt.firdecim(2,b);

figure

y_fi = filter(h,x);

x = double(x);

y = double(y_fi);

11000

1001

0.809

11010

1010 1011 1100 1101 1110 1111

0.866 0.914 0.951 0.978 0.994 1.000

Matlab程序: %fout: Output frequency %Fs: Sample frequency %Bits: Number of bits of the LUT %endtime: Expectedቤተ መጻሕፍቲ ባይዱsimulation endtime %y: Output sine wave %t: Output time

址吗对数据 ROM 进行寻址。

地址码

幅度(满度值为 1)

数字下变频基于FPGA的软件设计与实现

数字下变频基于FPGA的软件设计与实现【摘要】雷达的数字下变频功能主要是将天线接收到的中频回波信号通过A/D变换后,进行数字下变频处理,转为两路I/Q基带数据。

本文主要设计了一种基于FPGA的数字下变频方法,通过对数字控制振荡器(NCO)及低通滤波器(FIR)的设计及实现,完成了对于不同频率本振信号的数字下变频处理。

结果表明,基于该方案设计的数字下变频功能已在实际系统中得到应用。

【关键词】数字下变频(DDC);FPGA;数字滤波器【Abstract】The function of DDC is mainly to convert the signal received after A/D conversion by the antenna to Digital Down Convert(DDC),finally into two I/Q baseband data. This paper mainly design a method about Digital Down Conversion based on FPGA,by designing the numerically controlled oscillator (NCO)and a low-pass filter (FIR),to convert different frequency signal with DDC. The results showed that the conversion function has been used in the actual system.【Key words】DDC(Digital Down Convert);FPGA;FIR Filter0 引言软件无线电是现今无线通信系统的关键技术,其核心思想是让数字化处理功能尽量的靠近天线,从而将更多的处理通过数字的方式完成。

[1]而数字下变频是软件无线电的关键部分,主要完成对信号的AD变换、混频、滤波以及抽取等工作,包括数字混频模块和抽取滤波模块。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

收稿日期:2004-09-16 第22卷 第12期计 算 机 仿 真2005年12月 文章编号:1006-9348(2005)12-0303-04用M ATLAB 在FPGA 芯片中实现数字下变频设计贾雪琴,李强,王旭,李景宏(东北大学信息科学与工程学院,辽宁沈阳110004)摘要:数字下变频在接收系统的数字化和软件化过程中起到了至关重要的作用。

该文研究了高倍抽取的数字下变频设计,重点分析了基于级联积分梳状滤波器和级联半带滤波器的多级抽样频率算法。

采用最新的设计软件Systemgenerator 软件可以方便地在MAT LAB 中实现算法仿真并可生成FPG A 芯片的下载文件,简化了设计流程,降低了开发成本和周期。

提出了一种基于计算机IS A 总线的系统验证方法。

用Systemgenerator 设计和仿真基于FPG A 芯片的的硬件设计有效地验证了算法并降低了试验成本,是一种好方法。

关键词:数字下变频;半带滤波器;级联积分梳状滤波器;现场可编程门阵列中图分类号:T N998 文献标识码:ARea liza tion of D ig ita l D own Conversion i n FPGA Ch ip by Usi ng M ATLABJ I A Xue -qin,L IQ iang,WAN G Xu,L I J ing -hong(College of Infor mation Science &Engineering,Northeastern University,Shenyang L iaoning 110004,China )ABSTRACT:D igital down conversion p lays a key role in the digitized and soft ware -oriented p rocess of the receiver system.This paper studies the high deci m ation ratio of digital down converter,and especially analyzes the multi -stage deci mation algorithm based on C I C filter and HB filter .It w ill reduce the cost and thedevelopment ti m e by using the newest Systemgenerator which can si m ulate the design and download it to FPG A easily .And verifying the design w ith an IS A bus of computer w ill save lots of money,effectively .U singMAT LAB design and si mulation hardware p rojects based on FPG A is a good method .KEYWO RD S:DDC;HB -filter;C I C -filter;FPG A1 序言现代数字信号处理中,为了满足系统的性能而使用可变频率来实现数字信号处理的过程,称为多速率数字信号处理(multirate digital signal p rocessing ),而其中以数字下变频(DDC )技术应用最为广泛。

它将采样后的数据传输速率降低到最小,使信号接收系统的数字化和软件化得以实现。

与早期的由分立式器件组合而成的下变频器相比,目前市场上出现了多种集成下变频器(如:AD6620,HSP50124b 等),广泛应用于无线电通讯和数据采集等领域。

本文提出一种采用FPG A 器件来实现数字下变频的方案。

与集成器件相比,FPG A 芯片在速度和灵活性上都有很大的提高。

并且,使用FPG A 器件实现的下变频器可以更加方便的采用软件方法对射频链路上引入的干扰进行有效的补偿,同时也可将存储器、控制器等外围器件集成到芯片内部,提高了整个系统的稳定性和集成度。

本设计选用Xilinx 公司的Spartan3系列芯片为设计对象,采用Xilinx 公司与M athwork 公司合作的Systemgenerator 软件进行设计与仿真。

该软件的使用,使得Xilinx 公司提供的IPcore 和M atlab 中的si m ulink 工具得到完美结合,令计算结果可以更加直观的表现出来。

并且,可以将设计模型直接编译成可在FPG A 器件中布局布线的网表文件。

成功地解决了算法研究人员和硬件实现工程师之间的工作协调问题,使得用户能够以最快的速度将他们的算法得到硬件实现。

2 数字下变频原理与实现如图1所示,数字下变频器主要由数字混频器和数字滤波器组两部分组成。

混频器部分由DDS 和两路乘法器组成,数字滤波器部分主要由级联积分梳状滤波器(以下称C I C 滤波器),半带滤波器(以下称HB 滤波器)和后级F I R 滤波器组成的链路构成。

2.1 混频器软件无线电系统接收到的数据是对自然信号调制产生—303—图1 下变频器结构框图的窄带信号,其解析表达式为:z (t )=A (t )・cos [ω0t +θ(t )]+j A (t )・sin [ω0t +θ(t )](1)将上述公式乘以e -j ω0t,将载频ω0下移,变成零载频,其结果称为基带信号(或称为零中频信号)。

则:z 0(t )=A (t )・[cosθ(t )+j sin θ(t )]=z 0i (t )+jz 0q (t )(2)式中: z 0i (t )=A (t )cosθ(t ) z 0q (t )=A (t )sin θ(t )(3)分别称为基带信号的同相分量和正交分量。

基带信号为解析信号的复包络,显然通过基带信号可以无误差的恢复初始的窄带信号。

因此窄带信号既可以用它的解析信号z (t )来表示,也可以用它的基带信号z 0(t )来表示。

而在基带对信号进行处理,可以通过下变频技术将信号处理器的计算量显著降低。

窄带信号相对带宽越窄,这种应用就越有效。

而混频器的作用就是得到输入信号的基带信号。

通过直接数字合成(DDS )技术,可以方便的获得频谱非常纯的正弦和余弦信号,目前采用砷化镓实现的DDS 芯片可以提供几百兆赫兹的输出频率,已经广泛应用于通信系统中。

DDS 技术已经相当成熟,芯片很容易获得,且如果在FPG A 器件中实现DDS 技术很难保证信号的频谱纯度。

因此,本设计中不涉及DDS 技术的FPG A 实现,而是采用了集成DDS 芯片AD9854来提供相应的功能。

图2 混频器模拟及其输入输出频谱 Spartan3系列FPG A 芯片(尚未量产,可申请样片)采用90nm 工艺制造,其内部集成的18bits ×18bits 乘法器可以工作在近百兆的速率。

对于目前国内所能购买的A /D 转换器而言,该性能已经大大超出系统的实际需要。

且使用数字乘法器可以很好的避免模拟器件的功率消耗较大和相位不稳定问题,同时由于每块芯片内部都集成大量的乘法器(4~104个不等,因芯片而异),从而为我们构筑多路接收系统提供了更大的灵活性。

图2显示为混频器的仿真电路和计算结果。

该电路只构造了混频器两路设计中的一路,并且采用直接输入正弦信号的方法来模拟DDS 输入。

频谱图(0~π)中虚线部分显示为原始输入信号的频谱,实线显示为进行混频之后的频谱。

2.2 数字滤波器组高达数十兆甚至上百兆的计算速率对数字运算器提出了更高的要求,而为了在混频之后得到期望的基频信号,需要有相应的抽取滤波器进行操作。

由于涉及到大量的乘、累加运算,抽取滤波器必然将成为制约整个系统工作频率的瓶颈。

本设计采用由C I C 滤波器、HB 滤波器和F I R 滤波器组成的滤波器组进行数字下变频的方法来解决这个问题。

采用多级滤波器级联来实现抽取具有如下优点:1)简化滤波器设计,允许每一级滤波器的过渡代比较宽;2)可以显著的降低运算量;3)减少系统中的存储器的使用量;积分梳状滤波器的冲击响应为:h (n )=1,0≤n ≤D -10,其他(4)图3 C I C 滤波器频谱图3显示的是它的频谱图,这种设计的好处是显而易见的。

由于C I C 滤波器的所有系数都是1,因此这种滤波器实现起来极其简单,它不需要任何乘法运算,不需要存储滤波器—403—系数,几乎不需要任何外部的复杂控制,只是通过简单的求和即可完成滤波过程。

这种结构决定了使用FPG A 器件可以很方便的实现它的设计。

根据它的幅度频谱计算公式:|H (ejω)|=|sin (ωD /2)sin (ωD /2)|=D ・sin c (ωD /2)・sin c -1(ω/2)(5)可得第一旁瓣的衰减大约为-13.46dB 。

这与工程上通常需要的-60dB 相差较大。

通常采用多级级联的方案来解决这个问题。

如果使用Q 级的级联C I C 来实现的话,阻带衰减将达到Q ×(-13.46)dB 。

但是,并不是可以任意的增大Q的值,Q 值的增大同时也能引起通带波纹(或称通带容限)的增大,从而影响滤波器性能。

另外,从式(5)中可以得到Q 级级联后的振幅将达到D Q ,需要必要的运算对其进行修正。

由于第一旁瓣较大,在抽样后引起频率混叠导致C I C 滤波器只有当通带宽度远远小于采样频率的时候才有效,因此该滤波器必须应用在下变频系统的最前级。

图4 C I C 滤波器模型及其输入输出数据 图4(a )所示C I C 滤波器的设计模型。

其主体部分由一个4阶、4倍抽取率的C I C 滤波器和一个移位寄存器组成。

其中移位寄存器的作用是适当的衰减由于多级滤波器级联导致的振幅增大问题。

图4(b )为设计模型的仿真结果。

其中波形1为输入信号,波形2为输出信号。

因输入信号为标准正弦波形,理想情况下带宽为1。

因此,4倍下变频反应到时域中的效果为对输入信号进行4倍的抽取。

图5 半带滤波器频谱半带滤波器(Half -band filter )特别适合于实现2的幂次方倍的抽取,且计算效率高,实时性强。

其频谱图6 分布式F IR 滤波器图如图5所示。

半带滤波器具有如下特性:H (e j ω)=1-H (e j (π-ω))H (ej π/2)=1/2(6)H (n )=1(n =0);0(n =±2,±4,±6,…);滤波系数(n =±1,±3,±5…)也就是说半带滤波器的好处是近乎半数的滤波器系数精确等于零,因此实现这种滤波器时,比对称F I R 设计时的计算量少一半,而比任意系数F I R 设计所需要的乘法次数少四分之三。