【高速中频采样和数字下变频的研究】第九章 数字下变频的设计

软件无线电数字下变频技术研究及FPGA实现

a nd FPGA m pl m e t to i e n a in

H iZ i Q U Y n , E S n E L h , I a g H o g

(co lo nom t n S i c n eh ooy o t etJ o n nvri ,h nd 17 6, hn ) S h o fIfr ai c n e ad T c nlg ,Suh s i t g U i sy C e gu 6 5 C ia o e w a o e t 1

振 荡 器 N O( u r al o t l d O i a r产 生 的 正 交 本 振 信 号 混 频 , 后 再 由 抽 取 滤 波 模 块 进 行 处 C N mei l C nr l s lt ) c y oe l o 然

理, 以输 出低 速 的 低 频 或 基 带 信 号 。本 文 以软 件 无 线 电数 字 下 变频 技 术 为研 究 对 象 , 考 G M系统 建 参 S

Ab ta t I n e t e l w t h r q e c xn f t r g、 e i t g a d s a i g o h iu in l .I t e s r c : t e d o d a i t e f u n y mii g、 l i h e i e n d cma i n h p n f t e p t sg as n h DDC y t m, n s se

基于FPGA的高效数字下变频设计

采样 样 本 , C N O就 增 加 一 个 2t r×.

相 位 增

量, 然后 以 ∑2t o 相位 累 加 角度 作 为地 址 , r× 饥

Hale Waihona Puke 平 台上 , 通过 安装 不 同 的软 件来 完成 各 种 通 信 功

能, 其结 构 的基本 特 征 之 一 就是 使数 模 变 换 尽 量

De i n o g ・ f ce c g t lDo sg f Hi h- i in y Di ia wn- n e so s d o Ef - Co v r i n Ba e n FPGA L i , U Qn WA G G n , A a gj g g N a g H N F n— n i

器、 数字 本振 、 取 和 低 通 滤 波器 组 。数 字 本 振 、 抽 数 字 混 频 可 由采 用 C R I O D C算 法 的数 控 振 荡 器

基 于 F G 的高效 数 字 下变 频 设 计 PA

卢 卿, 王 钢 , 方 景 韩

( 防 科 技 大 学 电 子 科 学 与 工 程 学 院 , 沙 407 ) 国 长 10 3

摘 要 : 绍 了 一 种 高 效 数 字 下 变 频 的 实现 方 法 , 点 介 绍 采 用 坐 标 转 换 数 字 计 算 机 ( O D C 介 重 C R I) 在 实 现 N O 的 同 时 也 完 成 了混 频 器 功 能 。 改 进 了 滤 波 器 组 结 构 , 减 少 资 源 消 耗 的 同 时 , C 在 实

电 子 信 息对 抗技 术 ・ 2 第 5卷

卢

卿, 王

钢 , 方 景 韩

21 00年 5 第 3期 月

基于 FG P A的 高 效 数 字 下 变 频 设 计

基于FPGA的超宽带数字下变频设计

1 引 言

随 着 雷 达 应 用 需 求 的 提 高和 数 字 信 号 处 理 技 术 的 迅 速 发 展 ,对 雷达 接 收 系 统 的设 计 也越 来越希望符合软件无 线电的设计思想 ,即将A D C 尽可能靠近天线 ,将接 收到的模 拟信号尽早数

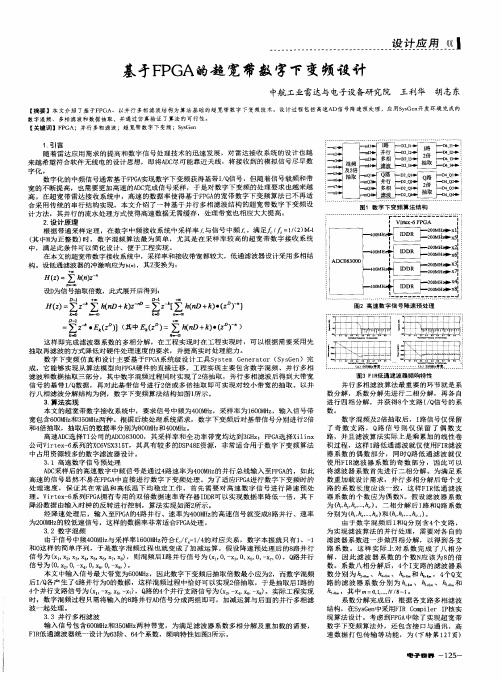

字化 。 数 字 化 的 中 频信 号 通 常 基 于F P G A 实现 数 字 下 变 频 获 得 基 带 I / Q 信 号 , 但 随 着 信 号 载 频 和 带 宽 的不 断提 高 , 也 需 要 更 加 高 速 的 A D C 完 成 信 号 采 样 ,于 是 对 数 字 下 变频 的 处 理 要 求 也 越 来 越 高 。在 超 宽 带 雷 达 接 收 系 统 中 , 高速 的 数 据 率 使 得 基 于 F P G A 的宽 带 数 字 下 变 频 算 法 己 不 再 适 合 采 用 传 统 的 串 行 结 构 实 现 ,本 文 介 绍 了一 种 基 于 并 行 多 相 滤 波 结 构 的 超 宽 带 数 字 下 变 频 设 计 方法 , 其 并 行 的 流 水 处 理 方 式 使 得 高 速 数 据 无 需缓 存 , 处理 带 宽 也 相 应 大 大 提 高 。 2 . 设 计原 理 根 据 带 通 采 样 定 理 ,在 数 字 中 频 接 收 系 统 中 采样 率 与 信 号 中频 。满 足 / =1 / ( 2 ) M- 1

日 ( z ) :∑ h ( n ) z

月-

设D 为信 号 抽 取 倍 数 , 此式 展 开 后 得 到 :

D- J + ∞ D- 1 - 嘲

—4 0 0 M H I D D R _; l o 0 M H

图 2 高 一2 0 0 MH m l I  ̄ X 4

软件无线电中数字下变频实现方法

前沿技术数字通信D I G I TAL COMMUN I CAT I O N /2010 2软件无线电中数字下变频实现方法收稿日期:2009 09 29苗鹏豪,杨 超,李 征(兰州交通大学电子与信息工程学院,兰州730070)摘 要:介绍了软件无线电短波接收机中数字下变频(di g ita l down conversi on ,DDC)的基本原理和应用,以及数字下变频的一般结构。

DDC 主要是将中频信号和NCO 产生的载波信号进行混频,再经过LPF 虑除高频分量得到基带信号,从而实现下变频的功能。

分别介绍了查表法和应用CORD IC 算法实现DDC 的过程。

关键词:软件无线电;数字下变频;数字控制振荡器;查表法;CORD I CR ealization of DDC m ethod i n soft ware radi osM I AO Peng hao ,YANG Chao ,LI Zheng(Coll ege of E l ectron i cs and I n for m ation Eng i neeri ng ,Lanzhou J i aotong Un i vers i ty ,L anz hou 730070,P .R .Ch i na)Abstrac t :Th i s paper introduces the basic pr i nciple and the appli cation o f dig ital do w n conversi on (DDC)based on so ft w are rad i o and t he g eneral structure of DDC .T he si gna l of i nter m ediate frequency and the s i gna l o f ca rr i e r wave w ere m i xed up i n t he DDC ,t he m i xed s i gna l passed through lowpass filter ,and t hus the f unc ti on o f down conversi on w as i m ple m en ted .T he pape r presen ts t he l ookup table and the process o f us i ng CORD IC to rea lize DDC .K ey word s :soft w are radio ;d i g ital down conversi on (DDC);nu m erica l con tro ll ed oscillator (NCO );l ookup tab l e ;CORDIC0 引 言在1992年美国远程通信系统会议上,JoeM ito la 首次正式提出了 软件无线电 (soft w are defi n ed ra dio)的概念。

基于软件无线电的数字下变频原理和实现

1 引

言

2 基本思想

数 字变 频 技 术 是软 件 无 线 电的核 心技 术 之一 。

19 92年 5月 JeMil 在美 国 国家 远 程 系统会 o. t a o

议上首次提 出了软件 无线 电( o a ai) Sf r R d 的概 w t e o 念 。它 的基本 思想 即 数字 化 在 天 线 端 ( 者 无 限 接 或 近) 实现 , 而所有处理完全 由驻 留在高速数字信号 处理功能部件中的软件来完成。把硬件作为无线通 信的基本平台, 把无线 电信号 的数字化从基带 移向 中频( ) I 级最后移到射频 ( F 级 , F R ) 其宽带 A D A / / 转换器尽可能靠近天线( r , R ) 把尽可能多的无线通 信功能用软件定义。但受硬件发展水平 的限制 , 直 接射频采样 目 前还有一定 困难 , 以首选方案是在 所 中频 ( ) I 对模拟信号数 字化。经过模 拟混频将射 F 频信号变换到 中频上。然后在 中频 (F 带对宽带 I) 多信道信号 进行 带通采样 。根 据带 通采样 ( 欠采

t c n lg fs l i n. e h o o y o out o

Ke r s: ot a e r d o Dii ld w o v re ;n e me i t e u n y; a i e u n y y wo d S f r a i ; gt o n c n e tr I t r d a e f q e c R d o f q e c w a r r

YU U —xa e

( oeeo nom t nSi c n n i e n , a n n e i Tcnl y N n 10 9 C i ) C lg fr ai c ne dE gn r g N mi U i rt o eh o g , a g2 00 ,hn l fI o e a ei g v syf o a

数字下变频FPGA实现

I

时钟 重

配置

I_W

S W

Q 2选1 I_N BUS

MUX

多相滤波结

2

构的宽带滤 Q_W 选

M c

I Q_N

波器

1B

中频

IT

S

AD 信号

C

6645

NCO Q H

BP U 接口 输

S

出

开关

S

配置

至

FPGA EP2S60F672C4

I Q

I_N W

窄带滤

I

波器组 Q_N T

C

I_N Q_N

M 参数 U DDC X 参数

…

−2π −π −ω1 0 ω1 π 2π ω

(a)下变频前实信号频谱

X (e jω )

−ω1 0

ω

(b)复本振信号频谱

X (e jω )

A

…

…

−2ω1 0 2ω1

ω

(c)混频后的信号频谱

图 4 数字下变频完成的频谱搬移

2) 数字下变频器两种典型结构

a) 传统窄带数字下变频结构

图 5 传统窄带数字下变频结构

本系统的数据流程如图 1 所示,A/D 采样的中频模拟信号输出至 FPGA, FPGA 中的 VB-DDC 将中频信号下变频至基带,再通过 McBSP 接口将基带信号 传给 DSP 进行解调、功率谱估计等数字信号处理,最后 DSP 再将结果通过以太 网送至上位机 PC 进行显示。同时,VB-DDC 可通过 McBSP 接口接受上位机 PC 传来的配置参数,实现 DDC 的动态配置。

Receivers. The Variable-Bandwidth Digital Down-Converter (VB-DDC) ,which is suitable for Wideband Digital Receiver, is implemented in FPGA chip Stratix II EP2S60F672C4. The VB-DDC combines the advantages of traditional digital down-conversion architectures and poly-phase filter architectures, realizes efficient high-speed processing for input IF signal, and could configure the bandwidth of signal processing flexibly in a large range. Hardware test result shows the effectiveness of this design.

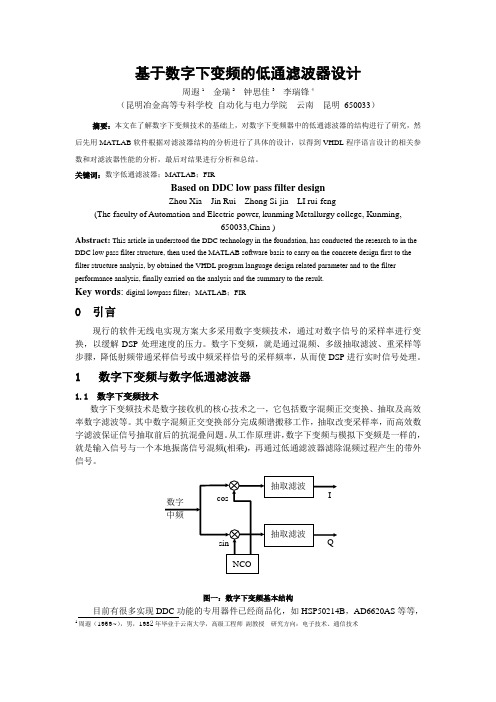

基于数字下变频的低通滤波器设计

基于数字下变频的低通滤波器设计周遐1金瑞2钟思佳3李瑞锋4(昆明冶金高等专科学校自动化与电力学院云南昆明650033)摘要:本文在了解数字下变频技术的基础上,对数字下变频器中的低通滤波器的结构进行了研究,然后先用MATLAB软件根据对滤波器结构的分析进行了具体的设计,以得到VHDL程序语言设计的相关参数和对滤波器性能的分析,最后对结果进行分析和总结。

关键词:数字低通滤波器;MA TLAB;FIRBased on DDC low pass filter designZhou Xia Jin Rui Zhong Si-jia LI rui-feng(The faculty of Automation and Electric power, kunming Metallurgy college, Kunming,650033,China )Abstract:This article in understood the DDC technology in the foundation, has conducted the research to in the DDC low pass filter structure, then used the MATLAB software basis to carry on the concrete design first to the filter structure analysis, by obtained the VHDL program language design related parameter and to the filter performance analysis, finally carried on the analysis and the summary to the result.Key words: digital lowpass filter;MATLAB;FIR0 引言现行的软件无线电实现方案大多采用数字变频技术,通过对数字信号的采样率进行变换,以缓解DSP处理速度的压力。

软件数字下变频技术研究

(ne oae e o d—od rp ln mi s ,a da I l r Itr ltd sc n p re oy o a ) n n F R ft . l ie

K yw r sSf aer i; i t o ncne e ; S P It o t eod—O dr oyo i s ; l rh e o d :o w r a o Dga dw o vr r IO (n r l e S cn t d il t e ad p re P l m a ) Agi m n l ot

灵 活性 、 应 性 。文 中指 出将 混频 、 取 、 波 结合 在 一起 完成 将 大 大 减 少运 算量 , 分 析 了将 CC 适 抽 滤 并 I

滤 波 器与 内插 的二阶 多项式 滤 波器组 合进 行 有 效抽 取 滤 波的 设计 方 案 , 真 结果表 明该 方案 有 效 可 仿

行 。

维普资讯

国 讥 技 22 第 期 0 年 5 0

文 章 编 号 :0 1 9 X(0 2 0 0 2 0 10 —83 2 0 }5— 0 7— 5

RSAC &DVI究 E发 EERH EEOM开 与N 研 P T

软 件 数 字 下 变 频 技 术 研 究

李 利 刘 向东

( 北 航 天 工 业 学 院 电子 工 程 系 , 北 廊 坊 050 ) 华 河 600

摘 要 : 文讨 论 了软 件 无线 电接 收机 中数 字下 变频 处理 的 高效 算 法 和结 构 , 目的 是 在 D P中用 本 其 S

软 件 完 成 数 字 下 变 频 处 理 , 样 可 省 去 专 用 数 字 下 变 频 器 ( D ) 件 集 成 电 路 , 增 强 中 频 处 理 的 采 用 欠 采 样 技 术 , 中

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

第九章数字下变频的设计数字下变频又称数字I、Q复解调。

它广泛应用于雷达、声纳和无线电接收机中。

数字下变频的原理已经在第一章和第八章得到阐述。

在本章中先介绍主要的数字下变频芯片,然后介绍数字I、Q复解调板的设计。

第一节主要的数字下变频芯片对于不同的厂商,数字下变频(digital down converter)芯片有时又被称为数字解调器(digital tuner)或数字接收信号处理器(digital receive signal processor) 。

目前世界上生产数字下变频芯片的厂家主要有GrayChip、Harris Semiconductor、Analog Device、National Semiconductor等,其中GrayChip公司虽然是一个小公司,但它却是一个专门生产数字下变频ASIC芯片的专业公司。

其生产的品种多、功能全、是选择数字下变频芯片的首选公司。

Harris公司生产数字下变频芯片的历史也较长。

由于其具备产生高速A/D变换器的功能,所以其数字下变频芯片和ADC芯片配合良好,可以配套使用。

由于软件无线电技术的发展和市场对数字接收机的大量需求,近几年来,半导体芯片的头号厂商Analog Device和National Semiconductor也涉足数字下变频芯片市场,并且发展势头非常迅猛。

特别是生产ADC芯片的龙头老大Analog Device公司,凭借其雄厚的模拟和数字电路芯片的设计和生产技术,开发了先进的数字接收器芯片AD6620和AD6624。

与此同时,Analog Device公司还将其新一代中频A/D转换器芯片和DSP芯片与其数字下变频芯片相结合,提出了多套完整的数字接收机的完整解决方案。

表9-1-1是市场上常用的数字下变频芯片。

表9-1-1 常用的数字下变频芯片的对照表名称AD6620 HSP50214 CLC5902 GC1012A生产厂家ADI Harris NS Graychip 输入数据宽度16bit 16bit 16bit 12bit输入数据速率65MHz 52MHz 52MHz 80MHzNCO精度0.02Hz 0.02Hz 0.02Hz 0.1HzCIC5 CIC4 无CIC滤波器CIC2CIC5固定系数FIR系数FIR RAM系数FIR1,FIR滤波器 RAM系数FIR RAMFIR2随着软件无线电的发展,通信、雷达、声纳等领域将需要更多的数字下变频芯片,从而也会出现更多的新芯片和厂家。

9-1-1. 窄带数字下变频芯片AD6620AD6620数字接收器芯片主要由四部分组成,如图9-1-1所示,包括一个频率转换部分(NCO和混频器)、两个固定系数的抽选滤波器、一个程控系数的抽选滤波器。

图9-1-1 AD6620的功能框图AD6620的多种数据输入输出方式设计使其能非常方便地连接高速ADC芯片和通用DSP 芯片。

其输入接口可接受16位基数,3位指数输入,并且还有A/B选择输入。

这样可使它具备三种输入方式:单通道实模式(real),单通道复模式(complex)和多通道实模式(real)。

高精度的NCO可以使AD6620能从高速数据流中选择出一个单个载波。

其滤波器不仅具有大范围的抽选比,而且动态范围大,适用于窄带和宽带载波的提取。

它的基于RAM的可编程系数滤波器可适用于多种模式的应用,如抗混叠、匹配滤波、静态均衡功能等。

AD6620的主要性能指标如下:高速数据输入率:65MHz 单通道实模式(single channel real)32.5MHz 单通道复模式 (single channel complex)32.5MHz 多通道实模式(diversity channel real)NCO性能:最小伪波(worst spur)小于 –100dBc最小频率精度 0.02Hz2阶CIC滤波器:线性相位,固定系数程控抽取因子:2, 3, …16.5阶CIC滤波器:线性相位,固定系数程控抽取因子:1, 2, 3, …32.程控抽取、RAM系数FIR滤波器256个20bit可程控系数程控抽取因子:1, 2, 3, …32.多种数据输出方式:输入管脚设置选择串口或并口输出方式串口输出与大多数DSP串口输入相匹配16位I、Q交替并行输出两个独立的控制与配置端口:通用微处理器端口通用串口AD6620的内部各部分结构如图9-1-2所示,其中数据输入可以是16位整数形式,输入到IN[15:0];也可以是浮点数形式,基数输入到IN[15:0],指数输入到EXP[2:0]。

NCO由一个32bit 数控制,产生不同的频率。

通过乘法器产生I、Q两路,并把中频转换到基带。

图9-1-2 AD6620的内部结构NCO的初始相位是可以设置的,并且它有相位和幅度dither使能功能,一旦dither功能打开,可以使NCO的SFDR性能提高。

紧接着NCO和频率转换器(混频器)的是一个2阶CIC 滤波器,它的抽选比可设置为2到16,它的滤波器频率响应和输出数据速率都是由抽选因子M CIC2决定的。

在CIC2后的第二个固定系数的滤波器是一个5阶CIC滤波器。

它的抽选比是1到32,它的滤波器频率响应和输出数据速率也是由抽选因子M CIC5所决定。

前面的CIC滤波器实际上也是一种结构简单的FIR滤波器。

它们的主要作用是降低输入信号的速率。

这样,最后一级RAM系数FIR滤波器(RCF)就可以在每次输出时计算更多的次数,以实现更高的阶数。

从图9-1-2中可以看出,对于每路RCF滤波器,其乘法器只有一个,因此,每个时钟周期只进行一次乘法运算。

所以,要使RCF成为高阶FIR滤波器,前面两级CIC滤波器必须进行抽选,使输入到RCF的数据速率降低,即多个时钟周期输入一个数据。

这样RCF就有时间完成高阶滤波运算。

从图9-1-2中还能看到,两路RCF滤波器是公用一组RAM系数的。

这就是说,两路的滤波特性是完全一样的。

RCF的系数是20bit数,最多存放256个,因此,RCF的最大阶数是256。

然而,很少有用到256阶FIR滤波器的情况。

这时,这256个系数可以进行分组,以构成多个不同频率响应的滤波器,通过软件设置来选用其中不同的滤波器系数。

总之,AD6620总的滤波特性是CIC2、CIC5、RCF三个滤波器频率响应的乘积。

CIC滤波器实现起来简单,但频率响应较差,其过渡带较长。

RCF的频率响应好,能实现很陡的过渡带,且通带平整,阻带衰减大,其缺点在于需进行大量的乘加运算,难以实现高速数据率下的滤波。

图9-1-3是CIC和RCF滤波器频率响应特性。

由于AD6620结合了CIC和RCF两种滤波器,通过软件设置,使其能适用于许多应用场合。

图9-1-3 CIC和RCF滤波器频率响应9-1-2. 宽带数字下变频芯片GC1012AGC1012A是Graychip公司的高速宽带数字下变频芯片。

它的输入数据的最高速率是80MHz,即能处理的输入信号带宽高达40MHz。

输出数据速率由抽取因子D来决定。

对于复模式输出方式,D可以设置为1、2、4、8、16、32和64,输出速率F O=F CK/D,F CK是输入数据时钟。

对于实模式输出方式,D可以设置为2、4、8、16、32和64,输出速率F O=2F CK/D。

与AD6620不同的是GC1012A内部只有一个40阶的FIR滤波器。

数据先由滤波器滤波再进行抽取。

GC1012A的内部结构如图9-1-4所示。

图9-1-4 GC1012A的内部结构NCO的频率由一个28位的累加器来控制,其频率调节精度等于输入时钟频率除以228。

所以,对于输入时钟频率为50MHz,其NCO频率调节精度为±0.1Hz。

NCO的无伪波动态范围(SFDR)超过75dB。

由于GC1012A是一个宽带数字下变频芯片,其数据输出速率比较高,只能采用并行输出方式。

输出数据的增益也可以调节,最小调节步长是0.03dB,输出数据的宽度可以设置为10,12,14和16位。

GC1012A的配置和控制通过一个通用微处理器I/O来实现,其中包括8位数据线,4位地址线,一根读/写线和一根控制线。

GC1012A的主要性能指标如下:80MHz数据输入速率0.1Hz NCO频率分辨率>75 dB 动态范围可控数据输出宽度: 12位输入数据宽度; 10、12、14或16位输出数据宽度实模式或复模式数据输出方式增益调节步长 0.03dB微处理器控制和配置接口GC1012A实现宽带滤波在于其拥有一个高阶(40阶)的FIR滤波器。

滤波器的系数是固化在芯片中的,因此,其频率响应也是固定的,图9-1-5所示的是抽取率为2时的滤波器频率响应。

Graychip 公司也可以根据用户的要求在芯片中固化其他的滤波器系数。

图9-1-5 滤波器的频率响应滤波器的通带纹波是0.13dB,阻带衰减大于75dB。

2dB输出带宽是±0.4Fs(即80%的带宽利用率),这里Fs是复模式数据输出速率。

0.1dB输出带宽是±0.36Fs(即72%的带宽利用率)。

从图3-3-5中可以看出,滤波器具有一个非常快的过渡带,在过渡带滤波器很快地下降到60dB,并维持75dB以下的阻带衰减。

9-1-3 用FPGA设计的数字下变频芯片由于数字下变频ASIC芯片具有价廉、功耗小、体积小和使用方便等特点而得到广大工程师的青睐。

然而,通信、雷达等系统的应用非常广泛,有时会对数字下变频芯片提出某些特殊的要求,这时通用的数字下变频芯片就无法胜任。

这里主要指芯片中的FIR指标无法满足要求,如特殊滤波器的频带、通带纹波、阻带衰减等。

另外,有些应用对NCO的频率精度、数字下变频的输入输出数据宽度和运算精度也有要求,这样,就必须设计专用的数字下变频芯片。

专用的数字下变频芯片一般都需要更高的滤波器特性、更快的速度和更大的数据宽度。

这就要求用来设计数字下变频的FPGA或EPLD芯片有更大的容量和更快的速度。

目前Altera公司和 Xilinx公司的FPGA芯片的容量已超过100万门,时钟频率也超过100MHz,所以,尽管芯片的价格非常高,但设计专用的数字下变频芯片的硬件条件已经成熟。

在软件方面,Altera公司和 Xilinx公司都提供NCO和FIR设计的内核(Megacore Function),只要把两者结合起来,就可设计出满足要求的数字下变频芯片。

下面简单介绍一下Altera公司的FIR Megacore Function 。

FIR Megacore是专为采用Altera公司FPGA和EPLD芯片设计FIR的内核软件模块,它作为一个开发工具在MAX PLUS II或Quartus平台下运行。

在设计FIR时,只要先定义滤波器的输入输出数据宽度和内部数据位数,再定义滤波器的阶数、通带纹波、阻带衰减、截止频率、抽选率等参数,该软件模块就能自动地计算出滤波器的系数和频率响应,如图9-1-6所示。