基于FPGA的PCM30or32 路系统信号同步数字复接设计

两路语音PCM时分复用系统的设计

摘要数字通信系统是采用数字信号来传递信息的通信系统,数字通信过程中主要涉及信源编码与译码、信道编码与译码、数字调制与解调等技术问题。

而脉冲编码调制就是一种常用的信源编码方法,将模拟信号抽样、量化,直到转换成为二进制符号的基本过程。

为了扩大通信系统链路的容量,在一条链路上传输多路独立的信号,为此引入了一种复用技术来实现多路信号共同传输的目的。

而在本系统设计中,所运用的复用技术是时分复用,同时基于现场可编程门阵列器件作为主控芯片,在Quartus II软件中使用硬件描述语言Verilog HDL编写PCM编译码和时分复用模块的程序,再对其进行波形仿真以验证程序的正确性,从而设计出语音信号的PCM编码与译码、时分复用的过程。

本设计中,将两路语音信号通过外围硬件电路模块送至FPGA中进行PCM编码、译码处理,最后通过后级外围电路实现语音信号的重现。

关键词:语音脉冲编码调制时分复用FPGADesign of Two-way V oice PCM Systemby Time Division MultiplexingABSTRACT A digital communication system is a communication system that transmit information by using digital signal, and digital communication mainly relates to the source coding and decoding, channel coding and decoding, digital modulation and demodulation technology. Pulse code modulation is a common source coding, and it is that the analog signal sampling ,quantization ,until the transformation become the basic process of binary symbols. In order to expand the capacity of communication link system ,a transmission of multiple independent signal on a link, therefore introduction of a division multiplexing technology to achieve the purpose of multiplexing.In this system design, we use a time division multiplexing technology, and based on the Field Programmable Gate Array, using Verilog HDL hardware description language to write PCM encoding and decoding and time division multiplexing module in Quartus II, then Waveform simulation to verify the correctness of the program, thus design a voice signal process of PCM encoding and decoding, time division multiplexing. In this system design, The two-way voice signal through the peripheral hardware circuit module is sent to the FPGA for PCM encoding and decoding, finally to achieve reproducible speech signal through the peripheral circuit. Key Words:V oice Pulse code modulation Time division multiplexing FPGA目录摘要 (I)ABSTRACT........................................................... I I 目录1 引言 (1)1.1 选题背景与意义 (1)1.2 QuartusⅡ软件 (2)1.3 FPGA的介绍 (3)1.4 本文内容简介 (4)1.5 实施过程简介 (4)1.6 设计结果简介 (4)2 基本原理介绍 (5)2.1 模拟信号的数字化 (5)2.1.1 采样定理 (5)2.1.2 量化原理 (5)2.1.3 A律13折线 (5)2.2 脉冲编码调制 (7)2.3 时分复用技术 (9)2.4 PCM一次群帧结构 (10)3 系统设计介绍 (11)3.1 总体框图 (11)3.2 外围硬件电路的介绍 (12)3.2.1 拾音电路 (12)3.2.2 仪用放大器 (12)3.2.3 带通滤波器 (13)3.2.4 抬升电路 (13)3.2.5 A/D转换电路 (14)3.2.6 D/A转换电路 (14)3.2.7 功率放大器 (15)3.3 基于FPGA的模块设计 (16)3.3.1 系统时钟的设计 (16)3.3.2 前端模块设计 (16)3.3.3 后级模块设计 (18)3.3.4 同步时钟的提取 (20)3.3.5 整体FPGA系统原理框图 (20)4 设计的结果 (21)致谢 (22)参考文献 (22)附录 (23)1 系统实物图 (23)2 FPGA中主要模块程序 (24)1 引言1.1 选题背景与意义在当今信息化极其高度的社会,信息和通信已经与现代社会的发展密不可分。

通信原理-选择题(26)

2011年1月一、单项选择题(本大题共15小题,每小题1分,共15分)1.衡量数字通信系统可靠性的主要指标是( )A.信息传输速率B.符号传输速率C.频带利用率D.误码率2.PCM通信系统实现非均匀量化的方法目前一般采用( )A.模拟压扩法B.直接非均匀编解码法C.自适应法D.非自适应法3.样值的绝对值相同其幅度码不相同...的为( )A.一般二进码B.折叠二进码C.格雷码D.折叠二进码和格雷码4.PCM30/32路系统传输复帧同步码的位置为( )A.F0帧TS16前4位码B.F0帧TS16后4位码C.F1帧TS16前4位码D.F l帧TS16后4位码5.PCM30/32路系统标志信号的抽样周期为( )A.T(=125μs) B.2TC.15T D.16T6.帧同步码码型的选择主要考虑的因素是( )A.产生容易,以简化设备B.捕捉时间尽量短C.产生伪同步码的可能性尽量小D.以上都不是7.数字复接中的同步指的是( )A.收、发定时同步B.收、发各路信号对准C.二次群的帧同步D.各低次群数码率相同8.异步复接二次群一帧中的码速调整用的插入码有( )A.4bit B.12bitC.0~4bit D.28bit9.PCM异步复接二次群的帧长度为( )A.848bit B.820bitC.256bit D.212bit10.PCM一次群的接口码型为( )A.HDB3码B.AMI码C.CMI码D.HDB3码或CMI码11.可以采用1+l保护方式的自愈环有( )A.二纤单向通道倒换环B.二纤双向通道倒换环C.二纤单向复用段倒换环D.二纤单向通道倒换环和二纤双向通道倒换环12.没有误码增殖的基带传输码型是( )A.AMI码B.CMI码C.HDB3码D.AMI码和CMI码13.再生中继系统的特点为( )A.无噪声积累B.有误码率的积累C.无误码率的积累D.无噪声积累和有误码率的积累14.数字通信系统(传送话音信号)误码率应低于( )A.10-5B.10-6C.10-7D.10-815.光纤数字传输系统属于( )A.频带传输B.基带传输C.数字数据传输D.无线传输2010年10月一、单项选择题(本大题共15小题,每小题1分,共15分)1.传送话音信号的基带传输系统模型中( )A.无信道编码和调制B.无信道编码、有调制C.有信道编码、无调制D.有信道编码和调制2.某数字通信系统传输l0000000个码元,其中误1个码元,误码率为( ) A.10-4B.10-5C.10-6D.10-73.抽样后的PAM信号的特点是( )A.幅度和时间均连续B.幅度连续、时间离散C.幅度离散、时间连续D.幅度和时间均离散4.解决均匀量化小信号的量化信噪比低的最好方法是( )A.增加量化级数B.增大信号功率C.采用非均匀量化D.降低噪声功率5.样值的绝对值相同其幅度码也相同的码型为( )A.一般二进码B.折叠二进码C.格雷码D.折叠二进码和格雷码6.A律13折线编码器输出的码型是( )A.RZ码B.NRZ码C.AMI码D.HDB3码7.PCM30/32系统第18路信令码的传输位置(即在帧结构中的位置)为( ) A.F3帧TS16的前4位码B.F3帧TS16的后4位码C.F4帧TS16的前4位码D.F4帧TS16的后4位码8.PCM30/32系统复帧同步码的码型为( )A.001101l B.0110110C.0000 D.11119.DPCM是属于( )A.参数编码B.波形编码C.子带编码D.纠错编码10.按SDH标准速率STM-4的速率是( )A.2.048Mb/s B.155.520Mb/sC.622.080Mb/s D.2488.320Mb/s11.PCM四次群的接口码型为( )A.AMI码B.HDB3码C.NRZ码D.CMI码12.SDH中继网适合采用的拓扑结构为( )A.网形B.线形C.星形D.环形和线形13.可用于数字信号基带传输的信道为( )A.电缆信道B.光缆信道C.卫星信道D.微波信道14.再生中继系统中的升余弦波的特点是( )A.无码间干扰、均放特性不易实现B.有码间干扰、均放特性不易实现C.无码间干扰、均放特性容易实现D.有码间干扰、均放特性容易实现15.属于频带传输系统的有( )A.ADPCM系统B.数字微波传输系统C.数字卫星传输系统D.数字微波传输系统和数字卫星传输系统2010年1月一、单项选择题(本大题共15小题,每小题1分,共15分)1.人讲话的语声信号为( )A.模拟信号B.数字信号C.调相信号D.调频信号2.脉冲编码调制信号为( )A.模拟信号B.数字信号C.调相信号D.调频信号3.均匀量化的特点是( )A.量化间隔不随信号幅度大小而改变B.信号幅度大时,量化间隔小C.信号幅度小时,量化间隔大D.信号幅度小时,量化间隔小4.A律13折线压缩特性中的第7段线的斜率是( )A.0.5B.1C.4D.165.PCM30/32系统中对每路信号的抽样帧频率是( )A.8kHzB.16kHzC.64kHzD.2048kHz6.STM—16的一帧的字节数为( )A.9×270×lB.9×270×4C.9×261×16D.9×270×167.PCM30/32系统复帧的周期是( )A.125sμB.250sμC.1msD.2ms8.异步复接在复接过程中需要进行( )A.码速调整和码速恢复B.码速恢复C.编码方式变换D.码速调整9.PCM30/32系统发送帧同步码的周期是( )A.125sμB.250sμC.500sμD.1ms10.以下4种传输码型中含有直流分量的传输码型是( )A.双极性归零码B.HDB3码C.AMI码D.单极性归零码11.PCM30/32系统发送复帧同步码的周期是( )A.125sμB.250sμC.1msD.2ms12.对SDH网络同步而言,在SDH网络范围内正常的工作方式是( )A.伪同步方式B.准同步方式C.同步方式D.异步方式13.样值为513∆,它属于A律13折线的(l=8)( )A.第4量化段B.第5量化段C.第6量化段D.第7量化段14.PCM一次群的接口码型为( )A.RZ码B.AMI码C.CMI码D.HDB3码15.A律13折线编码器量化级数N越大,则( )A.小信号时量化信噪比越小B.小信号时量化信噪比越大C.折叠噪声越小D.折叠噪声越大2009年10月一、单项选择题(本大题共15小题,每小题1分,共15分)1.A律13折线压缩特性中最靠近零点的第1段线的斜率是()A.128 B.64C.32 D.162.PCM30/32系统发送帧同步码的频率是()A.4kHz B.16kHzC.64kHz D.2048kHz3.下列编码方法中不属于...波形编码的是()A.PCM B.ADPCMC.子带编码D.DPCM4.以下4种传输码型中含有直流分量的传输码型是()A.双极性归零码B.HDB3码C.AMI码D.CMI码5.异步复接在复接过程中需要进行()A.码速调整B.码速恢复C.码速变换D.码速变换和码速恢复6.样值为444∆,它属于A律13折线的(l=8)()A.第4量化段B.第5量化段C.第6量化段D.第7量化段7.数字信号的特点是()A.幅度取值是离散变化的B.幅度取值是连续变化的C.频率取值是离散变化的D.频率取值是连续变化的8.PCM30/32系统复帧的频率是()A.500Hz B.1kHzC.64kHz D.2048kHz9.模拟信号的特点是()A.幅度取值是离散变化的B.幅度取值是连续变化的C.频率取值是离散变化的D.频率取值是连续变化的10.同步复接在复接过程中需要进行()A.码速调整B.码速恢复C.码速变换D.码速调整和码速恢复11.非均匀量化的特点是()A.量化间隔不随信号幅度大小而改变B.信号幅度大时,量化间隔小C.信号幅度小时,量化间隔大D.信号幅度小时,量化间隔小12.STM-1的一帧的字节数为()A.9×270×1 B.9×270×4C.9×261×4 D.9×270×1613.SDH的复用采用()A.同步复用、按比特间插B.同步复用、按字节间插C.异步复用、按比特间插D.异步复用、按字节间插14.语声数字通信质量与误码率()A.成正比B.成反比C.相等D.无关15.PAM信号为()A.模拟信号B.数字信号C.调相信号D.调频信号2009年1月一、单项选择题(本大题共15小题,每小题1分,共15分)在每小题列出的四个备选项中只有一个是符合题目要求的,请将其代码填写在题后的括号内。

PCM

目录一、设计总体思路及方案确定 (1)1、设计总体思路 (1)2、方案确定 (1)二、时分复用原理 (3)三、模块设计 (4)1、帧同步模块 (4)2、时钟电路模块 (4)3、分频电路模块 (5)4、抽样信号产生电路模块 (6)5、PCM编译码单元电路模块 (7)四、电路调试、系统仿真 (9)1、电路调试 (9)2、系统仿真 (10)五、附录(总电路原理图) (15)六、心得体会 (16)七、参考文献 (17)一、设计总体思路及方案确定1、设计总体思路本次课题设计一时分复用通信系统,采用30/32路PCM时分复用系统实现帧码及两路模拟正弦信号的复接数字系统。

PCM时分复用数字基带传输,是各路信号在同一信道上占有不同的时间间隙进行通信。

它把模拟信号通过抽样、量化、编码转变为数字信号,然后在位同步和帧同步信号的控制下通过复接器实现复接,复接后的信号通过信道传输,分接器在同步信号的作用下把接收到的信号进行分路,分路后的信号通过PCM译码、低通滤波器还原出输入的模拟语音信号。

先将模拟正弦信号进行数字化,因为数字信号有着模拟信号所不可比拟的优点:结构简单,抗干扰性强,易整形、再生和占用带宽较宽等属性,特别是基于二进制的系统更是具有设备简单,抗干扰性好,噪声不累积,复用方式先进和灵活多样,易加密,安全可靠等先天性优点。

2、方案确定要求输入为模拟正弦信号,要使这样的信号在数字通信系统中或数字信道中传输,必须将模拟信号转换为数字信号。

脉冲编码调制(PCM)技术与增量调制(△M)技术已经在数字通信系统中得到广泛应用。

当信道噪声比较小时一般用PCM,否则一般用△M。

而△M在国际上无统一标准,但它在通信环境比较恶劣时显示了巨大的优越性。

而△M在比特率较高时信噪比较低,达不到语音通信的要求。

因此,在此系统的设计中采用PCM 方式。

非均匀量化的具体办法是压缩、扩张法,即在发送端对抽样信号先进行压缩处理再均匀量化,压缩器特性曲线在小信号时的斜率大,大信号时的斜率小,使抽样信号的小样值部分被充分放大,大样值部分被适当压缩。

实验5两路PCM时分复用

信号源:同步正弦波(2K)

模块8:FS3 模块8:FS_SEL 模块2:PCMOUT-A 模块2:PCMOUT-B

模块2:SIN IN-A;SIN IN-B

模块2:FSXA 模块2:FSXB 模块8:PCMAIN 模块8:PCMBIN

PCM编码输入信号

A路PCM编码帧同步输入 B路PCM编码帧同步输入 A路PCM编码输入信号 B路PCM编码输入信号

同步提取输入提取的位同步输入提取的帧同步输入pcm解码输入信号pcm解码输入信号路pcm解码帧同步输入路pcm解码帧同步输入1拨码开关s4s5都拨为01000404拨码开关s1s拨为0000103用示波器观测sin4用示波器观测sininbsinoutbinasin码帧同步输入两点的波形并进行比较结束结束结束outa两点的波形并进行比解复用输出bpcm译码位同步输入解复用输出a1用示波器观测pcmainpcmouta两点的波形并进行比较路解码帧同步输入2用示波器观测pcmbinpcmoutb点的波形并进行比较解复用输入保持前面连线继续解复用连线同步提取输入触发按钮看连线位同步输入返回波形帧同步输入保持前面连线继续解复用连线五实验步骤两人时分复用通话实验1保持以上连线不变拆除信号源模块保持以上连线不变拆除信号源模块2k步正弦波与模块2的连线增加以下连线

1、分别接两副耳麦的话筒耳机

2、调节W1W2W3W4改变通话音量及质量, 解码后2路语音信号输出 进行两人通话(结束)

六、实验报告要求

1、实验目的

2、实验内容 3、实验器材 4、实验原理 5、实验步骤 6、实验结果及分析

五、实验步骤

2、将两副耳麦分别接入模块2上的耳机插座:

“话筒1”“耳机1”“话筒2”“耳机2”,进行两人通 化实验,调节电位器W1、W2、W3、W4改变音 量及通话质量。 3、实验结束关闭电源,拆除连线,完成实验 报告。

第3章时分多路复用及PCM3032路系统

图3-16 帧同步系统工作流程图

图中A表示帧同步状态;B表示前方 保护状态;C表示捕捉状态;D表示后方 保护状态。

图中PS 为帧同步码标志;PC 为收端产 生的比较标志。

4.帧同步码型与长度

在选择帧同步码组结构时,要考虑 由于信息码而产生伪同步码的概率越小 越好。

如果增加帧同步码组的码位数,可

3.2.1 PCM30/32路系统帧结构

PCM30/32系统的帧周期是125 s,

每一帧由32个时隙组成,每个时隙对应1 个样值,1个样值编8位码。

图3-10 PCM30/32路系统帧结构

1.30个话路时隙:TS1∽ TS15 ,TS17∽TS 31

TS1∽ TS15 分别传送第1∽15路( CH1 ∽ CH15 )话音信号,TS ∽ 17 TS 31 分别传送 第16∽30路( CH16 ∽CH 30)话音信号。

为了提高通信信道的利用率,使信 号沿同一信道传输而不互相干扰,这种 通信方式称为多路复用。

目前多路复用方法中用得最多的有 两大类:频分多路复用(FDM)和时分 多路复用(TDM)。

频分多路复用方式用于模拟通信; 时分多路通信方式用于数字通信,例如 PCM通信。

2.时分多路复用的概念

所谓时分多路复用(即时分制)是 利用各路信号在信道上占有不同的时间 间隔的特征来分开各路信号的。

因此用户的话音信号需要经过2/4线 变换的差动变量器,经1 2端送入PCM 系统的发送端。

差动变量器1 2端与4 1端的传输 衰减要求越小越好,但4 2端的衰减要 求越大越好,以防止通路振鸣。

话音信号再经过放大(调节话音电

平)、低通滤波(限制话音频带,防止 折叠噪声的产生)、抽样和路及编码。

其抽样周期为 1 125s 16 16T (T 125s), 而且信令信号抽50样0 后只编4位码。

PCM30_32路基群帧同步电路的VHDL设计

— — — 以下为逐比特搜寻第一个偶帧同步码 — — — 已接收到 8 位串行输入数据 — — — 记录已连续正确检测到一个帧同步码 — — — 标记连续未正确检测到帧同步码次数 — — — 以下采取逐帧搜寻同步码 — — — 以下搜寻奇帧同步码

) THEN — IF ( even = ′ 1′ AND odd = ′ 0′ — — 以下检测搜寻到的是否为偶帧同步码 IF ( q = " 10011011" ) THEN keep: = keep + 1; IF ( loss < = 3 ) THEN loss: = 0; END IF; IF ( keep > = 3 ) THEN keep: = 3; floss < = ′ 1′ ; — — — 连续 3 帧均正确检测到同步码 ,则电路转为同步态 ELSE floss < = ′ 0′ ; END IF; ELSE loss: = loss + 1; IF ( keep < = 2 ) THEN — — — 连续正确检测到同步码的次数还不到 3 次 ,又未能正

说明 : 以上波形中 , clk、 data为按要求所加的系统激励信号 , reset为系统异步复位信号 , 高电平使系 μ s) , 统进入初始状态 ,做好检测第一个偶帧同步码的准备 。输入激励信号 data 共有十帧 (每帧持续 125 μs, 每帧前八位加入的时序为 : 偶帧同步码 、 持续 1250 偶帧同步码 、 偶帧同步码 、 奇帧同步码 、 偶帧同步 码、 奇帧同步码 、 无同步码 、 无同步码 、 无同步码 、 无同步码 。从以上系统功能测试波形可以看出本文的 VHDL 设计完全满足系统功能要求 。

第 24 卷 许开华 唐 广 : PCM30 /32 路基群帧同步电路的 VHDL 设计 第 3期

基于FPGA的多路数字信号复接系统设计与实现

基于FPGA的多路数字信号复接系统设计与实现摘要数字复分接技术是数字通信网中的一项重要技术,能将若干路低速信号合并为一路高速信号,以提高带宽利用率和数据传输效率。

文中在介绍数字复接系统的基础上,采用VHDL对数字复分接系统进行建模设计和实现。

并利用乒乓操作和先进先出存储器(FIFO)对复接器进行设计,利用帧同步器对数据进行分接。

以QuartusII8.0为仿真软件,对设计进行仿真验证,仿真结果表明,设计实现了复接系统,便于修改电路结构,增强了设计的灵活性,且节约了系统资源。

数字通信系统中,为了提高信道的利用率,使多路信号在同一条信道上传输时互相不产生相干的方式称为多路复用。

在时分复用中,将时间划分为若干时隙,各路信号在时间上占用各自的时隙,即多路信号在不同时间内被传送,各路信号在时域中互不重叠。

数字复接终端是将若干低速率码流变换成一路高速率码流的设备。

应用可编程逻辑门阵列(FPGA)芯片实现复接系统便于修改电路结构,增强了设计的灵活性,并节约了系统资源。

1 多路复接系统设计要求(1)实现两路数据的同步复接。

(2)支路速率为32 kbit·s-1。

(3)按位复接。

(4)帧同步码字为10 bit:“1 0 1 1 0 1 0 01 1”。

(5)帧长128 bit。

2 数字复接系统基本原理2.1 数字复接系统数字复接终端的作用是将低速数据码流变换成高速数据码流的设备。

将两个或两个以上的支路数字信号按时分复用方式合并成单一的合路数字信号的过程称为数字复接;完成数字复接功能的设备称为数字复接器;在接收端将一路复合数字信号分离成各支路信号的过程称为数字分接。

数字复接器、数字分接器和传输传道共同构成了数字复接系统。

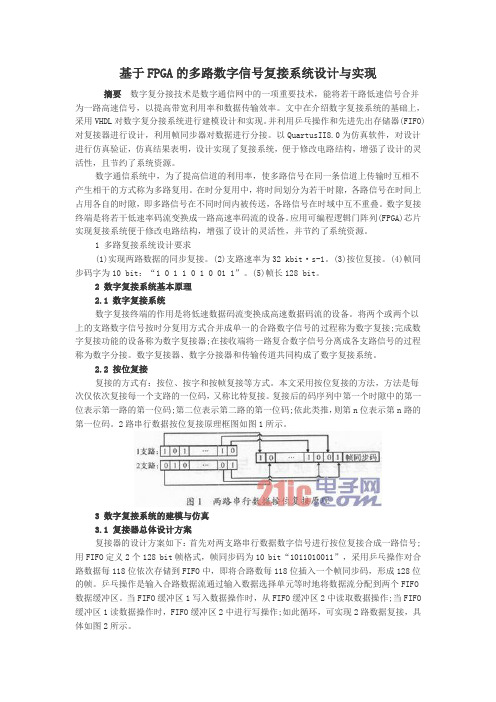

2.2 按位复接复接的方式有:按位、按字和按帧复接等方式。

本文采用按位复接的方法,方法是每次仅依次复接每一个支路的一位码,又称比特复接。

复接后的码序列中第一个时隙中的第一位表示第一路的第一位码;第二位表示第二路的第一位码;依此类推,则第n位表示第n路的第一位码。

通信多路复用的方法及3032路PCM帧结构

通信多路复用的方法及30/32路PCM帧结构通信系统包括发送设备、接收设备和传输设备. 传输线路投资往往占整个通信系统投资的很大比例,因此,如何提高线路利用率,实现传输线路的多路复用,就成了一个非常重要的话题。

1 多路复用的方法多路复用通常有3种基本方法:频分复用(FDMA),码分复用(CDMA)和时分复用(TDMA)。

1.1 频分复用频分复用是模拟通信中广泛使用的传输方式,它的基本原理是利用调制手段和滤波技术使多路信号以频率分割的方式同时在同一条线路上互不干扰地传输。

1.2 码分复用码分复用是指在同一条信道上,多路信号以不同的编码形式互不干扰的传输。

它目前已成为移动通信中使用的先进方法。

1.3 时分复用时分复用是现代数字通信中主要采用的传输方式,时分多路复用就是在一条信道内,将若干路离散信号的脉冲序列,经过分组、压缩、循环排序,成为时间上互不重叠的多路信号一并传输的方式。

例如两地有许多用户要进行通信,用户11—用户12,用户21—用户22……用户n1—用户n2。

可是线路只有一对,于是在收发双方各加了一对快速旋转的电子开关SA1和 SA2(这两个开关实际就是一组抽样门和分路门,它们的开闭受抽样脉冲控制),SA1、SA2旋转频率相同,初始位置相互对应。

我们称之为同步动作。

开始,SA1和SA2停留在用户11和用户12上,然后依次旋转到21和22上、31和32上,n1和n2 上,最后又回到11和12上,如此反复。

目前世界上的数字时分多路复用系统主要有北美、日本的24路PCM系统和欧洲、中国的30/32路PCM系统。

下面主要介绍30/32路PCM系统。

2 30/32路PCM基群帧结构2.1 帧结构帧结构的概念就是把多路话音数字码以及插入的各种标记按照一定的时间顺序排列的数字码流组合。

我国采用的是30/32路PCM基群结构,即在传输数据时先传第1路信号,然后传第2路信号,第3路信号……直到传完第32路,再传第1路,第2路……如此循环下去。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

基于FPGA的PCM30/32路系统信号同步数字复接设计摘要:在现代数字通信系统中,为了扩大信道的传输容量提高信号传输效率,常采用数字复接的技术。

在分析了PCM30/32路系统基群信号帧结构的基础上,以EDA综合仿真设计软件QuartusⅡ8.0为开发平台,利用Verilog HDL硬件描述语言进行系统建模,设计了一种基于FPGA的同步数字信号复接系统。

经过对系统的功能仿真测试及综合布局布线分析,验证了输入/输出的逻辑关系,实现了系统中在发送端进行数字复接和接收端同步分解还原的设计要求,功能稳定可靠。

0 引言数字通信系统包括发送设备、接收设备和传输设备,在现代数字通信中,为了扩大信道传输容量提高传输效率,通常需要将若干低速数字码流按一定的规范复接为一个高速数据码流流,以便在高速宽带信道中传输。

目前采用较多的技术是频分多路复用和时分多路复用,频分多路复用适用于模拟通信,例如载波通信;时分多路多复用适用于数字通信,例如PCM通信。

数字复接技术就是依据时分复用的基本原理完成数据码流合并和分解还原的一种专门技术,并且是数字通信中的一项基础技术。

以往的数字复接系统大多采用模拟电路或传统的ASIC设计,电路复杂庞大且受器件局限性约束;由于近年来基于FPGA可编程器件的电路设计发展迅速,可方便反复编写和修改主程序及相关参数,灵活性和稳定性都很高。

本文以我国广泛应用的PCM30/32基群数字信号为例,介绍这种基于FPGA流程设计的同步数字信号复接和分解方案,使用EDA仿真设计工具QuartusⅡ和Verilog HDL硬件描述语言对数据复接和分解的关键步骤进行功能仿真和验证。

1 PCM30/32路系统帧结构介绍时分复用的基本原理是将时间段分割成若干路时隙,每一路信号分配一个时隙,帧同步码和其他业务信号、信令信号再分配一个或两个时隙,这种按时隙分配的重复性比特即为帧结构。

在PCM30/32路基群设备中是以帧结构为单位,将各种信息规律性地相互交插汇成2048Kb/s的高速码流。

PCM30/32路系统的整个系统共分为32个路时隙,其中30个路时隙分别用来传送30路话音信号,一个路时隙用来传送帧同步码,另一个路时隙用来传送信令码。

PCM30/32路系统中一个复帧(1复帧时间为2 ms)包含16帧,编号分别为F0帧,F1帧,F2帧,…,F15帧,每帧(每一帧的时间为125μs)又包含有32个路时隙,其编号为TS0,TS1,TS2,…,TS31,每一路时隙时间为3.9μs,包含有8个位时隙,其编号分别为D1,D2,…,D8,每个位时隙的时间为0.488μs。

其中TS1~TS15及TS17~TS31共30个时隙用于传送第1~30路的信息信号。

偶帧的TS0时隙传送帧同步码,其码型为{×0011011};奇帧TS0时隙用于传送帧失步对告和监视告警码等,码型为{×1A1SSSSS}。

TS16时隙用于传送复帧同步信号、复帧失步对告及各路的信令(挂机、拨号、占用等)信号,当TS16用于传随信令时,它的安排是子帧F0的TS16时隙用于传复帧失步对告码及复帧同步码,F1子帧的TS16时隙传送第1路和第16路的信令信号,F2子帧的TS16时隙传送第2路和第17路信令信号,依次类推,每一子帧内的TS16时隙只能传送2路信令信号码,这样30路的信令信号传送一遍需要15个子帧的TS16时隙,每个话路信令信号码的重复周期为1个复帧周期。

综上所述并结合抽样理论,每帧频率应为8000f/s,帧周期为125μs,所以PCM30/32路系统基群信号总数码率为:2 同步数字复接技术原理2.1 数字复接系统简介数字复接系统包括发送端和接收端两部分,通常称为复接器(Digital Multiplexer)和分接器(Digital Demultiplexer)。

数字复接器由定时单元和复接单元所组成,是把2个或多个低速的支路数字信号按照时分复用方式合并成为一路高速的数字信号的设备;数字分接器是由同步、定时和分接单元所组成,是把合路数字信号分解还原为原来的支路数字信号的设备。

定时单元给设备提供统一的基准时间信号;同步单元可以从接收到的复用信码中提取与发送单元相位一致的同步时钟信号以及帧同步信号,从而真正实现数字复接系统的同步特性。

在实际信号传输中,发送端把低速数字信号合并为高速信号的同时,常插入巴克码用作帧同步码,以便于解复用识别定位;在接收端,帧同步码能否被准确识别直接决定了能否正确地分接还原出各个支路信号。

系统总体结构简图如图1所示。

2.2 时分复接中的同步技术数字通信中的同步技术,也称为定时,包括位同步(也称时钟同步)和帧同步,这是数字通信系统的一个重要特征。

位同步是最基本的同步,是实现帧同步的前提,位同步的基本含义是收、发两端的时钟频率必须同频、同相,这样接收端才能正确接收和判决发送端送来的每一个码元。

为了达到收、发端频率同频、同相,在设计传输码型时,一般要考虑传输的码型中应含有发送端的时钟频率成分。

这样,接收端从接收到的经过复用的码元信号中提取出发端时钟频率来进而得到同频、同相的收端时钟,就可以做到位同步;帧同步是为了保证收、发对应的话路在时间上保持一致,这样接收端就能正确接收发送端送来的每一个话路信号,当然这必须是在位同步的前提下实现。

为了建立收、发系统的帧同步,需要在每一帧(或几帧)中的固定位置插入具有特定码型的帧同步码。

这样,只要收端能正确识别出这些帧同步码,就能正确辨别出每一帧的首尾,从而能正确区分出发端送来的各路信号。

上面介绍的PCM30/32路基群信号的TSO时隙传输的帧同步信号就是为了实现该功能。

2.3 复用方法数字复接的方法主要有按位复接和按字复接、按帧复接三种。

对PCM基群信号来说,一个码字由8位码组成,代表一个样值,所以该系统采用按字复接的方法。

每个复接支路依次轮流插入8位码组成的码字。

复接以后的合路信号码流顺序为:第1路的TS0,第2路的TS0,第3路的TS0,第4路的TS0;然后再是第1路的TS1,第2路的TS1,后面依次类推循环进行。

这种方式完整保留了码字的结构,有利于多路合成处理和交换。

按字复接方法要求设备有较大的存储容量,至少能存储一个码字。

相对比而言,按位复接就是指每次只复接每个支路的一位码字,复接后的码序列中第1时隙中的第1位表示第1支路第1位码,第2位表示第2支路第1位码,后面依次类推。

各路的第1位码依次取过以后,再循环此后的各位码,这种方法的特点是复接时每支路依次复接1 b,对设备要求简单,但破坏了原来的样值码字结构;同理而言,按帧复接是指每次复接一个支路的一帧数码,复接后的码元序列相当于把按字复接中的某一时隙替换为某一个帧信号。

这种复接方法的特点是:每次复接一个支路的一帧信号,因此按帧复接时不破坏原来各帧的结构,有利于信息交换,但要求有很大容量的缓冲存储器,电路结构相对复杂。

如图2所示为按位复接和按字复接的原理示意图。

3 基于FPGA的同步数字复接系统设计与实现根据系统实现功能要求的特征,本文以Verilog HDL硬件描述语言为基础对电路进行功能描述,建立FPGA模型,利用综合仿真设计工具QuartusⅡ8.0对复用端和分解端分别进行系统功能仿真、综合布局布线,并结合仿真波形结果,分析说明系统功能实现的正确性。

3.1 复用端电路设计原理复用端主要由定时时钟输入、时钟分频和复接模块组成,电路原理框图如图3所示。

定义一路8MHz的定时时钟输入信号CLK8和4路2048Kb/s的PCM基群信号a,b,c,d为支路输入。

定时时钟通过分频产生一路2MHz的模块内部时钟信号,并由模块内部逻辑产生一路LD控制信号。

复接器主要完成功能为在2 MB时钟控制下,接受支路输入的基群码元信号,每接收到8个码元信号后将其分别锁存在4个支路锁存器re-ga,regb,regc和regd中,然后在LD控制下将其搬移到32位并入串出移位寄存器,同时在8MHz时钟信号控制下串行输入经过复用的8196Kb高速信号e,其中LD信号的周期被设计为PCM信号的一个时隙间隔,系统利用时钟的同步性可实现4路低速支路输入和一路高速串行输出,电路原理结构图如图3所示。

3.2 复用端功能仿真结果分析利用QuartusⅡ进行综合仿真后,加载波形进行功能仿真分析。

由于一帧信号码元信息太多,为了便于分析,对仿真结果截取了一个LD周期,也即一个时隙的码元信号复用情况。

CLK2时钟上升沿采集支路某一时隙码元信号并存入锁存器,为方便表示,利用十六进制数据表示信号某时刻状态值,如图4所示。

LD上升沿到来时刻,支路寄存器采集到的一个时隙码元信号情况值为:rega=10010010B(92H);regb=11010101B(D5H);regc=11000110B(C6H);regd=11010100B(D4H)。

经过时分同步复用后的高速输出信号为:e=10010010110101011100011011010100B(92D5C6D4H),信道传输速率提高了4倍。

码元信号复用过程及仿真波形示意如图4所示。

3.3 分解端电路设计原理在分解端,8MHz高速串行信号e首先经过同步时钟提取模块,根据串行数据的内部特点,利用数字锁相环等技术提取出和发送端同频、同相的时钟信号CLK8,然后经过帧同步检测模块,建立状态机对串行数据中的TS0时隙的帧同步码元进行检测;这样保证了接收端能够准确无误的恢复发送端的数据。

对于高速数据分解为4路支路信号的电路原理刚好和复用端相反,如图5所示。

3.4 分解端功能仿真结果分析与复接端相反,利用CLKS高频时钟读取串行e的码元信号到锁存器rege中,LD信号为内部逻辑产生的控制信号,负责码元分解搬移。

由于一帧信号容量过大,故截取了某帧内的一个时隙以便于观察分解还原功能的实现,在32个CLK8时钟周期内从串行输入数据e采集到的码元信号锁存在rege移位寄存器中,如图6所示,rege=11100111001110011100111001110011B(E739CE73H),从波形图上可见分解后的支路锁存实时状态值为:rega=111001 11B(E7H);regb=OO11l001B(39H);regc=11001110B(CEH);regd=01110011B(73H),而恢复出4个支路的时隙码元信号为:a:11100111;b:00111001;c:11001110;d:01110011。

分解过程及其信号分解还原波形如图6所示。

4 结语本文主要依据PCM30/32基群信号的特点,结合FPGA建模仿真,利用QuartusⅡ8.0仿真综合软件,实现4路低速信号的同步时分复用,提高信号传输效率;并在分解端将其分解还原为4路原始信号。