[图像传输]基于TMS320C6201DSP的视频图像语音传输系统的硬件设计

(VR虚拟现实)基于ARMDSP的视频监控系统

基于ARM+DSP的智能视频监控系统设计说明1概述视频监控系统是安全防范系统的组成部分,它是一种防范能力较强的综合系统。

视频监控以其直观、方便、信息内容丰富而广泛应用于许多场合。

近年来,随着计算机、网络以及图像处理、传输技术的飞速发展,视频监控制技术也有长足的发展。

同时,随着智能技术特别是模式识别技术在理论和实践上的逐渐成熟,将机器智能概念引入常规视频监控系统成为该领域的重要突破点。

本智能视频监控系统采用基于ARM7TDM I内核的STR710微处理器为主控芯片,同时以TI TMS320C6211为图像处理的协处理器,充分发挥了ARM的控制优势和DSP的信号处理优势。

2硬件需求分析2.1硬件开发目标本系统的设计目标是实现建筑物内的实时监控功能,并通过GPRS模块向管理人员发送报警信号,甚至可以传送现场图片,以提高警报的可靠性。

2.2基本配置(1)USB接口的摄像头(2)STR710X MCU(3)TMS320C6211(4)1M FLASH 存储器(5)2片1M SRAM存储器3硬件系统总体设计3.1总体结构图及功能划分整个系统有四部分组成:全局控制模块、信号采集模块、信号处理模块和远程通信模块。

首先由ARM信号控制摄像头采集现场图像,将数据传入信号处理模块;信号处理模块判断现场是否满足报警条件,若不满足,则更新存储器,否则触发ARM中断,从而激活远程通信模块,由远程通信模块负责与管理人员的交互。

总体结构图如图1所示。

图1 总体结构图3.2组成系统各功能模块的逻辑框图(6)全局控制模块:该部分由STR710X MCU实现,负责系统整体行为的协调,主要管理下列三个模块。

(1)信号采集模块:该模块由USB接口的摄像头实现,负责现场图像的采集。

(2)信号处理模块:该模块负责现场图像的处理,包括现场状态的判别和FLASH存储器的更新。

(3)远程通信模块:负责报警信号的传输、管理信号的接受等。

4硬件系统详细设计4.1存储器空间分配ARM和DSP分别使用1M SRAM和1M FLASH,其中FLASH为ARM和DSP的共享存储器,作为二者的数据交换区和程序存储区。

TMS320C6201 DMA在视频图像编码中的应用

TMS320C6201 DMA在视频图像编码中的应用

李朝晖

【期刊名称】《北华航天工业学院学报》

【年(卷),期】2003(013)003

【摘要】TMS320C6201是一种片内集成了DMA控制器的高性能数字信号处理器(DSP).本文介绍了C6201DMA在笔者设计的视频图像编码器中的应用;针对DMA的应用难点,文中给出了C6201 DMA的编程方法和应用程序实例.

【总页数】4页(P12-15)

【作者】李朝晖

【作者单位】华北航天工业学院,电子工程系,河北,廊坊,065000

【正文语种】中文

【中图分类】TN911.7

【相关文献】

1.视频图像编码中的重排DCT方法 [J], 张贻雄;陈凌宇;王维东

2.真正三维小波变换技术及在视频图像编码中的应用 [J], 罗一平

3.TMS320C6201在MPEG-4视频解码器中的应用 [J], 李朝晖;李冬梅;何佩琨

4.TMS320C6201在MPEG—4视频解码器中的应用 [J], 李朝晖;李冬梅;等

5.视频信号压缩编码──第五讲运动估值在序列图像编码中的应用 [J], 张春田因版权原因,仅展示原文概要,查看原文内容请购买。

基于TMS320C6201的数据采集系统设计

一 0一 ∥ ∥ 0 ~一 ~ _ 0 — _

謦瓣一

维普资讯

≯~ 0 ~ 一 一~ 0

AD9 2 j. 采 样 。 2 4 ̄行 由于 要合 成视 频 采 样 时 钟 ,所 以 ,必 须 从 视频 信 号 中分 离 出 同步 信号 ,故 采用 同步 分 离芯片 E 4 8 L 5 3进 行 行 、场 同步 分 离 。为 了 保证 相 应 的 像 素 采样 位 置 设 计 的 灵 活性 , 用 CP 选 LD来 完 成 , 中 ,首先 ,视 频 传 感 器从 环 境 中获

统 的信 号 处 理 任 务 ,并控 制 系统 运

行 状 态 ,它 的 主要 功 能是 对 图像 低

空 目标 的识 别 和 跟 踪 。 系统 的原 理

如 图 1 示。 所

视 频 采 集 单 元 视 频 采 集 系 统 的原 理 图 如 图 2

所示 。

视 频 信 号 经过 电 缆传 输 及 电路

P 26 T 4 F GA产 生 控 制 信 号 和 采 样 时钟 传 F M 7 5 AE C1 4芯 片 。 P 给 ADC。

串 并 转换 等预 处 理 操 作 , 目标 DS P

电源 模 块 主 要 为 DS 提 供 高 稳 对 预 处 理 操 作 后 的 数 据 信 息 进 行 采 P

统 ,本 系 统 采 用 AD9 2 2 4和 T 3 0 6 0 MS 2 C 2 1芯片 ,并 用 CP D 控 制 时序 逻 辑 ,具 有 超 高 数据 采 集率 、大 L 容 量 存储 空 间、灵 活 外 围接 口和 强 大 的信 号 处理 能 力 等优 点 。 关 键 词 :数 据 采 集 ;实 时 ;数 字 信 号处 理

基于DSP硬件的JPEG2000算法设计与实现的开题报告

基于DSP硬件的JPEG2000算法设计与实现的开题

报告

摘要:

目前,数字图像在卫星图像、医学图像和视频传输领域中应用越来

越广泛。

JPEG2000作为一种新型的图像压缩标准,已经获得了广泛的应用。

本文将利用数字信号处理(DSP)硬件平台,设计并实现一种基于JPEG2000算法的图像压缩系统,以达到快速、高效、低功耗等要求。

首先,本文将介绍数字图像压缩的基本概念和相关技术,包括离散

余弦变换(DCT)、离散小波变换(DWT)和JPEG2000压缩标准等。

然后,设计使用TI公司的TMS320C6678 DSP芯片实现JPEG2000算法。

通过对DSP硬件平台的分析与设计,建立从压缩图像数据到压缩码流输

出的完整流程,对JPEG2000算法进行优化改进,提高图像压缩的速度和质量。

最后,通过对实验结果的测试和分析进行性能评价和实用性验证。

本文的主要贡献在于设计和实现一种具有高效性和实用性的压缩系统,该系统能够对图像进行JPEG2000压缩,在DSP硬件平台下实现高速、高质量、低功耗等要求,并且可以满足大部分应用场景的需求。

关键词:DSP;JPEG2000;图像压缩;TMS320C6678;实现。

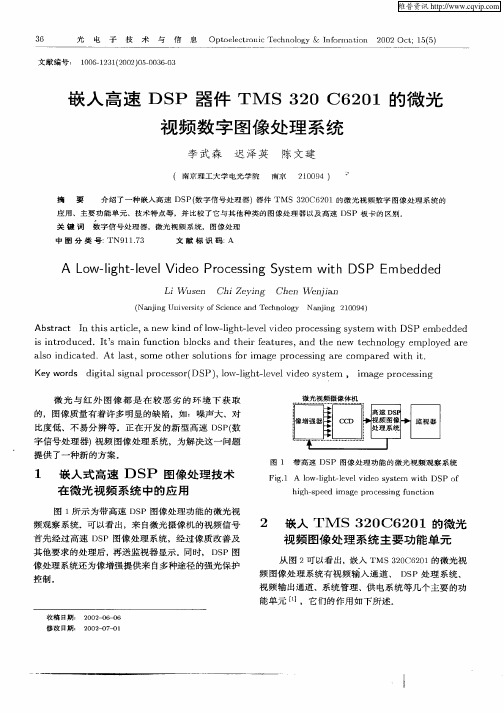

嵌入高速DSP器件TMS320C6201的微光视频数字图像处理系统

( n igUnv ri f ce c n c n lg Nm j g 0 4 Na j iedt o in ea dTeh oo y n y S li 2 0 9 ) n 1 Ab ta t I hi r il . w i d o w—i htl v lv d o p oc s i ys e t S e be e s r c n t sa tc e a ne k n fl o l g —e e i e r e sng s t m wih D P m dd d

i n r duc d.I ’ m ai unc i n b oc s a her f a u e ,a h e t c no o y e si to e tS nf to l k nd t i e t r s nd t e n w e h l g mpl y d a e o e r a s ndiat d.At l s ,s m e o h rs l to o m a e p oc s i g a e c lo i c e a t o t e o u i nsf r i g r e sn r ompa e t t r d wih i .

3 7

21 视 频 输 人通 道 .

将 待 处 理 的 标 准 模 拟 视 频 信 号 转 换 为 数 字 信

号 ,并 把 这 些 数 据 送 入 缓 冲存 储 器 中 ,再 定 时 送 入 TMS3 0 2 1 行 处理 。 功能 单元 的特 点是 : () 2 C6 0 进 该 1

嵌 入 高速 DS 器 TM S 3 0 C6 0 P 2 2 1的微 光

视 频 数 字 图 像 处 理 系 统

李武森 迟 泽 英 陈 文建

(南京理工大学电光学院 南京 2 0 9 1 04)

基于DSP-TMS320C6713控制系统的最小系统板的设计

基于DSP-TMS320C6713控制系统的最小系统板的设计作者:宋玥高伟强阎秋生来源:《现代电子技术》2008年第08期摘要:TMS320C6713是由TI公司生产的高精度浮点型DSP芯片。

基于DSP6713设计的最小系统板对与DSP有关的科研试验以及工程等领域有着重要的应用价值。

主要研究并介绍基于DSPTMS320C6713控制系统的最小系统板的硬件设计,并就最小系统板设计过程中的注意事项做了详尽阐述。

针对电源电路、复位电路、时钟电路、JTAG接口电路、扩展板接口电路和外部存储器扩展电路,提出可行的设计方案,该方案已作为模板电路实现。

关键词:DSP;TMS320C6713;最小系统;硬件设计中图分类号:TP274文献标识码:B文章编号:1004-373X(2008)08-041-(College of Mechanical and Electronic Engineering,Guangdong University ofAbstract:TMS320C6713 is a high precision floating digital signal processor which is produced by TI company.The minimal system that designed based on DSP6713 is very useful and valuable to the area of research and project which respect to DSP.This paper researches and introduces the design of minimal system of control system based on DSPTMS320C6713,and also introduces some problems which need to notice during the design of minimal system.The feasible project of design minimal system hardware circuit will be put forward in the paper.The hardware circuit includes the circuit about power supply,reset,timing,JTAG emulation,extend circuit interface and external memoryKeywords:DSP;TMS320C6713;minimal system;design of hardware1 引言TMS320C6713是TI公司推出的一款TMS320C6000系列的浮点DSP芯片。

基于TMS320C5416DSP芯片的语音录放器的设计

基于TMS320C5416DSP芯片的语音录放器的设计摘要DSP 技术在音频处理领域的应用越来越广。

目前,在很多语音处理系统中都用到了语音录放模块,采集现场的声音并存储起来供以后回放。

语音处理系统的实时性、功耗、体积、以及对语音信号的保真度都是很影响系统性能的关键因素。

因此,语音录放器的设计是非常必要的。

本设计采用的高速TMS320C5416DSP芯片,最高频率能达到160MIPS,能够很好的解决系统的实时性;采用的数字编解码芯片TLV320AIC23(以下简称AIC23)具有16~32位采样精度,录音回放模式下仅23mW的功耗。

因此,该音频编解码芯片与TMS320C5416DSP的结合是可移动数字音频录放系统、现场语音采集系统的理想解决方案。

本文首先介绍了基于TMS320C5416DSP芯片的语音录放系统的工作原理,给出了整体设计方案和工作框图,然后给出了系统的硬件设计方案;然后介绍了基于TMS320C5416DSP芯片的语音录放系统的软件设计。

在整个设计过程中,我们采用了TLV320AIC23DSP芯片为核心音频录放接口器件,结合TMS320C5416DSP芯片,语音数据存储FLASH存储器等进行了硬件设计。

软件部分则采用模块化的设计方法,用汇编语言来实现。

该语音录放器的设计能够完成语音采集,播放,存储,回放,基本实现了语音录放功能。

关键词:TMS320C5416,TLV320AIC23,DSP,语音录放THE DESIGN OF SPEECH RECORDING ANDPLAYING BASED ON TMS320C5416 DSP CHIPABSTRACTThe use of DSP technology in the field of audio processing is increasingly wider. At present, many speech processing systems are used in speech-recording module, acquisition scene speech and stored for later playback. Speech processing System with real-time, power consumption, size, and the speech signal fidelity is a key factor which is affecting system performance. Therefore, speech recording and playing design is very necessary.The design of high-speed chip used TMS320C5416 DSP, the maximum frequency can reach 160 MIPS,which is a good solution to the real-time system; the figures used in the codec chip TLV320AIC23 (hereinafter referred AIC23) is 16 ~ 32 Sampling precision, recording playback mode only 23 mw of power. Therefore, The Audio Decoder Chip and the combination TMS320C5416 DSP Mobile Digital Audio Recording and Playback System Speech Acquisition scene, is the ideal solution.This paper firstly introduces the Speech Recording and Playback System of principle based on TMS320C5416 DSP chip, given the overall design of the plan and diagram, and then gives the system hardware design program; Secondly V oice Recording and Playback System software design based on TMS320C5416 DSP chip .Throughout the design process, we used TLV320AIC23 DSP core chips for audio-recording device interface, TMS320C5416 DSP combination of chips, Speech Data Storage Flash memory, and so on the hardware design. Software is a modular design method, the assembly language to achieve.The speech recording of the design is to complete speech acquisition, broadcast, store, playback, the basic realization of the Speech Recording and Playback function.KEY WORDS:TMS320C5416,TLV320AIC23,DSP,Speech recording and playing目录前言 (1)第1章语音录放器的技术方案及硬件电路设计 (2)§1.1语音录放器的性能指标和硬件方案 (2)§1.1.1 语音录放器的主要性能 (2)§1.1.2 硬件设计方案 (3)§1.2 语音录放系统的硬件电路设计 (4)§1.2.1 TMS320C5416DSP数字信号处理接口电路模块 (5)§1.2.2 TLV320AIC23语音录放接口电路模块 (9)§1.2.3语音数据存储接口电路模块 (12)§1.2.4 音频接口电路模块 (13)§1.2.5 电源接口电路模块 (15)第2章语音录放器的应用软件设计 (17)§2.1 语音录放器应用软件系统的设计方案 (17)§2.2 主程序模块 (17)§2.3 语音录放模块程序设计 (20)§2.3.1 MCBSP的配置 (20)§2.3.2 AIC23的初始化 (22)结论 (26)参考文献 (27)致谢 (28)附录 (29)前言DSP处理速度快,功耗低,性能好,基于TMS320C5416DSP芯片的语音录放器存储容量大,语音录放时间长,具有很好的通信音质等特点,因此被广泛应用于很多领域中。

基于TMS320C6201实时图像处理系统的EMC设计

一

一

r

● ● ● ●go … …

…

认 证 与 电 磁 兼 容 卷

Ce r i i at On & EM C t f C i

EM C s gn a - i e I age y oc s i De i ofRe l t m m r Pr e s ng Sys em t Bas d e on TM S320C620 1

s f a e a t .m m ig m e s ew i m p a i. n ve of h y t m C B m a u a t r n ee t o t r n .a w n a ur t e h h ss i iw e s se P t n f cu e i lc r oma e i gn t c c m p t it u s i . h s p p rb ig o wa d t e m e h d o o o b he d d f m ner r n e a d o a i ly q e t b i on t i a e r s f r r h n t o fh w t e s il e r 0 it f e c n e

Key or w ds: PC B: EM C : EM ; l DSP : TM S3 20C6201

CL hu b ; c m orTN7 2 0

Do cum ontcodeI A

Ar i e ● 1 0 ・ 1 7( 00 ) 6 0 7 ・ 4 t cl D: 0 3 0 0 2 7 0 ・ 0 4 0

系统 要 由六 个 功 能 块 构 成 ,

其 硬 件 功 能 框 图 如 图 1所 示 。 系

公 司 的 新 一 代 高 性 能 定 点 DS P芯 片 , 0 时 钟 的 峰 值 性 能 可 以 2 MHz 0 达 到 24 Mop 0 0 s。 该 系 统 利 用 微 处 理 器 芯 片 对 图 像 进 行 编 码 解 码 处 理 来 实 现 。 这 种 实 时 通 用 图

基于DSP语音信号采集系统的设计毕业设计(论文)

DSP课程论文(设计)题目基于DSP语音信号采集系统的设计院系专业学生姓名学号指导教师二O一四年五月二十八日基于DSP语音信号采集系统的设计摘要:为了研究数字信号处理,提出了一个基于DSP TMS320VC5502的语音信号采集系统的设计。

给出了该系统的总体设计方案,具体硬件电路,包括系统电源设计、复位电路设计、时钟电路设计、存储器设计、A/D接口电路设计、JTAG接口设计、DSP与A/D芯片的连接等,以及软件流程图。

通过MATLAB得到语音信号的波形和频谱图。

实验表明: 所设计的基于DSP的硬件和软件系统是一个很好的语音信号采集系统,该系统结构清晰,电路简洁,易于实现。

关键词:语音信号;数据采集;DSP;TLC320AD501.引言20世纪50年代以来,随着数字信号处理各项技术的发展,语音信号处理技术得到不断提高, 语音合成、语音识别、语音记录与语音控制等技术已开始逐步成熟并得到应用。

在语音信号处理过程中, 要实现语音信号处理技术的精确性、实时性目的,语音信号采集和无误差存储成为语音信号处理中的前提。

TMS320VC5502是德州仪器公司公司在2002年基于TMS320VC5502推出的定点数字信号处理器,它采用修正的哈佛结构,包括1个程序存储总线、3个数据存储总线和4个地址总线,这种结构允许同时执行程序指令和对数据操作,运行速度快,单周期定点指令执行时间为5ns,远高于语音信号采集和处理的要求。

在语音信号采集中, 模拟信号向数字信号转换(ADC)的精度和实时性对后续信号处理过程起到了重要作用。

设计中采用TLC320AD50完成语音信号的A/D转换。

TLC320AD50是TI公司提供的一款16 bit 同步串口A/D和D/A转换芯片,ADC之后有1个抽取滤波器以提高输入信号的信噪比, 其采样频率最高可达22.5 Kb/s,满足语音信号处理中关于采样频率的要求。

2.总体设计基于TMS320VC5502的语音信号采集系统的结构如图2–1所示,该系统的中央处理单元采用美国TI(德州仪器)公司的高性能定点数字信号处理芯片TMS320VC5502,TMS320VC5502是TI 公司推出的定点数字信号处理器,它采用修正的哈佛结构,包括12组独立总线,即1组程序读总线,1组程序地址总线,3组数据读总线,2组数据写总线,5组数据地址总线。

双路视频图像跟踪器硬件设计

双路视频图像跟踪器硬件设计摘要:本文阐述了双路视频图像跟踪器的硬件设计,以fpga和dsp为核心,采用双路dsp交互通讯设计,实现了双路视频同时输入、同时跟踪的硬件平台,有利于跟踪算法和图像融合算法的实现及扩展。

关键词:跟踪器图像采集 dsp fpga引言随着电子技术及图像处理技术的飞速发展,图像跟踪器的研究取得了丰硕的成果,并在武器装备及民用领域得到越来越广泛的应用。

图像跟踪器的主要功能是采集视频图像,通过跟踪运算,计算出场景中被跟踪目标的位置信息。

本图像跟踪器设计实现了双路视频信号的同时输入、同时跟踪、同时输出以及与上位机、传感器、伺服控制组件的通讯功能和输出图像的信息叠加功能。

图像跟踪器硬件总体设计图像跟踪器接收来自可见光摄像机和红外摄像机的标准模拟视频信号,经视频信号采集,将两路模拟视频信号同时转换为数字视频信号,由fpga完成双路数字图像采集及图像预处理,存入相应的存储器。

图像跟踪器电路采用双dsp策略,图像跟踪器接收到上位机跟踪指令后,一片dsp负责可见光视频的跟踪运算,另一片dsp负责红外视频的跟踪运算,计算出被跟踪目标位置,输出目标区偏离视场中心的误差信号到伺服控制组件,驱动伺服机构跟踪目标,最终实现目标实时跟踪。

同时,图像跟踪器将含有系统信息的数字视频图像传输给视频图像输出电路,经视频编码器,转换为模拟信号输出给监视器显示。

图1给出了图像跟踪器的工作原理图。

图像跟踪器模块设计图像跟踪器硬件电路采用了dsp+fpga的设计思路,使用两片ti 公司生产的tms320c64系列高性能dsp和altera公司生产的cyclone系列fpga芯片,实现了单板结构的图像跟踪器设计,满足了双路视频同时跟踪同时输出的设计要求。

图像跟踪器硬件设计主要分为视频信号采集模块、视频信号字符叠加及输出模块、通讯模块、跟踪算法实现模块四大部分。

视频信号采集模块硬件设计视频信号采集模块实现两路全电视视频信号的解码及数字视频信号的采集功能。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

9&2 模 拟 视 频 输 入 接 口 的

原理框图如图 5 所示%

预处理

: 5; 模 拟 视 频 解 码 模 块 %

视频解码模块的作用是将 复 合 视 频 $ <% 分 量 等 模 拟 视频信号进行 ’=9 转换# 提取其中的同步和时钟信 号 #所 有 转 换 电 路 均 集 中 在 一块芯片内% 根据以上要 求 # 选 择 2/>,>?. 公 司 生 产 的可编程的数字视频 ’=9 变 换 器 &’’()))’ # 它 有 @

音频编解码器 !!"#$% " 摄像头

+8+" 输入缓冲

路模拟输入和 5 路模拟信号处理通道# 可以通过编程选 择 信 号 制 式 % 输 出 信 号 可 以 是 <AB@)):)5 位 ; $ <AB@55

:)7 位 ; $ <AB@55:%%80C7D7;:E 位 ; $ 0FG:D $7 和 D;:)7 位 ;

;. $ @@H4 $ @6J0K 等 通 用 的 采 样 频率 ! 如 此 宽 范 围 的 采 样

频率 可 以 适 应 从 电 信 到 音 频 的 各 种 应 用 需 求 # /8@.;49 采 用 频 率 分 别 为 4?H7;@@=0K 和 .@H3:?=0K 的 . 个 晶 振 来作为采样频率的时钟源#

&’’()))’ ’ * # 转换器 #&2 31&456%756)

以太网接口 图) 图像语音传输系统基本结构图

+8+" 帧存储器

或 0FG :E $E 和 E; :5@ 位 ; 格 式 % 系 统 通 过 8 5% 总 线 对

+,-./ 0"1 �’1

&’’()))’ 编 程 # 完 成 初 始 配 置 工 作 % 来 自 摄 像 头 的 模 拟

基于 !"#$%&’(%&) *+, 的视频图像语音传输系统的硬件设计

武 汉 华 中 科 技 大 学 控 制 科 学 与 工 程 系 !"#$$%"&

摘

要 ! 提 出 了 基 于 !"#$%&’(%&) *+, 芯 片 的 视 频 图 像 语 音 传 输 系 统 的 硬 件 方 案 并给出了

硬件实现的总体框图! 关 键 词 ! !-+$%.’(%.)

制 电 路 决 定 , ! 帧 时 序 由 0+12 信 号 控 制 # 在 系 统 中 将 采 用 带 有 - / 接 口 的 $ 与 34 系 列 兼 容 的 单 片 机 567/34-/.

.

/<>1/ 模 块 支 持 线 性 和 话 筒 的 多 路 输 入 " 音 频 的 放

大器用来对话筒输入信号进行预防和滤波’ 线性输入经 过 无 源滤 波 $ 交 流 耦 合 送 入 /8@.;49 ! 输 入 插 座 可 以 用 来 连 接 立 体 声 源 !通 过 软 件 可 以 独 立 控 制 左 $右 输 入 声 道 的 选 择 和 各 自 的 增 益 # /<>1/ 还 包 含 一 个 可 通 过 >8A 软 件 控制衰减的线性输出#

!微型机与应用 "!""# 年第 $ 期

号 ! !"#$ " %& 为 不 同 颜 色 ’()* 和 +)*, 复 用 信 号 # 信 号 输 出 格 式 由 - / 总 线 控 制 ’*!" 信 号 输 出 格 式 由 - / 总 线 控

. .

是 3" 器 件 ! >8A 是 ;H;" 器 件 ! 它们 相 互 连 通 后得 并 行 控 制 信 号 !并 且 必 须 通 过 总 线 收 发 器 进 行 信 号 转 换 #

"

硬件结构

:); 视 频 采 样 要 求 % 模 拟 视 频 输 入 接 口 电 路 的 作 用 是

"#! 模 拟 视 频 输 入 接 口 设 计

对 输 入 的 模 拟 视 频 信 号 进 行 预 处 理 #并 将 其 数 字 化 % 视 频 采 样 有 5 个 重 要 指 标&采 样 分 辨 率 和 采 样 频 率 % 采 样分 辨 率代表图像灰度量化的等级# 位数越多# 图像层次越丰 富 #同 时 图 像 数 据 量 也 越 大 ’采 样 频 率 决 定 可 数 字 化 后 图 像的空间分辨率 #为了不失真 #它 必 须 大 于 模 拟 视 频 信 号 的 频 谱 中 最 高 频 率 的 5 倍 % 另 外 #还 要 求 模 拟 视 频 输 入 接 口所引入的系统噪声最小%

简化了系统设计 # 2-2<’->5:.";?@%, 用于向 5=8;.%/?.%4 传 输 经 899:4449 转 换 后 的 4? 位 实 时 图 像 数 据 "A<’% "

’.& 采 用 8>+9= 扩 充 系 统 外 部 数 据 动 态 存 储 单 元 #

在 高 速 >8A 视 频 处 理 系 统 中 ! 数 据 存 储 器 的 作 用 是 暂 存 图 像 数 据 # 而 高 速 >8A 器 件 5=8;.I/?.I4 的 片 上 数 据

43, # 2-2< 不 存 在 地 址 线 的 问 题 ! 所 以 不 用 连 接 地 址 线 # !"! 音 频 编 解 码 器 的 选 取

采 用 /BCDEFG 公 司 的 /8@.;49 芯 片 作 为 核 心 音 频 编 码 解 码 器 #/<>1/& 模 块 # /8@.;49 多 媒 体 芯 片 为 系 统 提 供 一 个 灵 活 $ 通 用 的 音 频 前 端 # 它 是 一 个 4? 位 立 体 声 器 件 !包含完整的片上滤波$模拟 混 音 和 可 编 程 控 制 的 增 益 和 衰 减 调 节 # /8@.;49 支 持 6 $ 7H? $ 44HI.3 $ 4? $ ..HI3 $

’或 繁 杂 的 页 面 切 换,是 不 可 忽 视 的 实 际 问 题 # 从 对 采 集 到

的 数 据 的 处 理 方 式 可 以 看 出 ! 对 于 单 纯 采 集 应 用 %不 需 要 对数据做诸如叠加等预处理工作 &! 其 系 统 缓 存 单 元 在 结 构 上 相 当 于 先 进 先 出 ’2-2<, 队 列 ! 即 按 信 号 时 间 顺 序 先 采 集 的数据先被主处理芯片读取及处理# 所以采用专门的

!"# 系 统 扩 展 存 储 器 接 口 设 计 #4& 程 序 存 储 及 数 据 预 置 # 由 于 对 不 同 的 成 像 条 件 ! 要

求 其 视 频 运 动 估 算 和 图 像 处 理 算 法 能 够 自 动 适 应 ! 所以 必须存储多种算法备选# 因此要求选用大容量的存储器 或 者 多 片 小 容 量 的 存 储 器 # 片 外 6 位 或 4? 位 的 程 序 存 储 器 必 须 配 置 在 5=8;.I/?.I41=-2 # 外 存 接 口 & 的 /14 空 间 # 这 是 因 为 " ! 系 统 复 位 后 只 能 从 /14 载 入 引 导 程 序 #

31&456%756) 9&2 处理

图 5 9&2 模 拟 视 频输入接口的原理框图

!

系统的组成和基本原理

一个完整的视频图像语音传输系统不但要具备对图

&’’()))’

时 钟 产 生 电 路

像语音信号的采集功能# 还要求完成对采集上来的图像 语 音 信 号 的 分 析 及 处 理 算 法:如 图 像 压 缩 等;#最 后 采 用 一 定的媒质将处理好的信号传输到终端主机显示% 视频图 像语音信号的分析及处理算法的运算量很大# 同时又要 满 足 实 时 显 示 的 要 求 # 因 此 采 用 了 高 速 9&2 芯 片 作 为 数 据核心的处理单元% 系统的基本结构模型如图 ) 所示%

/8@.;49 同 时 提 供 了 并 行 和 串 行 接 口 ! 支 持 >=9 及

中 断 工 作 接 # 这里采用的是其中最有效的方式" 即串行接口传输音频 数 据 ! 并 行 接 口 传 输 控 制 信 息 # /8@.;49 使 用 与 >8A 的

对 899:4449 进 行 控 制 ! 即 对 模 拟 视 频 前 端 899:4449 的采样率$箝位电平$锁相环 等 进 行 编 程 设 置!以 使 整 个 视频输入接口电路按照预先设计的方式工作#

’;, 采 用 2-2< 作 为 实 时 图 像 数 据 输 入 缓 冲 器 # 从 性 能

上来说! 普通型的帧存储体在采集的同时不能读取采集 数 据 # 虽 然 采 用 双 端 口 +9= 也 可 以 解 决 并 发 访 问 的 问 题 ! 但它所必需的地址译码和占用大段的主存储器映射空间

软同步处理

信 号 #首 先 在 模 拟 信 号 控 制 下 #进 行 信 号 箝 位 $模 拟 放 大 $ 反 混 淆 滤 波 $’ = 9 转 换 # 然 后 将 得 到 的 E 位 亮 度 信 号 和 E 位色度信号分别送往亮度处理电路和色度处理电路进行 处 理 # 产 生 )7 位 的 <AB 信 号 % <:( & 6; 为 E 位 数 字 亮 度 信 ( !" (

" 1=-2 的 @ 个 存 储 空 间 中 ! 只 有 /14 可 以 与 6 位 或 4?

位 的 (窄 存 储 空 间 )接 口 # 根 据 预 存 程 序 和 数 据 的 大 小 估 计 ! 采 用 相 应 容 量 的 2GFDN +<= #