GF2m上的一种可并行快速乘法器结构

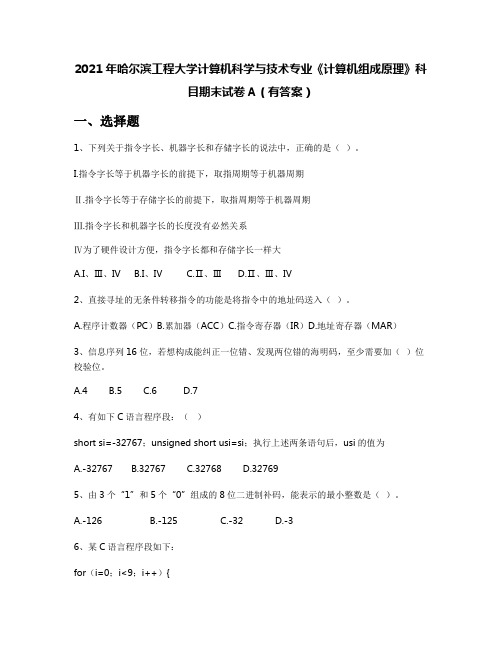

2021年哈尔滨工程大学计算机科学与技术专业《计算机组成原理》科目期末试卷A(有答案)

2021年哈尔滨工程大学计算机科学与技术专业《计算机组成原理》科目期末试卷A(有答案)一、选择题1、下列关于指令字长、机器字长和存储字长的说法中,正确的是()。

I.指令字长等于机器字长的前提下,取指周期等于机器周期Ⅱ.指令字长等于存储字长的前提下,取指周期等于机器周期Ⅲ.指令字长和机器字长的长度没有必然关系Ⅳ为了硬件设计方便,指令字长都和存储字长一样大A.I、Ⅲ、IVB.I、ⅣC.Ⅱ、ⅢD.Ⅱ、Ⅲ、Ⅳ2、直接寻址的无条件转移指令的功能是将指令中的地址码送入()。

A.程序计数器(PC)B.累加器(ACC)C.指令寄存器(IR)D.地址寄存器(MAR)3、信息序列16位,若想构成能纠正一位错、发现两位错的海明码,至少需要加()位校验位。

A.4B.5C.6D.74、有如下C语言程序段:()short si=-32767;unsigned short usi=si;执行上述两条语句后,usi的值为A.-32767B.32767C.32768D.327695、由3个“1”和5个“0”组成的8位二进制补码,能表示的最小整数是()。

A.-126B.-125C.-32D.-36、某C语言程序段如下:for(i=0;i<9;i++){temp=1;for(j=0;j<=i;j++)temp+=a[J];sum+=temp;}下列关于数组a的访问局部性的描述中,正确的是()。

A.时间局部性和空间局部性皆有B.无时间局部性,有空间局部性C.有时间局部性,无空间局部性D.时间局部性和空间局部性皆无7、连续两次启动同一存储器所需的最小时间间隔称为()。

A.存储周期B.存取时间C.存储时间D.访问周期8、CPU中不包括()。

A.操作码译码器B.指令寄存器C.地址译码器D通用寄存器9、CPU中的译码器要用()。

A.地址译码人B.指令译码C.数据译码1D.控制信号译码10、总线宽度与下列()有关。

A.控制线根数B.数据线根数C.地址线根数D.以上都不对11、在()结构中,外部设备可以和主存储器单元统一编址。

模拟乘法器原理

模拟乘法器原理乘法器是一种电路设计,用于将两个输入数相乘,并输出它们的乘积。

乘法器常用于数字信号处理、计算机和通信系统中。

乘法器的原理基于布尔代数和逻辑门。

它通常由多个逻辑门和触发器组成,以实现乘法运算。

乘法器的设计要考虑精度和运算速度。

一种常见的乘法器设计是Booth乘法器,它使用偏置编码技术来减少部分乘积的计算。

另一种常见的设计是Wallace树乘法器,它通过级联多个片段乘法器来提高速度。

乘法器的操作原理是分别将两个输入数的每个位进行乘法运算,并将结果相加。

具体步骤如下:1. 将两个输入数分别展开为二进制形式,对应位分别相乘。

最低位乘积直接输入到第一级部分乘积的输入。

2. 对每一位乘积进行部分乘积运算。

部分乘积运算是将当前位乘积和之前的部分乘积相加,并将结果输出到下一级。

3. 重复步骤2,直到所有位的乘积都被计算出来。

4. 对所有部分乘积进行累加,得到最终的乘积结果。

乘法器还需要考虑进位和溢出的问题。

在每一位相乘时,会产生进位位和当前位的乘积。

如果乘积超过了位数的范围,就会产生溢出。

乘法器的性能可以通过速度和面积这两个指标来评估。

速度是指乘法器完成一次乘法运算所需的时间,面积是指乘法器所占据的芯片空间大小。

总结来说,乘法器是一种常见的电路设计,用于将两个输入数相乘。

乘法器的原理基于布尔代数和逻辑门,它的设计考虑了精度和运算速度。

乘法器的操作原理是对输入数的每一位进行乘法运算,并将结果累加得到最终的乘积。

乘法器还需要考虑进位和溢出的问题。

乘法器的性能可以通过速度和面积来评估。

一种基于LPM的快速乘法器的设计

一种基于LPM调用的快速乘法器的设计摘要:乘法器是数字系统中的常见电路模块,本文设计了一种采用EDA技术、基于FPGA 芯片、调用LPM模块实现一种快速乘法器的方案。

调用LPM模块可以化简数字系统的设计,方法是根据系统的功能需求调用适当的LPM模块,根据系统功能对其各项参数进行设置,再配备适当的设计文件即可。

关键词:乘法器;LPM调用;EDA;MIF文件0 引言乘法器是通信系统中的重要模块,常用于卷积、傅里叶变换、滤波、变频等计算过程。

采用FPGA实现乘法器的算法有很多,如移位相加、加法器树乘等算法,而基于FPGA快速RAM资源实现的乘法器,具有更高的速度,在信号处理系统中,具有快速响应的优势。

在EDA设计中,集成开发环境自带丰富的参数可设置模块库(LPM),设计者可根据系统功能的需要,在LPM中调用适当的模块,编写相应的参数,配备相应的设计文件,即可实现设计。

LPM模块通常都是各项指标优化的优秀成熟设计半成品,可以减轻设计者的调试工作,对于较复杂的数字系统LPM调用法可以简化设计过程,提高了设计者的开发效率。

本文讨论了一种基于FPGA芯片通过LPM模块调用实现4位快速乘法器的方法。

1 快速乘法器的LPM的调用方案与实现在集成开发环境maxplus2下,LPM调用有原理图调用和VHDL调用两种方法,本文采用第一种方法。

在maxplus2原理图编辑器下,从参数可设置模块库…\maxplus2\max2lib\mega_lpm\*中调用LPM_ROM模块,设置其输入为两个4位的二进制乘数,将这两个4位二进制数组合为ROM的地址,在相应的地址单元里存放其乘积值。

因此该模块具有两个输入端口,分别为时钟信号CLK、地址输入端INPUT[7..0],乘法结果输出端OUTPUT[7..0]。

在原理图编辑器下双击LPM_ROM右上角的参数显示区域,弹出Edit Ports/Parameters 设置对话框,设置LPM_ROM模块相应的参数。

一种可重构的快速有限域乘法结构

第 2 卷第 4 8 期 2 0 年 4月 06

电

子

与信息来自学报 V 1 8 . b . No 4 2 Ap . 0 6 r2 0

J u n l fE e to is& I f r t nT c n l g o r a lc r n c o n o ma i e h o o y o

chenguafeng一类有限域的高效部分并行乘法器期刊论文计算机工程与应用20094519一种基于有限域的快速乘法器的设计与实现期刊论文计算机研究与发展2004414引证文献2条gf2m上的一种可并行快速乘法器结构期刊论文计算机工程与应用200935分组密码算法矩阵乘法运算的设计原理期刊论文吉林大学学报理学版20122引用本文格式

Ke r s VL I F n t ed Mu t l r Re o f u a l, l t u v r p o y t ms y wo d S , ii f l, ei l p i , c n i r be Elp i c r ec y t s se i e g i c

1 引言

有限域在纠错码 、高速数字通信 、密码学等领 域有着广

它具有高度的灵活性 ,同时能将速度 提高一倍 。与文献【】 9

中的乘法器相 比,它有较低的硬件复杂度。 基 { aa , a ) l , …, ‘被称 之为多项式基 , , 其中 a是不可 约

泛 的应用 。在 R A密码和椭 圆 曲线 密码I 等算法设计 中, S 有 限域乘法是最频繁、最复杂的运算。因此,优化 乘法器结

( p Eet n n ier g S a g a io n nv S a g a 0 0 0 C ia De tf l r i E gnei , h n h i a t gU i. h n h i 0 3 , hn ) o co c n J o , 2

基于MPI的卷积计算并行实现

基于MPI的卷积计算并行实现鲁金;马可;高剑【摘要】针对传统的卷积并行计算模型中,存在着大量的消息传递,负载不均衡等问题;提出一种新的基于MPI同步模型的并行卷积算法;该模型采用消息传递的方式进行进程间的通信,同时有效平衡负载,避免大量的消息传递;通过分析该模型的加速比和效率,实验结果表明,此方法显著提高了并行效率和长序列的运算速度,充分发挥了节点间分布式存储和多核并行处理的优势,是一种有效可行的并行策略.【期刊名称】《计算机测量与控制》【年(卷),期】2016(024)001【总页数】3页(P292-294)【关键词】卷积计算;并行;消息传递接口;负载平衡【作者】鲁金;马可;高剑【作者单位】西安电子工程研究所,西安710100;西安电子工程研究所,西安710100;西安电子工程研究所,西安710100【正文语种】中文【中图分类】TP311近年来,受到程工艺的限制,单核处理器的性能已接近极限,通过提高单处理器的时钟频率来提高计算机性能的方法越来越难以达到良好的效果。

因此,多核技术成为CPU制造商显著提高处理器的性能的共同解决方案[1-2]。

多核设备为应用程序提供了并行计算的硬件平台,使计算机的计算速度得到了巨大提高。

而另一方面,在数字信号处理领域中,要处理的数据量越来越庞大,实时性的要求也越来越高,,将并行处理的思想运用在信号处理中,构建一个具有并行性的系统,必将是一个未来发展的趋势。

卷积计算作为信号与系统时域分析的一种重要方法。

在科学计算领域中起着重要的作用[3],广泛应用于通信,航空航天,生物医学工程,雷达信号处理等工程领域。

因此,将并行化的思想应用在卷积计算中,从而大大加快卷积计算的速度,提高卷积计算的效率,具有重要的研究意义。

并行计算是指在并行系统上,将一个大的任务分解为多个小的子任务,分配给不同计算单元上,各个计算单元之间相互协同,并行地执行各个子任务,最后汇合同步,从而达到加速求解任务的目的。

计算机动态仿真(选修课试题)

1简述机构的特征,画出二例常见机构示意图机构是机器的重要组成部分,其主要功能是实现运动和动力的传递和变换。

因此,机构也具有机器的前两个特性,即∙是一种通过加工制造而成的机件组合体。

∙机器中各个机件之间都具有确定的相对运动。

4-74是曲柄滑块机构这一个里面随便挑一个就行,下面有名称的2是说明黄金分割法在优化计算机中的应用原理黄金分割法是用于一元函数f(x)在确定的初始区间[a,b]内搜索极小点a*的一种方法。

它是优化计算中的经典算法,以算法简单、效果明显而著称,是许多优化算法的基础。

但它只适用于一维区间上的凸函数。

其基本思想是:依照“去坏留好”原则、对称原则、以及等比收缩原则来逐步缩小搜索范围。

具体地说,就是在区间[a,b]中取点,,如果令;如果令,重新开始。

这样每次可将搜索区间缩小倍或倍,直至缩为一点。

黄金分割法原理如图1所示,其中K=0.618,区间长度为L。

该算法为收敛速度很快的一维搜索方法。

3简述有限元法在机械工程的应用原理将连续的求解域离散为一组单元的组合体,用在每个单元内假设的近似函数来分片的表示求解域上待求的未知场函数,近似函数通常由未知场函数及其导数在单元各节点的数值插值函数来表达。

从而使一个连续的无限自由度问题变成离散的有限自由度问题。

应用平面问题:空间问题和壳版问题静力平衡:动力响应和结构稳定国体力学:流体力学,传热学,电磁学等弹性材料:弹塑性,塑性,粘弹性,粘塑性和复合材料等三维问题1应力与平衡方程2应变与几何方程3物理问题4边界问题二维问题平面应力与应变问题都是我自己在网上找的,不知道和你们学的一样不,仅供参考哈!。

GF(2 m)域上通用可配置乘法器的设计与实现

b s n p ln milb s . lpirpo oe n ti p p r c n st f iee t sc rt e n fECC ae o oy o a aeA mut l rp s d i hs a e a ai y df rn e u y d ma d o i e s f i .

Ke o d :g l sf l ; F 2 ) m lpi y w r s a i i d G ( ; ut l r o e i e

摘 要 : 出 了一 种 应 用 于 椭 圆 曲 线 密 码 体 制 中的 有 限 域 乘 法 器结 构 , 于 已有 的 dg — e a 结 构 乘 法 器 , 用局 部 并 行 的 bt 提 基 itsr l i i 利 i — prl l 构 . 效 地 省 去 了模 约 简 电路 , 得 乘 法 器适 用 于 任 意 不 可约 多项 式 ; 过 使 用数 据 接 口控 制 输 入 数 据 的 格 式 并 内嵌 大 aal 结 e 有 使 通 尺 寸乘 法器 。 以 配置 有 限城 乘 法 器 的结 构 , 以 实现 基 于 多 项 式基 的 有 限域 乘 法运 算 。 该 结 构 可 以 有 效 满足 椭 圆 曲 线 密 码 体 制 可 用

维普资讯

C m ue nier ga dA pi t n o p trE gnei n p l ai s计 算 机 工 程 与应 用 n ห้องสมุดไป่ตู้ o

20 ,3 1 ) 0 7 4 (2

9 1

G 2 ) 上通用可 配置乘 法器 的设计 与实现 F(m域

卫 学陶 。 紫彬 . 戴 陈 韬

W EI Xu — a , e t o DAI Z — i CHEN T o i b n, a

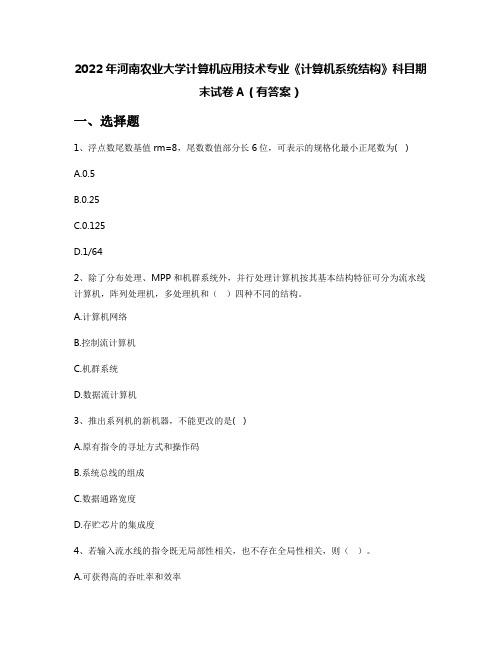

2022年河南农业大学计算机应用技术专业《计算机系统结构》科目期末试卷A(有答案)

2022年河南农业大学计算机应用技术专业《计算机系统结构》科目期末试卷A(有答案)一、选择题1、浮点数尾数基值rm=8,尾数数值部分长6位,可表示的规格化最小正尾数为( )A.0.5B.0.25C.0.125D.1/642、除了分布处理、MPP和机群系统外,并行处理计算机按其基本结构特征可分为流水线计算机,阵列处理机,多处理机和()四种不同的结构。

A.计算机网络B.控制流计算机C.机群系统D.数据流计算机3、推出系列机的新机器,不能更改的是( )A.原有指令的寻址方式和操作码B.系统总线的组成C.数据通路宽度D.存贮芯片的集成度4、若输入流水线的指令既无局部性相关,也不存在全局性相关,则()。

A.可获得高的吞吐率和效率B.流水线的效率和吞吐率恶化C.出现瓶颈D.可靠性提高5、全相联地址映象是指()。

A.任何虚页都可装入主存中任何实页的位置B.一个虚页只装进固定的主存实页位置C.组之间是固定的,而组内任何虚页可以装入任何实页位置D.组间可任意装入,组内是固定装入6、指令间“一次重叠”说法有错的是( )A.仅“执行k”与“分析k+1”重叠B."分析k”完成后立即开始“执行k”C.应尽量使“分析k+1”与“执行k”时间相等D.只需要一套指令分析部件和执行部件7、IBM360/91属于()A.向量流水机B.标量流水机C.阵列流水机D.并行流水机8、计算机组成设计不考虑( )。

A.专用部件设置B.功能部件的集成度C.控制机构的组成D.缓冲技术9、IBM360/91对指令中断的处理方法是()A.不精确断点法B.精确断点法C.指令复执法D.对流水线重新调度10、下列说法中不正确的是( )A.软件设计费用比软件重复生产费用高B.硬件功能只需实现一次,而软件功能可能要多次重复实现C.硬件的生产费用比软件的生产费用高D.硬件的设计费用比软件的设计费用低二、判断题11、能做为评价其它置换算法标准的置换算法是RAND。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

茗“+r(茹)

输出:c≈·b

1.c+_旬

2.对于i从m一1降序到0,重复执行 2.1 c+_左移(c)+c“·r

2.2 c+--c+bi"a

3.返回c 算法1所示的高位优先乘法器可扩展为大小可变的域

GF(2“)上的乘法器,其中m E{m1,ma,…,嘲,mI≤观≤…mt

hardware complexity.

Key words:Very large Scale Integrated Circuits(VLSl);multiplier;reconfignrable;elliptic calve cryptogaphy

攮要:在可重构的高位优先串行乘法器基础上,提出了一种GF(2_)上可控制的快速乘法器结构。该乘法器增加了1个控帝l信号 和7个两路选择器。在域宽小于最大域宽的一半时能利用现有硬件资源并行计算两个乘法。该乘法器结构电路复杂度低,能利用现 有存储空间并行计算,并能扩展应用于串并混合结构中。这种乘法器适合存储空间小、低硬件复杂度的可重构密码系统VLSI设计。 关键词:超大攫膜集成电路(VLSI);乘法器;可重构;椭圆曲线密码 DOI:10.37780.issn.1002—8331.2009.35.019文章编q-:1002—8331(2009)35-0059-03文献标识码:A中图分类号:7Ⅲ918;TN47

马自堂,段斌,刘云飞:GF(2“)上的一种可并行快速乘法器结构

2009,45(35)

61

馈后的位由于都经过同样的延迟,所以能严格同步输出。

4改进方法在串并混合模式中的应用 由于MSB在m个时钟周期内完成一次乘法运算,当m较

大时采用MSB乘法器实现速度还是较慢,因此可以根据芯片 的资’源J隋况采用串并混合结构的乘法器。这种算法能通过对并 行计算的位数—数字大小(digit--size)k的选取在速度与面积之间 进行平衡。若数字大小为||},则完成—次模乘运算只需I(m+l溉] 个时钟周期。记,=Fm/kl,且

算法3 G“2_)上的串并混合乘法嬲

输入:仁(铂,…,ol,ao),b=(6。,…,6l,bo)EGF(2")√<并),J|}

输出:c=口·b 1.c(菇)+—口(茗)—艮1(x)modl人并) 2.对于i从s一2降序到0,重复执行

2.1 u(菇)o∑c,茗J蒯“善)

j=0 k-1

2.2口(菇)~(屉)∑6。。√Inod人茗)

hi,bo),芦(kl,…,r^,kl,…,rl ro)∈cF(2m) “茗)为域的不可约多项式,n=m]2,sel∈【0,11为控制信号 输出:c=(c+1,…,c。,c一,…,cl'co)邵·b

1.c+_由

2.如果sel=l

2.1令(k1,…l"1 ro)=(~l,…r肿l,k)--A髫)纠 2.2对于i从n_l降序到0,重复执行

积复杂度极限情况下为常数和O(m‘)。混合乘法器通常用来在 硬件资源受限时均衡性能和面积。例如,串行乘法器中的高位 优先乘法器(MSB)能用2个m比特移位寄存器和2个寄存器

在进行m次移位后完成一次C以2“)上的乘法运算。而当硬件 资源允许时,并行乘法器可以用组合电路将乘法运算的m位乘 积一次并计算出来,但这是以更多的电路复杂度为代价的。混合 乘法器如数字串行乘法器能一次同时计算出乘积的多位。如果 乘法运算以k倍的速度加速完成,但电路复杂度也会增加_|}倍。

ture has low circuit complexity and low power cost.It Can USe limited registers to accelerate computing,and also can be applied

to the serial-parallel architecture.It suits the VLSI design of reconfignrable cryptographie applications with limited storage and low

收稿日期:2009—07-07

修回13期:2009-08—26

万方数据

60 2009,45(35)

Computer Engineering and Applications计算机工程与应用

控制的快速乘法器结构。通过增加控制信号和多路选择器,乘 法器在域宽小于最大域宽的一半时能将速度提高—倍。它不占 用额外的存储空间,并能扩展应用于串并混合结构中。

CLA加法器。进一步对于有限域G及2“)来说,其乘法器还可以 按串并行方式的不同一般分为三类:比特串行乘法器、并行乘

法器和混合乘法器。若乘法器在每个时钟周期产生出乘积的一 个位,则称它为位串行的。若乘法器在每个时钟周期产生出乘 积的多个位,则称它为数字串行的。若乘法器在—个时钟周期 产生出乘积的所有位,则称为并行的。从理论上来说,串行乘法 器的时间和面积复杂度一般为0(m),并行乘法器的时间和面

Computer Engineering and Applications计算机工程与应用

◎研发、设计、测试0

2009,45(35)

59

GF(m)上的一种可并行快速乘法器结构

马自堂1,段斌2,刘云飞2

MA Zi-tangI,DUAN BinI,LIU Yun-fei2

1.解放军信息工程大学电子技术学院,郑州450004 2.防空兵指挥学院防空导弹系,郑州450052

(6孵(髫)+6la(茹)·菇+…+ba_ct(戈)·茹m-2+6m_母(茹)·茹”1)mod.八茹)-

boa(x)modf(x)+b18(z)·xmodf(x)+…+6+1a(茗)·髫~nlod火茗) 按照对b各位处理顺序的不同,可以将串行乘法器分为高

位优先(MSB)和低位优先(LsB)两种。

算法1 GF(2“)上的高位优先乘法器[,】

carl哪the rim multiplier.One control signal and six two-way muxes a坨added in the multiplier.and it

fixed hardwal'e resource

to compute two multiplication parallelly,when the field length is less than half of the maximum.The proposed multiplier arehitee-

2可重构的高位优先乘法器

m—l

在多项式基{1,戈,…,戈”1l表示下,口(茹)=∑ai石‘,6(戈)=

i=O

m一1,h一1

∑6。茹‘GF(2“)∥省)≈“+r(茹)≈“+∑,f髫‘为CF(2”)的约减

i=0

i=O

多项式,则

c(x)铷(并)b(x)moaf(髫)=

a(x)(bo+b rx+…+6+Ix“)rood火菇)=

2.2.1同时执行 (c“,…c1,co)+-左移(c㈣…cI,co)+c,卜l(‰,…rl,r0) (c扣l'.一,c肿l,c。)}左移(cM,…c肿l’c。)+c一(~I’.”r肿l,k)

2.2.2同时执行

(c纠,…CI,,Co)-(c,l,…cl,co)+6i(吗卜l,…,嘞,aa) (C2a--l,…Cr,+l c。)+-(c纠,…Cn*l,c。)+6湘(%.1,…,‰l,an) 否则

Z b4。√,o≤i≤s一2

j.o

Bi(茗)= 珥‘*七一l ∑6。。√,i=s一1

则 c(x)=a(x)b(x)mod火石)=

口(算)(菇‘mE.1(菇)帆‘mB-2(茗)+…+

f曰,(髫)+既(戈))mod“茗)=

((…((口(茹)E.。(并))≯+口(菇)E≈(名))石‘+…+

a(x)81(菇))f+口(石)Bo(茹))mod人茹)

在高位优先乘法器的基础上,提出了一种在G,(2“)上可

作者筒介:马自堂(1962一),男,教授,硕士生导师,主要研究领域为信息系统安全,嵌入式系统设计,EDA技术;段斌(1981一),男,硕士研究生,主要

研究领域为信息系统安全,嵌入式系统设计;刘云飞(1979一),女,讲师,主要研究领域为嵌入式系统设计,制导与仿真。

每个寄存器的长度为m。图l描述了在任意域c以r)上,m E {m,,啦,…,巩}和任意约减多项式中实现乘法的MSB。控制器按 从高到低的顺序载入口,b和r的比特位,并将无用位置0。虽然 无用位也被时钟所驱动,但由于无用位的内容未发生变化,所 以其功耗几乎为零。这种乘法器能用—个计数器、两个m位存 储器和两个m位移位寄存器在m个时钟周期内执行一次乘法 运算。

I

西门㈩

图2改进后的MSB结构

表l 串并行模式控制说明

壅堡

N<m≤M 凸咖≤Ⅳ

兰!!墅兰

0 串行

1并行

望矍 在m个时钟周期内计算—个m位乘法

在m个时钟周期内计算两个m位乘法

算法2改进后的可重构高位优先(MSB)乘法器 输入:口=(%I'…,%,稚I,…,嘞,ao),6=(6,l,…,6。,b,卜l,…,

1引言 有限域在密码学领域有着广泛的应用。在公钥密码RSA

和ECC等算法设计中,有限域乘法运算是最重要的一种运算。 乘法运算的速度会对算法整体速度有很大影响,因此,设计复 杂性低、速度快的乘法运算算法和乘法器结构对提高加解密运 算速度非常重要。

乘法器按实现结构的不同可分为三类,一是反复式乘法器 (Iterative Structure Multiplier)lllJ移位累加乘法器,二是阵列式 乘法器(Array Structure Multiplier),三是树状结构乘法器(Tree Structure Multiplier)。反复式面积最小,但所耗时钟数最多;阵 列式乘法器速度快些,结构规则,但关键路径时延和面积都随 乘数被乘数的比特位同比递增;现多采用树状结构乘法器,即部 分积+压缩树+最终加法器结构,如Booth编码器+Wallace树+