梯形晶体带通滤波器设计

数字梯形成形滤波器的模块化设计

数字梯形成形滤波器的模块化设计王毅男;林伟【摘要】针对数字梯形成形滤波器在数字化多道脉冲分析仪中的应用,给出其z变换方法的推导过程,并通过傅里叶变换讨论其滤波功能.从实际应用出发,对梯形成形滤波器进行模块化设计,使设计更有利于可编程逻辑器件的实现,可以简单灵活地调节梯形形状以适应不同的工作环境.利用Matlab软件对设计进行原理仿真,验证了模块化设计的正确性,并通过加入高斯白噪声的方法讨论其滤波特性.使用FPGA配合嵌入式逻辑分析仪给出梯形成形滤波器的硬件实现及仿真,验证了系统设计的正确性.【期刊名称】《自动化仪表》【年(卷),期】2015(036)010【总页数】4页(P89-91,95)【关键词】梯形成形;数字化滤波;多道脉冲幅度分析仪;延迟可调;FPGA【作者】王毅男;林伟【作者单位】上海应用技术学院电气与电子工程学院,上海201418;上海应用技术学院电气与电子工程学院,上海201418【正文语种】中文【中图分类】TH83;TN71320世纪90年代,基于数字信号处理技术,提出了新的核脉冲能谱分析技术。

数字电路技术的最大优点是灵活性,它可以综合成各种滤波器,使系统达到更高的信噪比,获得更好的能量分辨率,这些优点也是模拟电路难以实现的,甚至不可能实现的[1-2]。

多道脉冲幅度分析器是通过测量核辐射探测器输出的电脉冲信号来获取核辐射信息,该信号具有较快的上升沿,有丰富的高频成分。

由于前端电路的噪声影响和数模转换器采样频率的限制,不可能采集到每个脉冲信号的最大幅值[3-4],因此在高精度要求下,“直接数据采集法”是不可行的,而梯形成形算法可以弥补这个不足。

梯形成形滤波器是将输入的下降沿衰减的指数信号成形为梯形脉冲信号输出。

已有研究证明,当只考虑电压和电流噪声,探测器收集电荷的时间不为零时,梯形成形滤波器是最优滤波器,并且非常适合用数字方法实现[5]。

为提高梯形成形算法的实用性,本文对算法进行模块化设计,从更适合可编程逻辑器件实现的角度出发,完成梯形成形滤波器的结构设计。

改进型梯形谐振滤波器的带通滤波器设计

一

级梯形 滤波器 的理论频 响为

Zp | | R

o Z。 。t 2一 u +Zs +Ri

() 6

经过调整各个参数 , 到的频 率响应如 图6 得 所示 , 中心频率为 875M z通 带带宽为 4 z最大 的插 9. H , 0MH ,

1 g 2=

动系统 ( S 等 。与此 同时 , G M) 人们对 通信设 备的关键 器件 之一 的滤 波器 , 提 出了越来 越 高 的要 求 , 也 主要 体现 在工 作频 率更 高 , 宽更 宽 , 带 同时要求 具有 窄 的

过渡带 。

2 单端对 声表 面波谐振器原理

典 型 的单端 对声表 面波谐 振器 如 图 1 所示 , 中间 部分 为叉 指换 能器 ( trDg a Tasu e, T , I e— i t rnd crI ) 上 n il D 下两根汇 流条分别 连接发射 电极和接 收电极 , 右两 左 边 为金 属反 射栅 , 当输入适 当频率 的信号 时 , 叉指 换

z: 一

jC 0-01 o。  ̄ J )- .

() 4

一

jc 一; ∞ ∞) (

() 5

以 1 1 为输 入端 , , 为输 出端 。 ,端 2 2端

运用A WR软件 , 据 图 5的等 效 电路 图进行 仿 根 真 。最终 的频率 响应图如 图 6 所示 。

单 端谐振器 构成 , 并联 支路 由单 端对谐振 器与 电容元 件 组成 , 级联 时加 入容性 元 件进行 补偿 , 此基 础 在 在

上 级 联 了五 级 梯形 谐 振 器结 构 , 计 出 中心频 率 为 设 875M , 入损耗小 于 3 B, 9 . Hz插 . d 带外 抑制达 3 B以 6 0d 上 的带通滤波器 。

带通滤波器设计

LC椭圆函数带通滤波器设计要求带通滤波器,在15kHz~ZOkHz的频率范围内,衰减最大变化1dB,低于14.06kHz和高于23kHz频率范围,最小衰减为50dB,Rs=RL=10kΩ。

③运行Filter Solutions程序。

点击“阻带频率”输人框,在“通带波纹(dB)”内输人0.18,在“通带频率”内输人1,在“阻带频率”内输人1.456,选中“频率单位-弧度”逻辑框。

在“源阻抗”和“负载阻抗”内输人1。

④点击“确定阶数”控制钮打开第二个面板。

在“阻带衰减(dB)”内输人50,点击“设置最小阶数”按钮并点击“关闭”,主控制面板上形式出“6阶”,选中“偶次阶模式”逻辑框。

⑤点击“电路”按钮。

Filter s。

lutions提供了两个电路图。

选择“无源滤波器1”,如图1(a)所示。

⑥这个滤波器必须变换为中心频率ω0=1的归一化带通滤波器。

带通滤波器的Q 值为:把所有的电感量和电容值都乘以Qbp°然后用电感并联每一个电容、用电容串联每一个电感使其谐振频率为ω0=1,该网络被变换为带通滤波器。

使用的谐振元仵是原元件值的倒数,如图1(b)所示。

⑦按照图1的方式转换Ⅱ型支路。

变换后的滤波器见图1(c)。

在原理图下标出了以rad/s为单位的谐振频率。

⑧用中心频率fo=17.32kHz和阻抗10kΩ对滤波器进行去归一化以完成设计。

将所有的电感乘以Z/FSF,所有的电容除以z×FSF,其中z=104,FSF=2πfe=1.0882×105。

最终的滤波器见图1(d)。

图1(c)中的归一化谐振频率直接乘以几何中心频率fo=17.32kHz即可得到谐振频率。

频率响应见图1(e)。

滤波器的主要参数滤波器的主要参数(Definitions) 中心频率(Center Frequency):滤波器通带的中心频率f 0 ,一般取f 0 =(f 1 +f 2 )/2,f 1 、f 2 为带通或带阻滤波器左、右相对下降1dB或3dB边频点。

带通滤波器的设计步骤

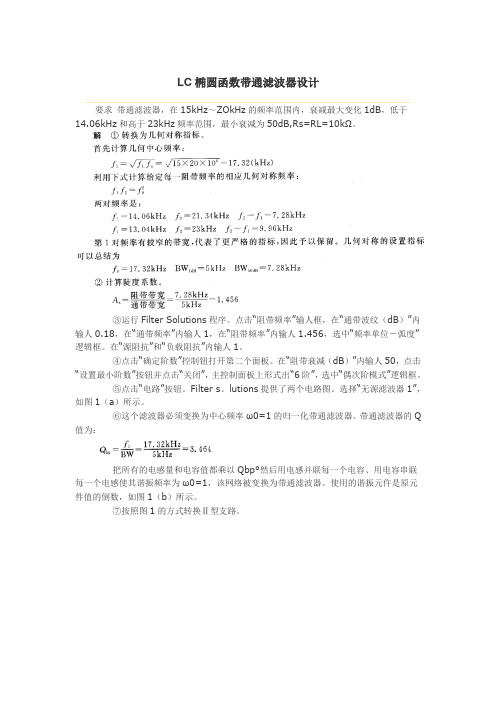

带通滤波器设计流程滤波器是具有频率选择性的双端口器件。

由于谐振器的频率选择性,所以规定的频率信号能够通过器件,而规定频率信号以外的能量被反射,从而实现频率选择的功能。

滤波器从物理结构上,就是由一些不同的单个谐振器按相应的耦合系数组合而成,最后达到规定频率的信号从输出端通过的目的。

1. 滤波器技术指标1.1工作频率范围: 1060MHz±100MHz 1.2插入损耗: 0.5dB max 1.3驻波比: 1.2 max1.4带外抑制: >20dB@f0±200MHz>35dB@f0±300MHz >60dB@f0±500MHz1.5寄生通带: f >3500MHz 以上,对衰减不作要求1.6工作温度: -55°Cto+85°C 1.7最大输入脉冲功率:400W ; 最大输入平均功率:20W2.滤波器设计原理图1 滤波器原理图3.滤波器结构选择 3.1物理结构选择根据以上技术指标选择腔体交指型带通滤波器,主要的原因是因为它有着良好的带通滤波特性,而且它结构紧凑、结实;且容易制造;谐振杆端口2的长度近似约为λ/4(波长),故第二通带在3倍fo上,其间不会有寄生响应。

它用较粗谐振杆作自行支撑而不用介质,谐振杆做成圆杆,还可用集总电容加载的方法来减小体积和增加电场强度,而且它适用于各种带宽和各种精度的设计。

3.2电路结构的选择根据以上技术指标选择交指点接触形式,主要的原因是它的谐振杆的,载TE一端是开路,一端是短路(即和接地板接连在一起),长约λ/40M(电磁波)模,杆1到杆n都用作谐振器,同时杆1和杆n也起着阻抗变换作用。

4.电路仿真设计如图2模型选择。

采用An soft公司的Serenade设计,根据具体的技术指标、体积要求和功率容量的考虑,此滤波器采用腔体交指滤波器类型,使用切比雪夫原型来设计,用圆杆结构的物理方式来实现。

图2模型选择如图3滤波器综合指标选择。

带通滤波器设计流程 耦合矩阵

带通滤波器设计流程耦合矩阵带通滤波器是一种常用的滤波器,可以将一定频率范围内的信号通过,而将其他频率范围的信号抑制或削弱。

在设计带通滤波器时,我们需要按照一定的流程来进行,以下是带通滤波器设计的一般流程。

1.确定带通滤波器的需求在设计带通滤波器之前,首先需要明确带通滤波器的设计要求。

这包括带通滤波器的中心频率、通带宽度、阻带宽度、衰减量等参数。

这些参数会根据应用场景的不同而有所差异。

确定这些参数是设计带通滤波器的基础。

2.选择合适的滤波器类型根据设计要求,选择合适的滤波器类型。

带通滤波器有很多种类型,包括Butterworth滤波器、Chebyshev滤波器、椭圆滤波器等。

每种滤波器类型都有其自身的特点和适用范围。

根据设计需求选择合适的滤波器类型。

3.设计滤波器的阶数滤波器的阶数决定了滤波器的衰减量和相位响应。

阶数越高,滤波器的衰减量越大,但相应的计算复杂度也会增加。

根据设计要求和滤波器类型的特性,确定滤波器的阶数。

4.确定滤波器的传递函数根据选择的滤波器类型和设计要求,确定滤波器的传递函数。

传递函数可以通过一系列的公式或者图表来表示,它描述了输入信号和输出信号之间的关系。

根据设计要求和传递函数,可以得到滤波器的具体参数和频率响应。

5.计算滤波器的频率响应根据确定的滤波器传递函数,可以计算滤波器的频率响应。

频率响应可以表达滤波器对输入信号的不同频率分量的响应程度。

通过计算频率响应,可以对滤波器的性能进行评估和优化。

6.进行滤波器参数的调整和优化根据滤波器的频率响应,可以对滤波器的参数进行调整和优化。

这包括调整阻带范围和通带范围,优化滤波器的衰减量和通带波动等。

通过不断的调整和优化,可以得到满足设计要求的带通滤波器。

7.实现滤波器将滤波器的设计参数转化为具体的电路或者数字滤波器的实现。

这需要根据具体的实际应用场景和设计要求选择合适的电路拓扑结构和滤波器器件。

对于数字滤波器,可以采用差分方程、传输函数或者直接形式实现。

声表面波窄带梯形滤波器的仿真与设计

收稿日期:2010 07 11 作者简介:黄华(1986 ),男,江苏常州人,硕士生,主要从事声表面波梯形滤波器的研究。

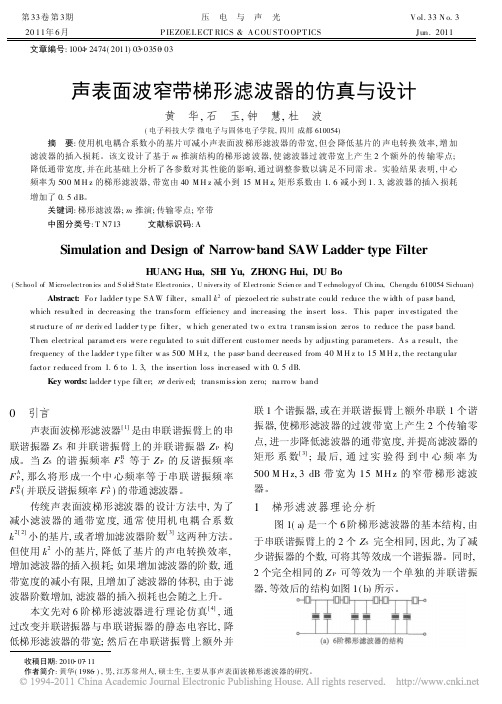

文章编号:1004 2474(2011)03 035003声表面波窄带梯形滤波器的仿真与设计黄 华,石 玉,钟 慧,杜 波(电子科技大学微电子与固体电子学院,四川成都610054)摘 要:使用机电耦合系数小的基片可减小声表面波梯形滤波器的带宽,但会降低基片的声电转换效率,增加滤波器的插入损耗。

该文设计了基于m 推演结构的梯形滤波器,使滤波器过渡带宽上产生2个额外的传输零点;降低通带宽度,并在此基础上分析了各参数对其性能的影响,通过调整参数以满足不同需求。

实验结果表明,中心频率为500M H z 的梯形滤波器,带宽由40M H z 减小到15M H z,矩形系数由1.6减小到1.3,滤波器的插入损耗增加了0.5dB 。

关键词:梯形滤波器;m 推演;传输零点;窄带中图分类号:T N713 文献标识码:ASimulation and Design of Narrow band SAW Ladder type FilterHUANG Hua,SHI Yu,ZHONG Hui,DU Bo(School of M icroelectron ics and S olid S tate Electronics ,U nivers ity of Electronic S cien ce and T echnologyof Ch ina,Chengdu 610054Sichuan)Abstract:Fo r ladder ty pe SA W f ilter ,small k 2of piezoelect ric substr ate could r educe the w idth o f pass band,which resulted in decreasing the transfor m efficiency and incr easing the insert loss.T his paper inv estigated the st ructur e of m deriv ed ladder ty pe filter ,w hich g ener ated tw o ex tra t ransm ission zer os to r educe t he pass band.T hen electr ical par amet ers wer e r egulated to suit differ ent custo mer needs by adjusting parameters.A s a r esult,the frequency of the ladder t ype filter w as 500M H z,t he pass band decr eased from 40M H z to 15M H z,the rectang ular facto r r educed fr om 1.6to 1.3,the inser tion loss incr eased w ith 0.5dB.Key words:ladder t ype filt er;m deriv ed;transmission zero;na rro w band0 引言声表面波梯形滤波器[1]是由串联谐振臂上的串联谐振器Z S 和并联谐振臂上的并联谐振器Z P 构成。

数字梯形成形滤波器的模块化设计

数字梯形成形滤波器的模块化设计王毅男,等数字梯形成形滤波器的模块化设计Modular Design of Digital Trapezoidal Shaping Filter王毅男林伴(上海应用技术学院电气与电子工程学院,上海201418)摘要:针对数字梯形成形滤波器在数字化多道脉冲分析仪中的应用,给出其^变换方法的推导过程,并通过傅里叶变换讨论其滤波 功能。

从实际应用出发,对梯形成形滤波器进行模块化设计,使设计更有利于可编程逻辑器件的实现,可以简单灵活地调节梯形形状 以适应不同的工作环境。

利用Matlab软件对设计进行原理仿真,验证了模块化设计的正确性,并通过加入高斯白噪声的方法讨论其 滤波特性。

使用F P G A配合嵌入式逻辑分析仪给出梯形成形滤波器的硬件实现及仿真,验证了系统设计的正确性。

关键词:梯形成形数字化滤波多道脉冲幅度分析仪延迟可调FPGA中图分类号:TH83;TN713 文献标志码: A DO I:10.16086/j. cnki. issn l000 -0380.201510022Abstract :In accordance with the application of digital trapezoidal shaping filter in multi-channel pulse analyzer, the derivation process of its z transform method is given, and its filtering function is discussed through Fourier transform. From the practical application, the modular design of trapezoidal shaping filter is conducted, thus the design is more conductive to the realization of the programmable logic devices, and to adapt different working environment, the shape of trapezoid can be adjusted flexibly. The principle simulation of the design is conducted by adopting Matlab software, the correctness of the modular design is verified, and the filtering characteristics are discussed through adding Gaussian white noise. The hardware implementation and simulation of such filter are given using FPGA and embedded logic analyzer, the correctness of the system design is verified.Keywords :Trapezoidal shaped Digital filtering Multi-channel pulse amplitude analyzer Adjustable delay FPGA〇引言20世纪90年代,基于数字信号处理技术,提出了 新的核脉冲能谱分析技术。

带通滤波器设计最新123

目录1 技术指标 (1)2 设计方案及其比较 (1)方案一 (1)2.2 方案二 (4)方案比较 (7)3 实现方案 (8)实现方案所用到的元器件 (8)实现方案的原理图 (8)实现方案的原理分析 (9)实现方案的实物图 (10)4 调试过程及结论 (10)调试过程 (10)调试及结论 (11)5 心得体会 (12)6 参考文献 (13)带通滤波器设计1 技术指标设计一个带通滤波器要求其技术指标要满足一下标准:上限截止频率:f=30kHz,下限截止频率:f=5KHz通频带带宽:Bw=25KHz,阻带衰减速率为:-40dB/10倍频电压增益:4<A v<92 设计方案及其比较滤波器:滤波器在电子电路中是一种对干扰信号或是无用的信号进行滤除的一种装置,包括电抗性元件L、C构成的无源滤波器、由集成运算放大器组成的有源滤波放大器,以及三极管滤波器等。

滤波器分类:按滤波器的组成元件的不同可以分为无源滤波器和有源滤波器。

按照滤波器的频率特性不同,滤波器通常可以分为四类:低通滤波器、高通滤波器、带阻滤波器、带通滤波器。

低通滤波器:它允许信号中的低频或直流分量通过,抑制高频分量或干扰和噪声。

高通滤波器:它允许信号中的高频分量通过,抑制低频或直流分量。

带通滤波器:它允许一定频段的信号通过,抑制低于或高于该频段的信号、干扰和噪声。

带阻滤波器:它抑制一定频段内的信号,允许该频段以外的信号通过。

两类响应巴特沃斯响应〔最平坦响应〕巴特沃斯响应能够最大化滤波器的通带平坦度。

该响应非常平坦,非常接近DC信号,然后慢慢衰减至截止频率点为-3dB ,最终逼近-20ndB/decade 的衰减率,其中n为滤波器的阶数。

巴特沃斯滤波器特别适用于低频应用,其对于维护增益的平坦性来说非常重要。

切贝雪夫响应在一些应用当中,最为重要的因素是滤波器截断不必要信号的速度。

如果你可以接受通带具有一些纹波,就可以得到比巴特沃斯滤波器更快速的衰减。

梯形晶体带通滤波器设计

梯形晶体带通滤波器设计BG6RDF晶体带通滤波器(crystal band-pass filter)是短波收发信机中常见的核心部件,晶体滤波器的优劣直接影响到短波接收机的性能。

梯形晶体带通滤波器(crystal ladder band-pass filter,以下简称梯形晶体滤波器),见图1,是一种常见的晶体带通滤波器的形式。

由于其便于DIY,因此在DIY短波收发信机时,梯形晶体滤波器被广泛采用。

本文是我学习DIY梯形晶体滤波器后一些资料的总结和心得。

A.电路图B.仿真结果图1:6晶体梯形滤波器一. 晶体带通滤波器的性能描述晶体带通滤波器的性能主要指标如下:中心频率:fo,滤波器通带中心频率带宽:BW,通常指-3dB带宽,用于SSB的晶体滤波器的带宽通常在1.8KHz到2.8KHz 之间。

矩形系数:通常用(-60dB带宽)÷(-6dB带宽)表示。

矩形系数约接近1越好,即滤波器的频幅曲线越接近矩形,这样对带外临近频率的衰减越大。

插入损耗:插损,滤波器通带的插入损耗,通常以dB表示。

插损当然是越小越好,但是插损和制作晶体滤波器的Q值、晶体滤波器的中心频率、晶体滤波器的带宽有一定关系。

简单地说就是晶体Q值越高,制作出的滤波器插损越小;带宽越大,插损越小。

纹波系数:ripple,指通带内频幅曲线的波动幅度,通常以dB表示。

当然纹波系数越小越好,但有些形式的滤波器具有这样的特性,就是在加大纹波系数后,阻带曲线能变得更为陡峭,最终的设计需要设计者权衡。

阻抗:指滤波器的终端阻抗,在特定的终端阻抗下,滤波器的响应才能够达到特定的性能。

如果终端阻抗不匹配,滤波器的性能将偏离设计值。

滤波器还有一些其他性能指标,如群延迟(group delay),参考文献3中指出,群延迟特性会影响收发信机的听感。

二. 晶体的测量要设计晶体滤波器,必须了解自己手头晶体的参数,为此,必须对晶体参数进行测量。

说到晶体参数,不得不说晶体的等效模型,见图2。

体声波梯形滤波器的布局设计方法

中 图 分 类 号 : TN603.5; TN629.1

文 献 标 志 码 : A doi:10.¨ 884/HPI PB201830.1701 1 2

随着 无线 通讯 设备 的快 速普 及 和用 户需 求 的不断 扩展 ,手 持移 动通 信 产 品正在 往小 型化 和轻 便化 发展 ,而 随着产 品尺寸 的减 小 ,产 品价格 不断 降低 ,对 其功 能 的要 求 却逐 渐 增 强 。在手 持 移 动通 信 产 品 中 ,射 频 滤波 器 已成 为 电子 系统小 型化 和集 成化 的瓶颈 之一 。在 保持 滤 波器性 能 的前 提下 ,需要 进 一步 缩小 滤波 器体 积 ,增加 相 同面积 晶 圆上 的芯 片数 量 ,提高 经 济 效 益 。体 声 波 (BAw )滤 波 器 是 通过 多 个 BAW 谐 振 器 串 、并 联 构 建 而 成 的 ,具 有工作 频 带宽 、体 积小 、品质 因数 (Q值 )高 、带 外 抑 制 好 等优 点 口 。除 了 可 以使 用 体 积小 的体 声 波谐 振器 (BAWR)以外 ,也 可 以优化 BAWR 的布 局 ,提 高 晶 圆 的面 积 利 用 率 。但 由于 BAW R之 间 距 离 太 小 会 产 生其 他 干扰 ,从而 影 响滤波 器 的性 能 ,例 如 电磁耦 合 。。 等 ,因而 ,在 布局 设计 过 程 中 ,不 得 不 考 虑这 些 干 扰 对 芯 片性 能 的影 响 。如何 在保 证 器件性 能 的前 提下 ,最 大 限度 地减 小 布 局 面积 ?针 对 这一 问题 ,文 献 [4]提 出 了一 种 布局 设计 方法 :将 串联 BAWR直 线形 排列 或 折线形 排 列 。但 这两 种 方 法 只排 列 串联 体 声 波谐 振 器 ,并 没 有 考 虑如 何排 列并 联体 声波 谐 振器 ,且 没有说 明如何 选择 串联 体声 波 谐 振器 的排 列方 式 。 因此 ,本 文对 于 BAW 梯形 滤 波器 的布 局设 计提 出了设计 准 则 和设计 流程 ,综 合考 虑 了 串 、并联 BAWR的排 列方 式 ,并给 出 一种 串联 体 声波 谐振 器排 列方 式 的选 择方法 。 以一 个 5阶 BAW 梯形 滤波 器 为例 ,展示 了布 局设 计流 程 。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

梯形晶体带通滤波器设计BG6RDF晶体带通滤波器(crystal band-pass filter)是短波收发信机中常见的核心部件,晶体滤波器的优劣直接影响到短波接收机的性能。

梯形晶体带通滤波器(crystal ladder band-pass filter,以下简称梯形晶体滤波器),见图1,是一种常见的晶体带通滤波器的形式。

由于其便于DIY,因此在DIY短波收发信机时,梯形晶体滤波器被广泛采用。

本文是我学习DIY梯形晶体滤波器后一些资料的总结和心得。

A.电路图B.仿真结果图1:6晶体梯形滤波器一. 晶体带通滤波器的性能描述晶体带通滤波器的性能主要指标如下:中心频率:fo,滤波器通带中心频率带宽:BW,通常指-3dB带宽,用于SSB的晶体滤波器的带宽通常在1.8KHz到2.8KHz 之间。

矩形系数:通常用(-60dB带宽)÷(-6dB带宽)表示。

矩形系数约接近1越好,即滤波器的频幅曲线越接近矩形,这样对带外临近频率的衰减越大。

插入损耗:插损,滤波器通带的插入损耗,通常以dB表示。

插损当然是越小越好,但是插损和制作晶体滤波器的Q值、晶体滤波器的中心频率、晶体滤波器的带宽有一定关系。

简单地说就是晶体Q值越高,制作出的滤波器插损越小;带宽越大,插损越小。

纹波系数:ripple,指通带内频幅曲线的波动幅度,通常以dB表示。

当然纹波系数越小越好,但有些形式的滤波器具有这样的特性,就是在加大纹波系数后,阻带曲线能变得更为陡峭,最终的设计需要设计者权衡。

阻抗:指滤波器的终端阻抗,在特定的终端阻抗下,滤波器的响应才能够达到特定的性能。

如果终端阻抗不匹配,滤波器的性能将偏离设计值。

滤波器还有一些其他性能指标,如群延迟(group delay),参考文献3中指出,群延迟特性会影响收发信机的听感。

二. 晶体的测量要设计晶体滤波器,必须了解自己手头晶体的参数,为此,必须对晶体参数进行测量。

说到晶体参数,不得不说晶体的等效模型,见图2。

图2:晶体等效模型图2中Lm称为等效串联电感,也有Cm称为等效串联电容,梯形晶体滤波器主要利用晶体的串联谐振,因此这两个参数是晶体测量的重点。

Rm称为等效串联电阻,这个值实际体现了晶体的Q值,Q值越高,Rm越小。

C0称为等效并联电容,对于梯形晶体滤波器,C0是有害的。

在了解了晶体的等效模型后,我们看看晶体的测量方法。

晶体的测量方法有很多种,强烈建议阅读参考文献1和参考文献2。

这里只详细介绍G3UUR的振荡器法,因为这种方法简便易行,不需要使用昂贵的网路分析仪,测量仪器仅需要一个频率计。

G3UUR振荡器的电路如图3所示,图3:G3UUR晶体测量振荡器电路图该电路中,Q1、Q2采用常见的2N4401、2N3904、S9014等小功率NPN型三极管都可以满足20MHz以内晶体的测量要求。

具体测量方法是:1.将频率计接在Output输出端。

2.闭合电路中的开关,旁路Cs使晶体Y1的一端直接接地,测量振荡器的输出频率,这时测出的频率记为f3。

3.断开电路中的开关,是晶体Y1的一端通过Cs接地,测量震荡器的输出频率,这时测出的频率记为f2。

f2>f3。

4.如果有LC表,用LC表测量Y1的等效并联电容C0。

如果没有也没关系,C0通常是3pF-5pF之间。

C0测量精度对最终测量的结果影响不大。

测量完成后,将测量值带入下面的计算公式:332))(0(2f f f C C C S M −+= M M C f L 23)2(1π=有些滤波器设计软件或仿真软件在设计或仿真前需要输入晶体的其他参数,比如Q 值,等效串联电阻Rs ,并联谐振频率fp 等。

这些参数对业余条件下的滤波器设计没有质的影响,这里给出一些近似的方法。

市售的晶体,通常Q 值是6万到10万之间, Q 值主要影响滤波器的插入损耗; Rs 可通过Q 值计算得到:QL f R M s 32π= 并联谐振频率可通过计算得到:103+=C C f f M p 上面这些公式看上去可能有些眼晕,实际上可自己设计一个EXCEL 的表格将公式设置好,让EXCEL 自动计算就行了,非常方便。

当然,如果手上有矢网,N2PK VNA 之类的仪器,测量晶体就不用这么麻烦了。

三. 梯形晶体滤波器的类型不同的梯形晶体滤波器有不同的性能特点,在设计滤波器前必须有一个认识。

这里主要介绍巴特沃斯(Butterworth),切比雪夫(Chebyshev)和Cohn 滤波器。

巴特沃斯型滤波器的主要特点是通带平坦,矩形系数较差。

切比雪夫型滤波器的主要特点是通带有纹波,而且纹波越大,矩形系数越好。

Cohn 滤波器也称作minimum loss 滤波器,结构简单(所有电容的电容量相同),所有晶体的串联谐振频率必须尽量相同,插损低,通带可做的比较平坦。

四. 滤波器设计方法晶体参数测量完了,就可以开始设计滤波器了。

这里主要介绍三种方法,我把这三种方法分别称为G3JIR 、W7ZOI 和AADE 方法。

1. 用G3JIR 法进行滤波器设计G3JIR 的方法参见参考文献6,另外参考文献7还提供了一个网页风格的设计器,使用起来非常方便。

设计步骤:A . 采用G3UUR 的方法,或参考文献7中提供的方法测量晶体参数,设计器需要提供的晶体参数包括f3, fp, Cm(设计器中名为Cs)。

B . 输入晶体滤波器的节数,纹波,带宽等指标后,设计器可自动计算出滤波器有关参数,如中心频率、阻抗,电路中电容容量的和电路形式。

输入纹波为0,则生成巴特沃斯型滤波器,输入其它值则生成切比雪夫型滤波器。

实际上,图1就是用G3JIR 法设计的。

2. W7ZOI 法G3JIR 法非常方便,但也有一些问题,比如滤波器中各晶体要求串联谐振频率一致,现有的设计器最高只支持8节滤波器,滤波器终端阻抗无法调整等问题。

而W7ZOI提供的设计方法就较好地解决了上述问题。

同时W7ZOI还为这种方法设计了若干程序用以进行自动化的设计和仿真,这些程序随参考文献3和参考文献4这两本书配套发行。

这里主要介绍的是参考文件3中配套的XLAD和GPLA。

设计步骤:A.运行XLAD,输入晶体参数,包括:晶体串联谐振频率,Lm(Motional L), Q值(Q-u), C0。

B.输入滤波器带宽和节数。

C.点击“2A. Chebyshev”按钮,输入纹波系数,计算k、q系数。

关于k、q系数可阅读参考文献4(慎入,以防公式过敏导致的口眼歪斜)。

D.输入端阻抗“End Resistance”,点击“4.Match Ends”,软件自动计算两端的并联电容容量以匹配到指定阻抗。

注意,这里的阻抗不是任意设置的,有一定的约束条件。

E.点击“5.Calculate Coupling”,软件自动计算并联耦合电容。

F.点击“6.Tune the Filter”,软件自动计算串联调谐电容,如果串联调谐电容显示为99999,则不需要串联调谐。

G.通过菜单File->Save as…,将刚才的设计输出存储到一个扩展名为.cir的文件中。

H.运行GPLA,通过菜单File->Open…,将刚才保存的文件打开。

点击“Plot”,软件将画出滤波器的响应曲线,其中红色S21为正向传输曲线,蓝色S11为输入端口的反射曲线。

点击“Click to Review Circuit”可看到滤波器电路的参数,包括端阻抗,并联电容,串联电容等。

XLAD最高可支持10节晶体滤波器,参考文献4的配套程序中,x.exe,l.exe和gpla.exe 也可以完成上述功能,并且最高能支持48节晶体滤波器,但是这3个程序是DOS下的,操作不方便。

如果有兴趣可参阅参考文献8和参考文献9的设计过程。

3.AADE方法提到滤波器设计不能不说AADE Filter Design这个软件,该软件可在参考文件12所列地址下载。

AADE Filter Design支持的滤波器种类非常多,使用也很方便,不仅可以设计而且可对设计结果进行仿真。

就梯形晶体滤波器设计而言,我认为AADE设计方法相比W7ZOI 方法仍有不足,主要是阻抗匹配需要另外增加LC器件,对晶体频率差异的调整不方便。

五. 设计实例因为W7ZOI方法的功能最强,使用最复杂,我以该方法为例,介绍一个滤波器的设计实例。

这个滤波器是频率9MHz,6节,0.5dB纹波切比雪夫型,带宽为2.4KHz,端阻抗500欧姆。

测量出来的晶体参数如下:串联谐振频率f3=8.9973MHz等效串联电容Cm= 22.406fF等效串联电感Lm=13.96534mH等效串联电阻Rm=9.868Ω等效并联电容C0=4.823pFQ值为79687按照上面所说的方法,在XLAD中设计滤波器,界面如图4:按上面的方法在GPLA中对刚才的设计进行仿真,结果如图5所示:为了解释并联耦合电容和串联调谐电容的用法,该滤波器的电路图如图6所示:图6:XLAD设计的滤波器电路实例六. 深入理解下面再来谈一些深入的话题,在DIY过程中,这些内容有现实意义。

1.mesh tuning在上面谈到了G3JIR的设计方法有个缺点是滤波器中各晶体要求串联谐振频率一致,在上面介绍的W7ZOI方法中看到各晶体的串联谐振频率也是一致的。

而在实际制作过程中经常遇到手头的晶体串联谐振频率差异较大的情况。

幸运的是,W7ZOI也给我们提供了解决方案。

如图6中弧形箭头所示,我们可以看到[C12,CR2,CT2,C23], [C23,CR3,CT3,C34], [C34,CT4,CR4,C45], [C45,CT5,CR5,C56]组成了4个晶体滤波器的的片段,这样一个片段称为mesh(在剑桥国际英语字典中mesh的中文解释是网孔、网,这样翻译感觉放在这里感觉不妥,下面全部都称mesh)。

那么[C1,CR1,C12]和[C56,CR6,CN]是不是mesh呢,也是的,但需要进行以下变换,这个下面会介绍。

一个mesh两端是并联耦合电容,中间是一个晶体外加一个串联调谐电容(这个电容也可以没有,比如Cohn晶体滤波器中就没有串联调谐电容)。

按照滤波器理论,每个mesh的谐振频率应该是一样的(见参考文献8)。

在图6中,单独看每个mesh,三个电容和晶体都是串联关系,我们会发现这三个电容串联后的电容量是相同的,按照公式C=1/(1/C1+1/C2+1/C3)计算,串联电容都是44.3pF。

这三个电容与晶体串联后,提高了晶体的串联谐振频率,按照公式f=1/(2πsqrt(LC))计算(其中L用晶体的等效串联电感量Lm,C用44.3pF串联晶体的等效串联电容量Cm),晶体串联谐振频率提高到了8.999574MHz。

如果晶体的等效并联电容C0为0,则这个频率就是晶体滤波器的中心频率,正是因为有了C0,mesh的谐振频率要低于这个频率,晶体滤波器的中心频率也低于这个频率。