2014EDA考试设计试卷

2014数电考试题

判断题。

1.8421BCD码是二一十进制码。

(√)2.与逻辑是至少一个条件具备事件就发生的逻辑。

(×)3.“同或”逻辑功能是两个输入变量A,B相同时,输出为1;A,B 不同时输出为0.(√)4.基本RS触发器具有“不定”问题。

(√)5.JK触发器有保持功能,但无翻转功能。

(×)6.逻辑器件74LS161是集成寄存器。

(×)7.计数器不能作为分频器。

(×)8.对于TTL门电路来说,如果输入端悬空即代表输入低电平。

(×)9.三态输出门电路的输出除了有高,低电平这两个状态外,还有第三个状态——高阻态。

(√)10.同步时序电路具有统一的时钟CP控制。

(√)二.单项选择题。

1.一个8选1的数据选择器有(8)个选择控制信号输入端。

2.n个变量,有多少个最小项(2^n)。

3.在数字逻辑电路中,利用三级管的截止状态和(饱和)状态实现开关电路的断开和接通。

4.共阳型七段数码管各段点亮需要(低电平)。

5.74LS148编码器是(8线-3线优先编码器)。

6.对于JK触发器,若J=K,则可完成(T)触发器的逻辑功能。

7.三变量逻辑函数F(A,B,C)=A+BC的最小项表示中不含下列哪项(A)。

A.m2 B.m5 C.m3 D.m78.下列逻辑代数基本运算关系式中不正确的是(C)。

A.(A+1)’=0B.A㈩B=A’B+AB’C.A+A’B=A’+BD.(A’+A’B)’=A9.常用于数据串并行转换的电路是(D)。

A.加法器 B.数值比较器 C.计数器 D.移位寄存器10.两片74LS160计数器级联后最大可组成(D)进制计数器。

A.99 B.100 C.255 D.2564.下列方法中,不能消除竞争冒险的是(B)。

A.引入封锁脉冲 B.化简电路,减少逻辑器件数目C.接入滤波电容D.引入选通脉冲5.卡诺图上变量的取值顺序是采用(A)的形式,以便能够用几何上的相邻关系表示逻辑上的相邻。

EDA试卷

一、名词解释(2个小题,每小题5分,共10分)1.逻辑适配——将由综合器产生的网表文件针对某一具体的目标器进行逻辑映射操作,(其中包括底层器件配置、逻辑分割、逻辑优化、布线与操作等,)配置于指定的目标器件中,产生最终的下载文件(如JEDEC格式的文件)的过程。

2.功能仿真——将综合后的VHDL网表文件再送到VHDL仿真器中所进行的仿真。

3、逻辑综合——将电路的高级语言描述转化成低级的,可与FPGA/CPLD或ASIC门阵列基本结构相映射的网表文件。

4、时序仿真——将接线器/适配器所产生的VHDL网表文件送到VHDL仿真器中所进行的仿真。

二、填空题(共20空,每空1分,共20分)1.FPGA的英文全称是Field Programmable Gate Array,CPLD的英文全称是Complex Programmable Logic Devices,二者在保存逻辑信息方面的区别是FPGA掉电后将丢失原有的逻辑信息而CPLD却能保持原有的逻辑信息。

2.一个相对完整的VHDL程序的三个基本组成部分别是库、程序包使用说明、实体说明和实体对应的结构体说明。

3.IEEE_1076标准程序包中定义的四种常用端口模式分别是IN模式、OUT模式、BUFFER模式和 INOUT 模式。

4.VHDL的数据对象有常量、变量和信号三种。

VHDL程序设计中常用的库有IEEE库、 STD库、WORK库和VITAL库。

5.VHDL是一种强数据类型语言,强数据类型的具体含义是:(1) 各数据对象必须具有确定的数据类型 (2)具有相同数据类型的数据对象才能进行相互操作。

6. VHDL的描述风格有三种,分别是行为描述、数据流描述和结构描述。

7.VHDL是一种强类型语言,强类型的具体含义是:(1) 要求设计实体中的每一个常数、信号、变量、函数以及设定各种参量都必须有明确的数据类型;(2) 只有数据类型相同的量才能互相传递和作用。

其设计成强数据类型语言的目的是使VHDL编译或综合工具很容易找出设计中的各种错误。

2014电子科技大学数字逻辑设计及应用期中考试试题附答案

电子科技大学2013-2014学年第二学期“数字逻辑设计及应用”课程考试题(半期)(120分钟)考试日期 2014年 月 日I. To fill the answers in the “( )” ( 2’ X 15 = 30 )1. Given ∑=ABCF )5,4,1(, then ABC F ∏=( 0,2,3,6,7 ),F =A ’∑BC( 1 )+A∑BC( 0,1 ).2. ( 1001 0011 )8421BCD =( 1111 0011 )2421BCD .3. ( 0101 1101 )2=( 0111 0011 )Gray .4. Open-drain output has two states, Low and ( Hi-Z/open ).5. A two’s -complement =0110 1010, C one ’s -complement =1111 1011, [A-C]two’s -complement =( 0110 1110 ). Is it overflow for [A-C]two’s -complement ? (Y es or No) [ No ]6. XOR gate in positive logic level is equivalent to ( XNOR ) gate in negative logic level.7. Five variables can make ( 32 ) minterms. The sum of all the minterms must be ( 1 ).8. If the function ∑=ABCF )6,3,2,1(, then ∑=ABC F '( 0, 4, 5, 7 ).9. If the information bits are 1001 0010, the check bit is ( 0 ) for odd-parity. 10. To make 2014 code-words, ( 11 ) bits should be used at least.11. Given the circuit shown in Figure 1, its output expression F=( (b(a+c)+ac)’ ).Figure 1II. There is only one correct answer in the following questions.( 3’ X 10=30 )1. Which of the following codes has the self-complement property? ( D)A. GrayB. BiquinaryC. 8421BCDD. Excess-32. Which of the following 2-input gates can form a complete set of logic gates? ( B )A. ORB. NORC. XORD. XNOR3. Which of the following gates is equivalent to XNOR? ( A)A. B. C. D.4. Which of the following connection is correct? ( C)A. B. C. D.5. Which of the following expressions has no hazard? ( B)A. F=W•Y+W’•Z’+X•Y’•ZB. F=W•Y+W’•Z’+Y•Z’C. F=W•Y+W’•Z’+X•Y’•Z+Y•Z’D. F=W•Y+W’•Z’+X•Y’•Z+W’•X•Y’6. Which of the following statements is correct? ( D)A. The duality of the minimal sum expression is its minimal product.B. The minimum sum-of-product expression has no static-1 hazard.C. The canonical sum must have hazard.D. The minimum sum-of-product expression has no static-0 hazard.7. The minimum sum of product for AB+A’C+BCDEFGH is ( A).A. A•B+A’•CB. A’•B+A•CC. A•B+A’•C+B•CD. A•B+A’•C+B•C8. Given A=(0011 1111 . 0100)2, its equivalent values for A10 and A16 are ( B)A. (96.58)10, (60.94)16B. (63.25)10, (3F.4)16C. (96.58)10, (60.49)16D. (63.25)10, (3F.94)169. Given the timing diagram as shown in Figure 2, the output function is ( A ). A. ∑=xyzf )7,6,5,3( B. ∑=xyz f )4,2,1,0( C. ∑=xyz f )6,2,1,0( D. ∑=xyz f )7,2,1,0(Figure 210. A self-dual logic function is a function such that F=F D . Which of the following functions is self-dual? ( C )A. ∑=xyzF )7,5,2,1( B. F=X ’•Y •Z ’+X •Y ’•Z ’+X ’•ZC. F=X •Y+X •Z+Y •ZD. )4,3,0(xyzF ∏=III. Combinational Circuit Analysis And Design: [40’]1.Given F(A,B,C,D)= B ⊕C ⊙(B •C)+A ’•D •(B •C)’, the constraint condition is A •(B+C)=0. Simplify the logic function F(A,B,C,D) into the minimal sum using Karnaugh map, and write out NAND-NAND logic expression of the minimal sum. (8’)参考评分标准:1.填写F 的卡诺图正确4分 ,d 占1分,错一格扣0.5分,扣完为止;2.化简的表达式正确3分,错一个乘积项扣1分;F minimal-sum (A,B,C,D)=B/C/+B/D+C/D3.“与非-与非“表达式正确1分F NAND-NAND (A,B,C,D)= [(B/C/)/(B/D)/(C/D)/]/2. A combinational circuit is shown as below. (8’)(1) Write out the sum-of-product expression of output F(W,X,Y,Z) for the circuit.(2) Analysis all conditions that the static hazard may exit for the circuit, and indicate types of static hazard.(3)Write out the minimal sum of output F(W,X,Y,Z) for the hazard-free.参考评分标准:1. 原始的积之和表达式正确3分 ,只要是积之和形式就算对,不管是否为原始积之和,错一个(多一个或少一个)乘积项扣一分,扣完为止;F(W,X,Y,Z)=WX/Y/+XY/Z+XY2.指出所有静态冒险存在的条件2分,指出静态冒险类型1分。

2014年下半年电子商务设计师考试真题(下午)

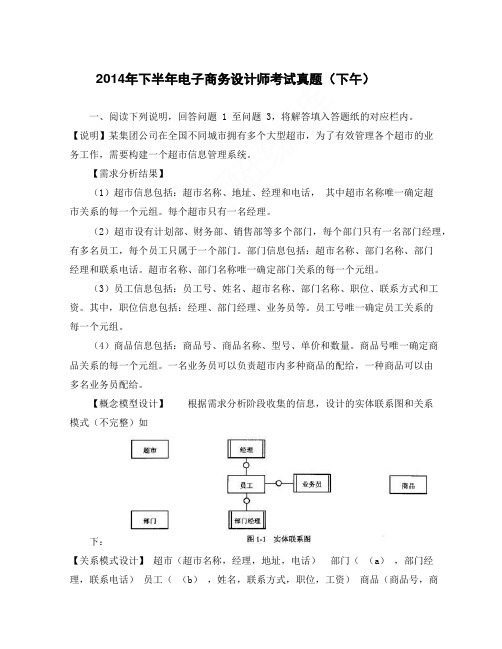

2014年下半年电子商务设计师考试真题(下午)一、阅读下列说明,回答问题 1 至问题 3,将解答填入答题纸的对应栏内。

【说明】某集团公司在全国不同城市拥有多个大型超市,为了有效管理各个超市的业务工作,需要构建一个超市信息管理系统。

【需求分析结果】(1)超市信息包括:超市名称、地址、经理和电话,其中超市名称唯一确定超市关系的每一个元组。

每个超市只有一名经理。

(2)超市设有计划部、财务部、销售部等多个部门,每个部门只有一名部门经理,有多名员工,每个员工只属于一个部门。

部门信息包括:超市名称、部门名称、部门经理和联系电话。

超市名称、部门名称唯一确定部门关系的每一个元组。

(3)员工信息包括:员工号、姓名、超市名称、部门名称、职位、联系方式和工资。

其中,职位信息包括:经理、部门经理、业务员等。

员工号唯一确定员工关系的每一个元组。

(4)商品信息包括:商品号、商品名称、型号、单价和数量。

商品号唯一确定商品关系的每一个元组。

一名业务员可以负责超市内多种商品的配给,一种商品可以由多名业务员配给。

【概念模型设计】根据需求分析阶段收集的信息,设计的实体联系图和关系模式(不完整)如下:【关系模式设计】超市(超市名称,经理,地址,电话)部门((a),部门经理,联系电话)员工((b),姓名,联系方式,职位,工资)商品(商品号,商品名称,型号,单价,数量)配给((c),配给时间,配给数量,业务员)【问题 1】(4 分)根据问题描述,补充四个联系,完善图 1-1 的实体联系图。

联系名可用联系 1、联系2、联系 3 和联系 4 代替,联系的类型分为 1:1、1:n 和 m:n(或 1:1、1:*和*:*)。

【问题 2】(7 分)(1)根据实体联系图,将关系模式中的空(a)~(c)补充完整;(2)给出部门和配给关系模式的主键和外键。

【问题 3】(4 分)(1)超市关系的地址可以进一步分为邮编、省、市、街道,那么该属性是属于简单属性还是复合属性?请用 1 00 字以内文字说明。

2014年系统架构设计师考试真题及答案

等价的 SQL 语句为:SELECT () FROM R,

A.A,R.C,E,F B.A,C,S.B,S.E C.A,C,S.B,S.C D.R.A,R.C,S.B,S.C

A.R.B=S.B AND R.C=S.C AND RC<S.B B.R.B=S.B AND R.C=S.C AND R.C<S.F C.R.B=S.B OR R.C=S.C OR R.C<S.B D.R.B=S.B OR R.C=S.C OR R.C<S.F

A.I2、C2、C4 B.I2、I3、C2 C.C2、P3、C4 D.C2、P3、P4

A.C2、C4、P4 B.I2、I3、C4 C.I3、P3、P4 D.C4、P3、P4

2.某文件系统文件存储采用文件索引节点法。假设磁盘索引块和磁盘数据块大小均为 1KB,每 个文件的索引节点中有 8 个地址项 iaddr[0]~iaddr[7],每个地址项大小为 4 字节,其中 iaddr[0]~ iaddr[5]为直接地址索引,iaddr[6]是一级间接地址索引,iaddr[7]是二级间接地址索引。如果要访 问 icwutil.dll 文件的逻辑块号分别为 0、260 和 518,则系统应分别采用()。该文件系统可表示 的单个文件最大长度是()KB。

10.结构化布线系统分为六个子系统,其中水平子系统()。 A.由各种交叉连接设备以及集线器和交换机等设备组成 B.连接了干线子系统和工作区子系统, C.由终端设备到信息插座的整个区域组成 D.实现各楼层设备间子系统之间的互连

11.在实际应用中,用户通常依靠评价程序来测试系统的性能。以下评价程序中,()的评测准 确程度最低。事务处理性台昱委员会(Transaction Processing Performance Council, TPC)是制定商 务应用基准程序(benchmark)标准规范、性能和价格度量,并管理测试结果发布的非营利组织, 其发布的 TPC-C 是()的基准程序。

EDA技术(VHDL)试卷及答案

班级 学号 姓名密 封 线 内 不 得 答 题一、单项选择题(30分)1.以下描述错误的是 CA .QuartusII 是Altera 提供的FPGA/CPLD 集成开发环境B .Altera 是世界上最大的可编程逻辑器件供应商之一C .MAX+plusII 是Altera 前一代FPGA/CPLD 集成开发环境QuartusII 的更新换代新产品D .QuartusII 完全支持VHDL 、Verilog 的设计流程2.以下工具中属于FPGA/CPLD 开发工具中的专用综合器的是 BA .ModelSimB .Leonardo SpectrumC .Active HDLD .QuartusII 3.以下器件中属于Xilinx 公司生产的是 CA .ispLSI 系列器件B .MAX 系列器件C .XC9500系列器件D .FLEX 系列器件 4.以下关于信号和变量的描述中错误的是 BA .信号是描述硬件系统的基本数据对象,它的性质类似于连接线B .信号的定义范围是结构体、进程 //在整个结构体的任何地方都能使用C .除了没有方向说明以外,信号与实体的端口概念是一致的D .在进程中不能将变量列入敏感信号列表中 5.以下关于状态机的描述中正确的是 BA .Moore 型状态机其输出是当前状态和所有输入的函数//Mealy 型状态机其输出信号是当前状态和当前输入的函数B .与Moore 型状态机相比,Mealy 型的输出变化要领先一个时钟周期C .Mealy 型状态机其输出是当前状态的函数D .以上都不对6.下列标识符中, B 是不合法的标识符。

A .PP0B .ENDC .Not_AckD .sig7.大规模可编程器件主要有FPGA 、CPLD 两类,下列对CPLD 结构与工作原理的描述中,正确的是 C 。

A//.FPGA 即是现场可编程逻辑器件的英文简称CPLD 复杂可编程逻辑器件 B .CPLD 是基于查找表结构的可编程逻辑器件 C .早期的CPLD 是从GAL 的结构扩展而来D .在Altera 公司生产的器件中,FLEX10K 系列属CPLD 结构 8.综合是EDA 设计流程的关键步骤,在下面对综合的描述中, D 是错误的.A .综合就是把抽象设计层次中的一种表示转化成另一种表示的过程B .综合就是将电路的高级语言转化成低级的,可与FPGA / CPLD 的基本结构相映射的网表文件C .为实现系统的速度、面积、性能的要求,需要对综合加以约束,称为综合约束D .综合可理解为,将软件描述与给定的硬件结构用电路网表文件表示的映射过程,并且这种映射关系是唯一的(即综合结果是唯一的)9.嵌套使用IF 语句,其综合结果可实现 A .A .带优先级且条件相与的逻辑电路B .条件相或的逻辑电路C .三态控制电路D .双向控制电路 10.在VHDL 语言中,下列对时钟边沿检测描述中,错误的是 D 。

2014电子设计大赛选拔考试电路设计题目

一、任务

设计并制作一个额定输出功率为16W 的8V DC/DC供电电源,已知额定输入电压为24V。

二、要求

1. 基本要求

( 1 )调整负载电阻至额定输出功率工作状态,供电系统的直流输出电压U O =8.0 ± 0.4V 。

( 2 )额定输出功率工作状态下,供电系统的效率不低于60% 。

( 3 )调整负载电阻(4欧姆~20欧姆),保持输出电压U O =8.0 ± 0.4V。

( 4 )调整输入电压(10V~30V),保持输出电压U O =8.0 ± 0.4V。

( 5 )具有显示输出、输入电压、电流、功率、系统效率的功能。

2. 发挥部分

( 1 )额定输出功率工作状态下,进一步提高供电系统效率。

( 2 )具有负载短路保护及自动恢复功能,保护阈值电流为 4.5A (调试时允许有± 0.2A 的偏差)。

( 3 )能正确显示系统输出、输入电压、电流、功率、系统效率。

(4 )具有键盘调节输入电压的功能,额定输入时,输出电压可设定为(6V~20V),单步调压1V。

EDA设计试题

a) Nop-flipped and separated rowsb)Flipped and abutted rowsc) Flipped and separated rowsd) Non-flipped and abutted rows22,Refer to layout A & B,which of the following is true:A:W/L=2/ B:W/L=4/a) B has the same area as A and double the drive.b) B has double the area of A and half the drive.c) B has the same area as A and the same drive.d) B has 4X the area as A and the same drive.e) B has 4X the drive as A and the same area.23,which is correcta)Slack=Data arrival time -Data Required timeb) Slack=Data Required time -Data arrival timec) Slack=Clock Arrival time -Data arrival timed) Slack=Clock Required time -Data Required time24,In the following figure, what is the total number of possible data arrival times for setupa) 1b)2c) 3d) 425,Which will always result in the worst slack for setup timea) The longest data arrival time.b) The shortest data arrival time.c)It is unclear as the slack is a function of data arrival time as well as data required time.26,n-device is faster than p-device because Reduce Areaa) Hole mobility is greater than electron mobility.b)Electron mobility is greater than hole mobility.c) The P threshold is greater than N threshold.d) The N threshold is greater than P threshold.e) None of the above.27,For a 25 MHz processor, what is the time taken by the instruction which needs 3 clock cyclea) 120 nano secsb) 120 micro secsc) 75 nano secsd)75 micro secs28,Which one is correct statementa) RTL models can be simulated only on cycle based simulatorb)Event driven simulators can simulate both synchronous and asynchronous designsc) Multi clock designs can not be simulated with Event driven simulatorsd) b and c29,Formal analysis means:a) Verifying designs with assertions using simulatorsb)Verifying designs only with assertions staticallyc) Analyzing functional coverage generated from the assertion IPsd) a and c30,Which language supports object oriented programming and good for RTL verificationa) C++b) Verilog with VPIc)System Verilogd) b and cis the difference between logic and bit types (1%)a) logic is 2 state, bit is 4 stateb) There is no differencec) logic is 4 state, bit is 2 stated) none of the abovedo you specify signal direction in a SystemVerilog interface (1%)a) through clocking blocksb) Through cross module referencec) Through modportsd) None of the abovedo I create a variable shared by all objects of a class, but not make a global (1%)a) declare it as automaticb) declare it in the top scopec) declare it as sharedd) declare it as staticdo I share code between classes (1%)a) Instantiate a class within another classb) Inherit from one class to another (inheritance/derivation)c) all of the aboved) None of the aboveis the final value of and in this code (1%)class Thing;int data;endclassThing t1, t2;initial begint1 = new();= 1;= 2;t2 = t1;= 5;enda) = 5, = 5b) t2 gets used before new() is called. Null object access!c) = 5, =2;d) None of the above36. Write a constraint for the variable Q that picks a value of 0, for 75% of the time and 1~3 for the rest (1%)a)constraint c {Q dist {0 := 75, [1:3] := 25} ; }b) constraint c { Q < 4; Q >= 0; }c) constraint c { Q < 4; Q >= 0; Q%2 dist {0 := 75, 1:= 25}; }d) constraint c { Q < 4; Q >= 0; Q%3 dist {0 := 25, 1:= 25, 2:=25, 3:= 75 }; }37. What are the possible values that x and y will take when the following class is randomized (1%)class E;rand bit [15:0] x[10], y[10];constraint size_cons {foreach (x[i]){x[i] > 0; x[i] < y[i];foreach (y[i])y[i] inside {[1:9]};}}endclassa} x in [0,9], y in [0,9]b) x in [1,9], y in [1,9]c) x in [1,9], y in [2,10]d) x in [1,8], y in [2,9]38. What is the final value of and in this code %)class Thing;int data;endclassThing t1, t2;initial begint1 = new();= 1;= 2;t2 = t1;= 5;enda) = 5, = 5b) t2 gets used before new() is called.Null object access!c) = 5, =2;d) None of the above39. The new intern Smart Assert can not write simple assertions. He wrote:( a ##1 (!b[*0:$] ##1 b)[*3:5] ## 1C )While the assertion works correctly, can you help him write it in a simplified form Please choose one correct answer from A), B), C) and D): %)A)property abc_sequence_with_!b_random_space_between;@(posedge clk) $rose(a)##1 b|-> b[*3:5] ##1c;endproperty: abc_sequence_with_!b_random_space_between;B)property abc_sequence_with_!b_random_space_between;@(posedge clk) a##1 b[=3:5] ##1 c;endproperty: abc_sequence_with_!b_random_space_between;C)property abc_sequence_with_!b_random_space_between;@(posedge clk) a##1 !b[*0:$] ##1 b[*3:5] ##1 c;endproperty: abc_sequence_with_!b_random_space_between;D)property abc_sequence_with_!b_random_space_between;@(posedge clk) a##1 b[->3:5] ##1 c;endproperty: acb_sequence_with_!b_random_space_between;40.Consider a bus protocol that includes the property “a new bus cycle may not start for 2 clock cycles after an abort cycle occurs.” This property could be coded as below. Please choose one correct answer from A), B), C) and D). %)A)property wait_after_abort;@(posedge clk) wait(abort_cycle)##2 !cycle_start;endproperty: wait_after_abort ;B)property wait_after_abort;@(posedge clk) while (abort_cycle) ##2 Not(cycle_start) ;endproperty: wait_after_abortC)property wait_after_abort;@(posedge clk) abort_cycle |=> !cycle_start[*2]; endproperty: wait_after_abortD )property wait_after_abort;@(posedge clk) abort_cycle |-> Not(##2 cycle_start); endproperty: wait_after_abort41. 考虑以下两个逻辑表达式 f 和 g,Consider the following logic expressions for f and g :ƒx 1x 2x3xx 1x 2x 1x 3xx 1 x 3x 4x x 1x名,否则不给分数。

EDA技术EDA技术试卷(练习题库)(2023版)

EDA技术EDA技术试卷(练习题库)1、个项目的输入输出端口是定义在()。

2、描述项目具有逻辑功能的是()。

3、关键字ARCHITECTURE定义的是。

4、 MAXPLUSII中编译VHDL源程序时要求()。

5、 1987标准的VHDL语言对大小写是()。

6、关于1987标准的VHDL语言中,标识符描述正确的是()。

7、符合1987VHDL标准的标识符是()。

8、 VHDL语言中变量定义的位置是()。

9、 VHDL语言中信号定义的位置是()。

10、变量是局部量可以写在()。

11、变量和信号的描述正确的是()。

12、关于VHDL数据类型,正确的是()。

13、下面数据中属于实数的是()。

14、下面数据中属于位矢量的是()。

15、可以不必声明而直接引用的数据类型是()。

16、 STD_LOGIG_1164中定义的高阻是字符()。

17、 STD_LOGIG_1164中字符H定义的是()。

18、使用STD_LOGIG_1164使用的数据类型时()。

19、 VHDL运算符优先级的说法正确的是()。

20、如果a=1,b=0,则逻辑表达式(aANDb)OR(NOTbANDa)的值是()。

21、不属于顺序语句的是()。

22、正确给变量X赋值的语句是()。

23、 EDA的中文含义是()。

24、 EPF10K20TC144-4具有多少个管脚()。

25、如果a=1,b=1,则逻辑表达式(aXORb)OR(NOTbANDa)的值是()。

26、 MAX+PLUSII的,数据类型为std_logic_vector,试指出下面那个30、在一个VHDL,数据类型为integer,数据范围0to127,下面哪个赋31、下列那个流程是正确的基于EDA软件的FPGA/CPLD和变量的说法,哪一个是不正确的:()。

33、下列语句中,不属于并行语句的是:()。

34、()在EDA工具中,能将硬件描述语言转换为硬件电路的重要工具软件称为。

35、不是操作符号它只相当与作用" target="_blank">在VHDL的CASE语句中,条件句中的“=>”不是操作符号,它只相当与()作用。

2014湖北省电子设计竞赛E题

x[n] n 1, 2,, N ,计算其均值 m

N n 1

x[n] / N ,则方差 2 为:

Байду номын сангаас

2

N n 1

x[n] m / N 。

2

共 3 页,E-3

2014 年 TI 杯大学生电子设计竞赛 E 题:∑-Δ 型 A/D 转换电路 1.任务

设计并制作 1 阶∑-Δ 调制器,并在此基础上设计并制作∑-Δ 型 A/D 转换电路,电路 结构如图 1 所示。

图 1 ∑-Δ 型 A/D 转换电路框图

2.要求

(1)设计并制作 1 阶∑-Δ 调制器,具体电路框图如图 2 所示。图中 U REF 为 2V。要 求∑-Δ 调制器输出的 1 位数据流为 TTL 电平,时钟频率 f CLK 自定。 (12 分) (2)利用(1)中制作的 1 阶∑-Δ 调制器,设计并制作∑-Δ 型 A/D 转换电路。要求 A/D 转换电路可设置工作于下列两种模式: 模式 1,采样频率为 100Hz,采样位数为 12 位; 模式 2,采样频率为 1600Hz,采样位数为 8 位。 (32 分)

1阶∑-Δ调制器中各点信号的波形示意

(2) 要求(3)设计并制作采样数据显示装置,可以使用自制的液晶显示;也可 以借助外部显示设备,如示波器。但必须能显示∑-Δ 型A/D转换电路输出的连续采样数 据,并能显示采样信号的波形。 (3) 采样数据的方差 2 计算:将∑-Δ 型A/D转换电路输出的一组采样数据,记为

(3)设计并制作∑-Δ 型 A/D 转换电路的采样数据显示装置。要求可以显示 A/D 转 换电路连续采样数据波形,显示的波形数据点数不少于 200 点。同时,在波 形上显示一个光标,移动光标时能显示相应波形点的采样数据。 (6 分) (4)改进∑-Δ 型 A/D 转换电路的显示装置,要求能计算 A/D 转换电路输出的采样 数据的方差 2 , 并实时显示。 方差的计算使用连续 1 秒的采样数据直接计算。 (10 分) (5)改进∑-Δ 型 A/D 转换电路的设计,尽量减小 A/D 转换电路的本底噪声和量化 噪声, 提高∑-Δ 型 A/D 转换电路的采样精度。 实现∑-Δ 型 A/D 转换电路能工 作于下列模式: (20 分) 模式 3,采样频率为 100Hz,采样位数为 16 位,有效位数不少于 13 位。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

第 1 页 共 2 页

广东海洋大学 2013 —— 2014 学年第 2 学期

《EDA(电子设计自动化)》考试设计题

课程号:

□ 考试 □ A卷 □ 闭卷

√ 考查 □ B卷 √ 上机

题 号 一 二 三 四 五 六 七 八 九 十 总分 阅卷教师

各题分数 5 10 10 10 10 10 20 20 5 100

实得分数

注:开放式环境下独立完成;设计电子文档与纸质卷上交的时间为

2014/6/20/AM 12:00前;所有的答案以打印的方式写在答题纸上;

一、 填空题(5分)

请将本人考试设计题目填于此 办公楼防盗报警器 ,本设计共设计

了 个电路子模块,分别为:模块一 ,模块

二 ,模块三 ,

模块四 ,模块五 ,…;

二、电路模块一设计说明(10分)

1、按照实际设计,画出本模块的示意图并详细标注出各个端口

;

2、说明本模块所完成的功能;

3、介绍本模块内最重要的一个进程或子程序的作用;

4、将本模块的程序及注释打印在本区域内;

5、做了仿真的,将本模块的仿真波形截图黏贴在本说明段内;

三、电路模块二设计说明(10分)

1、按照实际设计,画出本模块的示意图并详细标注出各个端口

;

2、说明本模块所完成的功能;

3、介绍本模块内最重要的一个进程或子程序的作用;

4、将本模块的程序及注释打印在本区域内;

5、做了仿真的,将本模块的仿真波形截图黏贴在本说明段内;

四、电路模块三设计说明(10分)

1、按照实际设计,画出本模块的示意图并详细标注出各个端口

;

2、说明本模块所完成的功能;

3、介绍本模块内最重要的一个进程或子程序的作用;

4、将本模块的程序及注释打印在本区域内;

5、做了仿真的,将本模块的仿真波形截图黏贴在本说明段内;

班

级

:

姓

名

:

学

号

:

试

题

共

3

页

加

白

纸

2

张

密

封

线

GDOU-B-11-302

第 2 页 共 2 页

五、电路模块四设计说明(10分)

1、按照实际设计,画出本模块的示意图并详细标注出各个端口

;

2、说明本模块所完成的功能;

3、介绍本模块内最重要的一个进程或子程序的作用;

4、将本模块的程序及注释打印在本区域内;

5、做了仿真的,将本模块的仿真波形截图黏贴在本说明段内;

六、电路模块五设计说明(10分)

1、按照实际设计,画出本模块的示意图并详细标注出各个端口

;

2、说明本模块所完成的功能;

3、介绍本模块内最重要的一个进程或子程序的作用;

4、将本模块的程序及注释打印在本区域内;

5、做了仿真的,将本模块的仿真波形截图黏贴在本说明段内;

…

七、电路顶层模块设计说明(或总设计说明)(20分)

1、按照实际设计,画出顶层模块内各个子模块之间的连接关系;

2、说明顶层模块所完成的功能;

3、介绍顶层模块内最重要的一个进程或子程序的作用;

4、将顶层模块的程序及注释打印在本区域内;

5、做了仿真的,将顶层模块的仿真波形截图黏贴在本说明段内;

八、实物或开发板演示(20分)

1、做了实物的,或将程序下载到开发板验证了功能的,可当场演示;

2、将相关的演示照片黏贴在本说明段内;

九、发表考试设计完成后的感想(5分)

1、可以写下自己在设计中的一些感想;

2、可以提出自己对进一步改进本课程教学方面和学习方面等的一些合理

建议;