数字电路第五版 第八章

合集下载

数字集成电路第8章

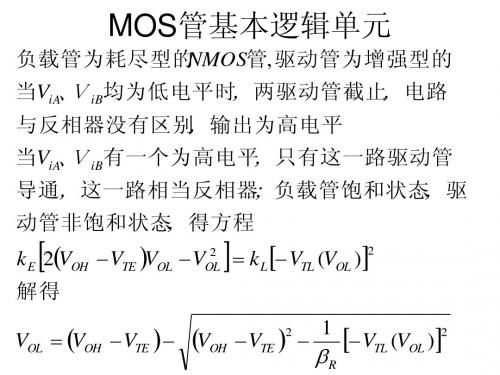

最坏情况, 只有一个驱动管导通时 的VoL 值, 对于给定

2 Gon Ron

2 VOL I D kE VOH VTE VOL 2 I D / VOL k E VOH VTE VOL

Gon k A VOH VTE VOL k B VOH VTE VOL

改进多米诺CMOS逻辑

• 省掉多米诺缓冲器,级联的各逻辑块交替地 由P型管和N型管构成 • 当¢=0,第一级预充到高电平(NMOS管逻辑), 第二级预充到低电平,第三级预充到高电平. • 由于第二级由PMOS管构成,在预充电期间, PMOS管都处于截止状态. • 由于第二级预充到低电平,第三级NMOS管也 都处于截止状态. • 因此可以进行多米诺连接

A B R L L

2VTL (VOL )

2 2 OL

VOH

VTD VOL

V 2

NMOS与非门

R 相当倒相器的两倍 , 要得到相同的

VOL 与非门每个驱动门所占 芯片面积相 当倒相器的两倍 ; 两个驱动管相串联 , 导通时等效电阻等于两 者之和 RON RONA RONB RON 2 RONA 2 RONB

NMOS与非门输出电容

VB VOH VB 0 或 V A VOH V A VOH COUT CGDA CGSA CGDB CGDL C LINE CG k (VOH , VOL )(C DBA C SBA C DBB C SBL ) V A 0 VB 0 或 VB VOH V A 0 COUT CGDA CGDL C LINE CG k (VOH , VOL )(C DBA C SBL )

数字电路逻辑设计第八章PLD可编程逻辑器件PLD

33 33 3

第八章 可编程逻辑器件PLD

厂商直接做出。

简如:介表芯

ASIC

全定制厂(商F做ull出C半us成tom品Design IC) 半定制(Semi-Custom Design IC)

半定制

标准单元(Standard Cell Array 简称SCA) 门阵列(Gate Array简称GA ) 可编程逻辑器件(Programmable Logic Device)

特别是一些较高级的软件平台,一个系统除了方案设 计和输入电路外,其它功能都可用编程软件自动完成。 可编程逻辑器设件计设人计员电完路成过程如下图所示:

电

设

优

选

器时

路方

计

化

择

编

件序

设案

输

电

器

程

功检

计

入

路

件

能查

220022220000//22110022////11332200//3300

h

11991199 19

h

22 22 2

第八章 可编程逻辑器件PLD 简介

传统的逻辑系统:当规模增大时

焊点多,可靠性下降; 系统规模增加,成本升高; 功耗增加; 占用空间扩大。

系统放在一个芯片内

专用集成电路(简称ASIC)

用户定制 集成电路

220022220000//22110022////11332200//3300

h

与阵列固定

与 门 阵 列

或阵列可编程

Y

Z

输出

输入

PLA B

A

与阵列可编程

与 门 阵 列

或阵列可编程

220022220000//22110022////11332200//3300

数电第8章

数字电路逻辑设计 7

系统具有加密功能:多数PLD器件,如GAL 或高密度可编程逻辑器件,本身具有加密功 能。设计者在设计时选中加密项,可编程逻 辑器件就被加密。器件的逻辑功能无法被读 出,有效地防止电路被抄袭。

2018/11/11

数字电路逻辑设计

8

8.2 可编程逻辑器件PLD概述

PLD是70年代发展起来的新型逻辑器件,相继出现 了ROM 、 FPLA、PAL 、GAL、EPLD和FPGA及 由输入缓冲器构成,产生输 由或门阵列构成,将与阵列输出的乘积项有 由与门阵列构成,产生输 由三态门寄存器构成,产生 isp等。前四种属于低密度 PLD,后三种属高密度 入变量的原变量和反变量 选择的进行或运算,形成与或式,实现函数 入变量的与项(乘积项) 输出信号,提供反馈信号 PLD。 PLD的基本结构

数字电路逻辑设计 13

2018/11/11

80年代中期的PLD:通用阵列逻辑(GAL)器件问世 ,并取代了PAL。GAL器件是在PAL器件基础上发 展起来的新一代器件。和PAL一样,它的与门阵列 是可编程的,或门阵列是固定的。但由于采用了高 速电可擦CMOS工艺,可以反复擦除和改写,很适 宜于样机的研制。它具有CMOS低功耗特性,且速 度可以与TTL可编程器件相比。特别是在结构上采 用了“输出逻辑宏单元”电路,为用户提供了逻辑 设计和使用上的较大灵活性。

通用集成电路:集成电路是指常用的中、小规模数 字电路(如74系列、4000系列等),其逻辑功能设 计以实现数字系统的基本功能块为目的,一般比较 简单,并且固定不变。 优点:通用性强,使用方便灵活。 缺点:体积、功耗和重量较大,可靠性和可维护性 较差等。

数字电子技术基础 2

2018/11/11

专用型集成电路(ASIC)

系统具有加密功能:多数PLD器件,如GAL 或高密度可编程逻辑器件,本身具有加密功 能。设计者在设计时选中加密项,可编程逻 辑器件就被加密。器件的逻辑功能无法被读 出,有效地防止电路被抄袭。

2018/11/11

数字电路逻辑设计

8

8.2 可编程逻辑器件PLD概述

PLD是70年代发展起来的新型逻辑器件,相继出现 了ROM 、 FPLA、PAL 、GAL、EPLD和FPGA及 由输入缓冲器构成,产生输 由或门阵列构成,将与阵列输出的乘积项有 由与门阵列构成,产生输 由三态门寄存器构成,产生 isp等。前四种属于低密度 PLD,后三种属高密度 入变量的原变量和反变量 选择的进行或运算,形成与或式,实现函数 入变量的与项(乘积项) 输出信号,提供反馈信号 PLD。 PLD的基本结构

数字电路逻辑设计 13

2018/11/11

80年代中期的PLD:通用阵列逻辑(GAL)器件问世 ,并取代了PAL。GAL器件是在PAL器件基础上发 展起来的新一代器件。和PAL一样,它的与门阵列 是可编程的,或门阵列是固定的。但由于采用了高 速电可擦CMOS工艺,可以反复擦除和改写,很适 宜于样机的研制。它具有CMOS低功耗特性,且速 度可以与TTL可编程器件相比。特别是在结构上采 用了“输出逻辑宏单元”电路,为用户提供了逻辑 设计和使用上的较大灵活性。

通用集成电路:集成电路是指常用的中、小规模数 字电路(如74系列、4000系列等),其逻辑功能设 计以实现数字系统的基本功能块为目的,一般比较 简单,并且固定不变。 优点:通用性强,使用方便灵活。 缺点:体积、功耗和重量较大,可靠性和可维护性 较差等。

数字电子技术基础 2

2018/11/11

专用型集成电路(ASIC)

《数字电子技术》课件——第八章 数模和模数转换

d2

22

d1 21

d0

20

)

VREF 24

D

8.2.2 倒T形电阻网络D/A转换器

VO

Ri

R VREF R

1 24

(d3 23

d2 22

d1 21

d0 20 )

VREF 24

D

对n位输入时,应有

VO

Ri

R VREF R

1 2n

(dn1 2n1

dn2 2n2

d1 21

d0 20 )

VREF 2n

第6页

8.2

8.2.1 权电阻网络D/A转换器 8.2.2 倒T形电阻网络D/A转换器

8.2.1 权电阻网络D/A转换器

求和放大器 权电阻网络

模拟开关

权电流:Ii VREF Ri I0 VREF 23 R I1 VREF 22 R I2 VREF 21 R I3 VREF 20 R

第7页

S3 ~ S0受数字d3 ~ d0控制

di 0时,Ii 0

di

1时,I

流向

i

点

8.2.1 权电阻网络D/A转换器

权电阻网络D/A转ቤተ መጻሕፍቲ ባይዱ器的优缺点:

• 1. 优点:简单 • 2. 缺点:电阻值相差大,

难于保证精度,且大电 阻不宜于集成在IC内部

输出电压:VO RF i

RF ( I3 I2 I1 I0 )

RF

R 2

RF

(VREF R

d3

VREF 2R

d2

VREF 22 R

d1

VREF 23 R

d0 )

VREF 24

(23 d3

22d2

21d1 20 d0 )

数字电路逻辑设计 第8章2 复杂可编程逻辑器件CPLDPPT资料60页

SRAM

XC7354

-(3)

54

54

108

EPROM

(1)有576个逻辑单元;(2)有1 024个可编程逻辑模块;(3)等效6个PAL22V10

CPLD的结构

逻辑块

逻辑块

可

编

逻辑块

程

逻辑块

内

部

I/O

连

I/O

逻辑块

线

逻辑块

矩

阵

逻辑块

逻辑块

CPLD的 逻辑块结构

内部 的可 编程 PI 连线 区

乘积项 阵列

8.3.1 概 述

表8-3-1 部分CPLD产品

器件名称 集成规模/门 I/O端数 宏单元数 触发器数

编程

EPM9560

12 000

216

560

772

EEPROM

EPM5032

600

24

32

32

EPROM

EPF10K10

10 000

134

-(1)

720

SRAM

EPX8160

3 200

172

160

160

8.3 复杂可编程逻辑器件(CPLD)

Complex Programmable Logic Device

8.3.1 概 述 8.3.2 CPLD的基本结构 8.3.3 CPLD的分区阵列结构 8.3.4 典型器件及应用举例

SPLD的阵列容量较小,不适合于实现规 模较大的设计对象。

SPLD片内触发器资源不足。不能适用于 规模较大的时序电路。

&

&

至n-1

& ≥1 宏单

& &